Изобретение относится к вычислительной технике и может быть использовано при проектировании ЭВМ и мультипроцессорных вычислительных систем.

Известны устройства дла вычислительной системы, содержащие блок синхронизации и группу каналов, каждый из которых включает приемный и передающий регистры, регистр адреса, управляющий регистр, буферный регистр, расп| еделитель импульсов, узел синхронизации, блок управления, узел .коммугацки управляющих сигналов и элемент ИЛИ 1J.

Недостаток этих устройств состоит а низкой пропускной способности.

Наиболее близко по технической сущности к предлагаемому устройство свяки для вычислительной системы, содержащге блок синхронизгщии и М блоков сопряжения, каждый из KOTOIMJX включает передающий и приемный регистры, распределитель импульсов, управляющий регистр, узел синхронизации, узел ком тации управляющих сигналов, схему сравнения, регистр адреса, первый, второй и третий буферные регистры, коммутатор информёщии, регистр состояние и элемент ИЛИ, причем выход передающего регистра К-го блока сопряжеВИЯ ( ,Й) соединен с информационным входом приемного регистра (К+1)го блока сопряжения, выход передающего регистра М-го блока сопряжения соединен с информационным входом приемного регистра первого блока сопряжения, а в каждом блоке сопряжения выход приемного регистра подключен к первому входу элемента ИЛИ, второй

10 вход которого соединен с выходом первого буферного регистра, а выход с информационным входом передающего регистра, выход которого подключен к первому входу схемы сравнения, пер15вый управляющий вход - с первым выходом блока синхронизации, а второй управляющий вход - с первым выходом узла коивлутации управляющих сигналов, второй выход которого подключен к

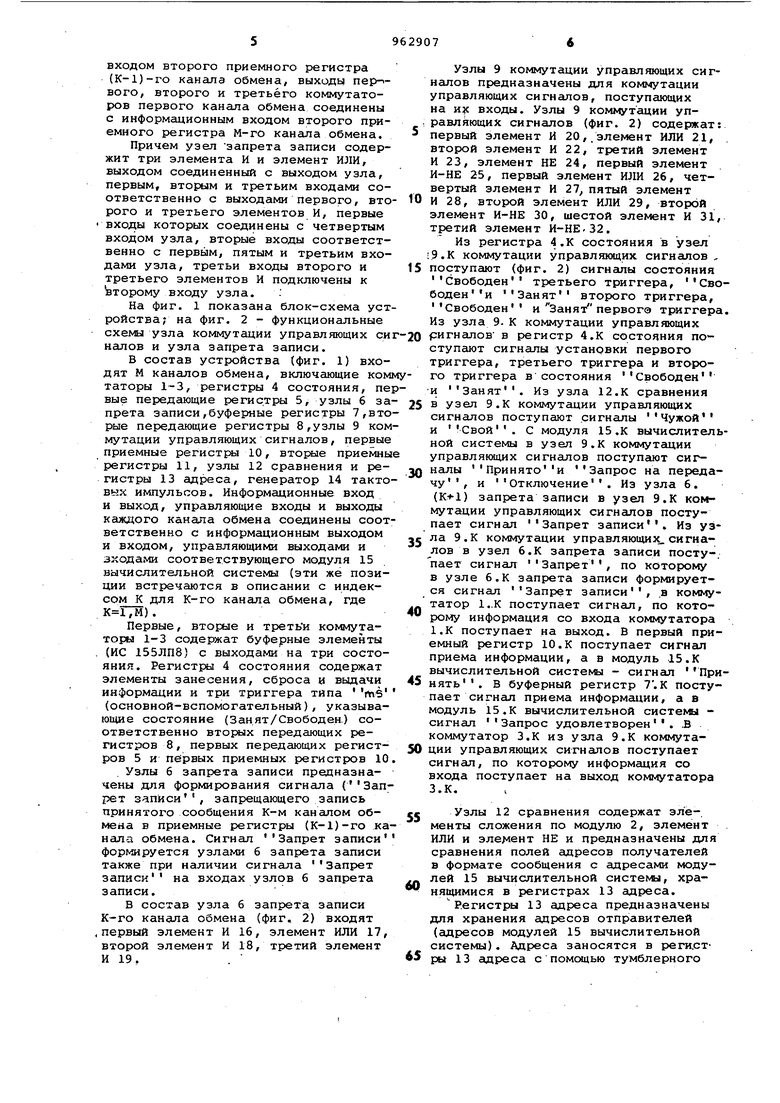

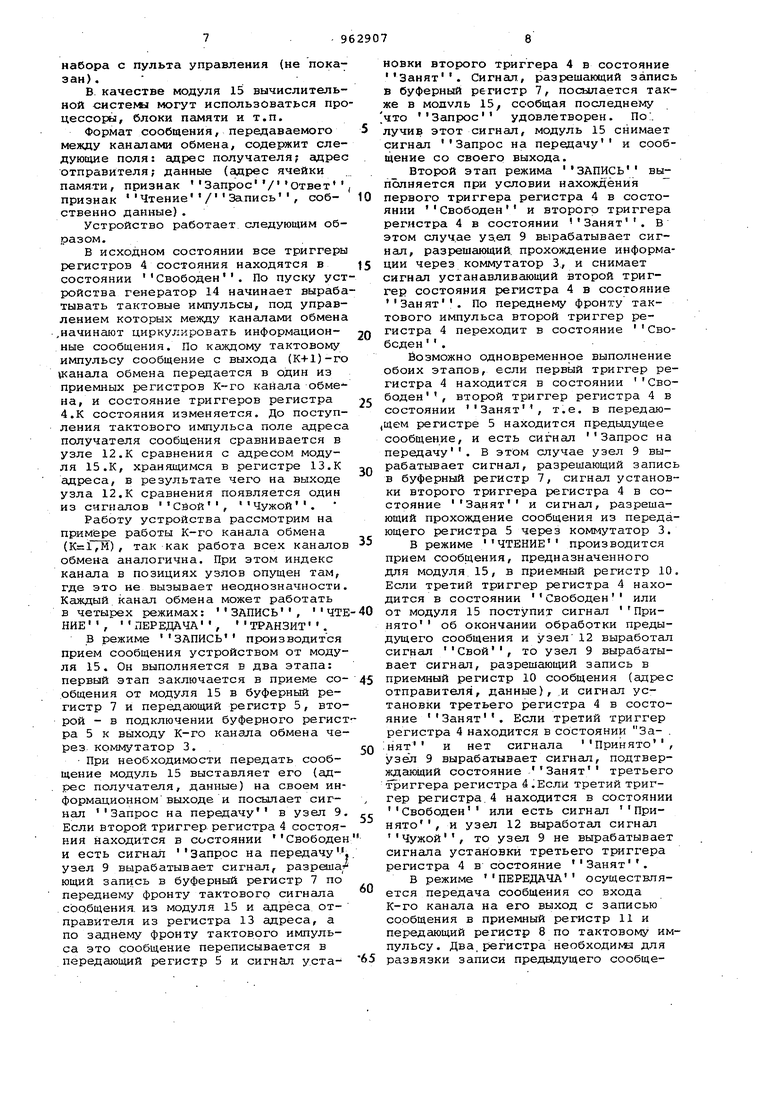

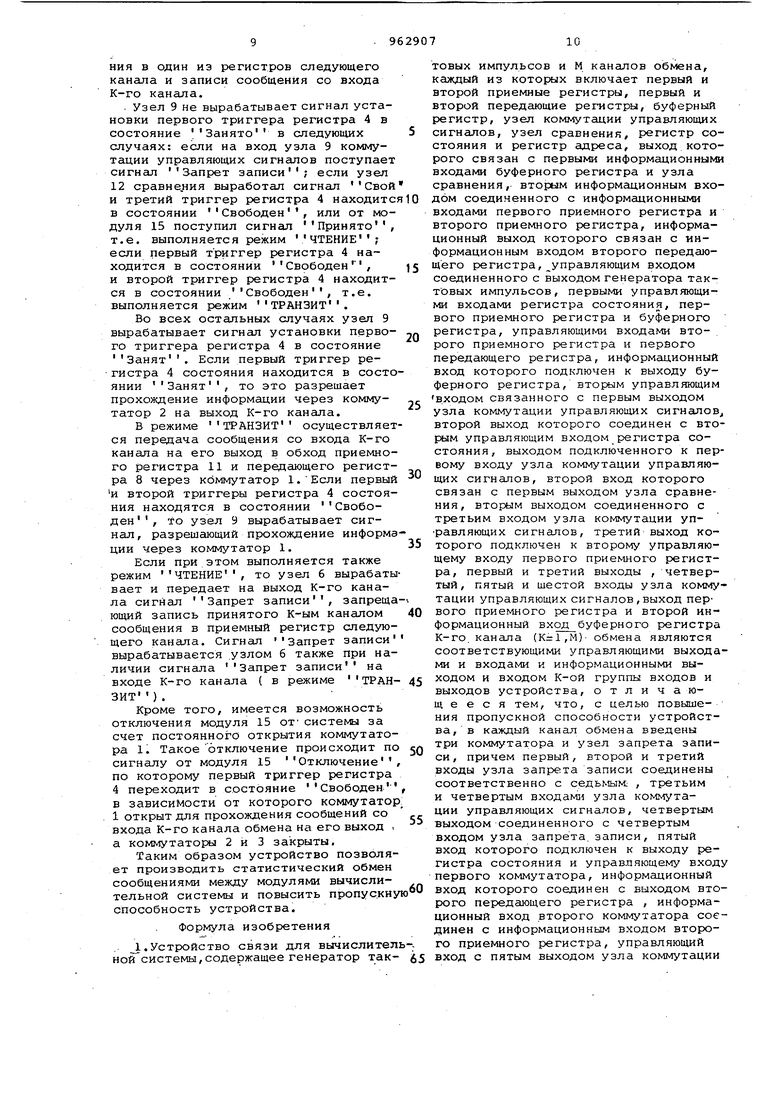

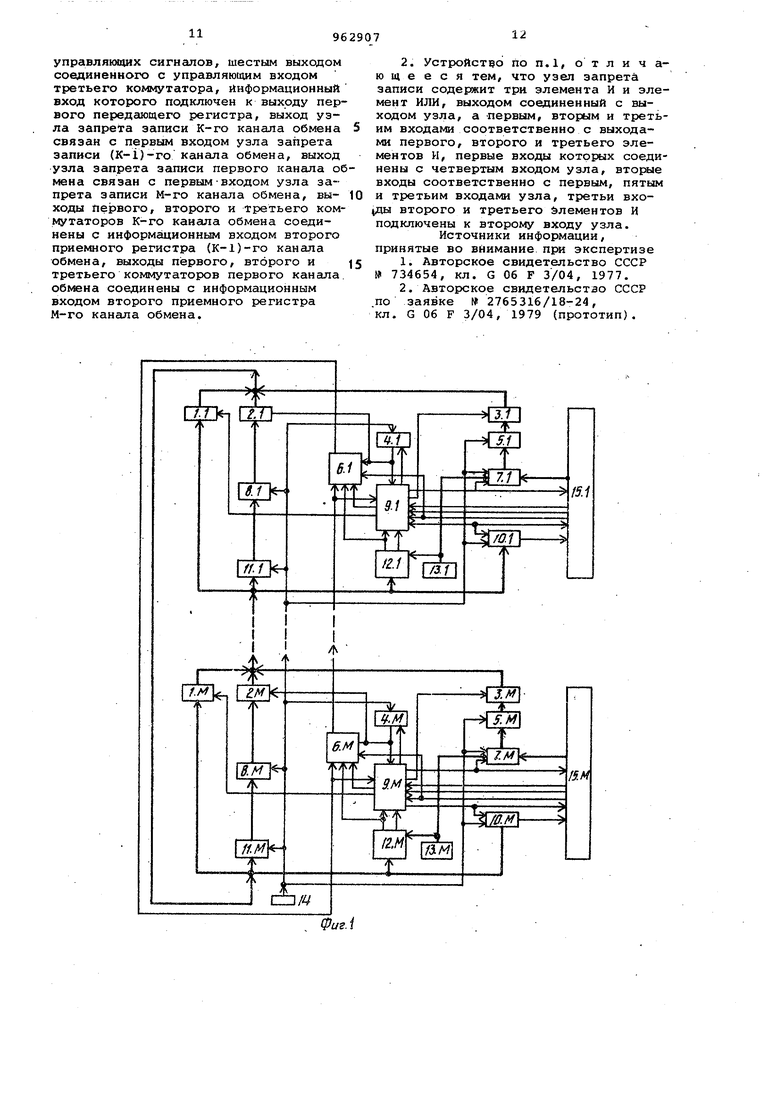

20 управляк ему входу первого буферного регистра, первый и второй входы соответственно к выходам распределителя импульсов и узла синхронизации, а первый и второй входы-выходы - со25ответственно .к выходам-входам схемы сравнения и управляющего регистра,вы.ход регистра адреса соединен с вторым входом схемы сравнения и первым информационным входом первого буФ сно30го регистра, вход распределитепя импульсов подключен к управляющим вхо дам приемного регистра и второму вы ходу блока синхронизации, группы ин формационных и управляющих вхрдов коммутатора информации являются соо ветственно группами информационных и управляющих входов устройства, а первый и второй управляющие выходы коммутатора информации соединены со ответственно с первым управляющим входом узла синхронизации и входом регистра состояния, вход-выход которого подключен к третьему выходувходу узла -коммутации управляющих сигналов, четвертый вход-выход которого соединен с выходом-входом комму татора информации, первым и вторым информационными выходами подключенно го соответственно к выходу из первой группы информационных выходов устрой ства и второму информационному входу первого буферного регистра, третий выход у зла-коммутации управляющих сигналов является выходом из второй группы управляющих выходов устройства, четвертый и пятый выход подключе ны соответственно к управляющим входам второго и третьего буферных регистров, информационные входы которых соединены с выходом передающего регистра, а выходы - соответственно с вторым входом элемента ИЛИ и с выходом из второй группы информационных выходов устройства, второй уп- равляющий вход узла синхронизации со единен с входом управляющего регистра и первым управляющим входом передающего регистра, а третий управляющий вход -- с шестым выходом узла ком мутации управляющих сигналов 2. Недостаток этого устройства заклю чается в низкой пропускной способнос ти, поскольку из-за отсутствия возможности сообщениям проходить без анализа свободные блоки сопряжения, обмен между модулями, подключенными к устройству, осуществляется за цикл работы устройства (произведение числа каналов обмена на время такта уст ройства) . Кроме того, устройство не позволяет автоматически отключать не исправные или. резервные модули. Цель изобретения - повышение про пускной способности и расширение фу циональных возможностей устройства. Поставленная цель достигается тем что в устройство, содержащее генератор тактовых импульсов и М каналов обмена, каждый из ко.торых . включает первый и второй приемные регистры, первый и второй передающие регистры буферный регистр, узел коммутации управляющих каналов, узел сравнения регистр состояния и регистр адреса, выход которого связан с первыми информационными входами буферного регистра и узла сравнения, вторым информационным входом соединенного с информационными входами первого приемного регистра и второго приемного регистра, информационный выход которого связан с информационным входом второго передающего регистра, управляющим входом соединенного с выходом генератора тактовых импульсов, первыми управляющими входами регистра состояния, первого приемного регистра и-буферного регистра, управляющими входами второго приемного регистра и первого передающего регистра, информационный вход которого поД слючен к выходу буферного регистра, вторым управляющим входом связанного с первым выходом узла коммутации управляющих сигналов, второй выход которого соединен с вторым управляющим входом регистра состояния, выходом подключенного к первому входу узла коммутации управляющих сигналов, второй вход которого связан с первым выходом узла сравнения,, вторым выходом соединенного с третьим входом узла коммутатции управляющих сигналов, третий выход которого подключен ко второму управляющему входу первого приемного регистра, первый и третий выходы, четвертый и шестой входы узла коммутации.управляющих сигналов выход первого приемного регистра и второй информационный вход буферного регистра К-го канала обмена () являются соответствующими управляюсщими выходами и входами и- информационными выходом и входом -К-ой группы входов и выходов устройства, в каждый канал обмена введены три коммутатора и узел запрета записи, причем первый, второй и третий входы узла запрета записи соединены соответственно с седьмым, третьим и четвертым входами узла коммутации управляющих сигналов, четвертым выходом соединенного с -четвертым входом узла запрета записи, ПЯТЫЙ вход которого подключен к выходу регистра состояния и управляющему входу первого коммутатора, информационный вход которого соединен с выходом второго передающего регистра, информационный вход второго коммутатора соединен с информационным входом второго приемного регистра, управляющий вход с.пятым выходом узла коммутации управляющих сигналов, шестым выходом соединенного с управляющим входом третьего коммутатора, информационный вход которого подключен к выходу первого передающего регистра, выход узла запрета записи К-го канала обмена связан с первым входом узла запрета записи (К-й)-го канала обмена, выход узла запрета записи первого канала обмена связан с первым входом узла запрета записи М-го канала обмена, выходы первого, второго и третьего коммутаторов К-го канала обмена соединеныс информационным входом второго приемного регистра (K-l)-ro канала обмена, выходы nep-vвого, второго и третьего коммутаторов первого канала обмена соединены с информационным входом второго приемного регистра М-го канала обмена. Причем узел запрета записи содержит три элемента И и элемент ИЛИ, выходом соединенный с выходом узла, первым, вторым и третьим входами соответственно с выходами первого, вто рого и третьего элементов И, первые входы которых соединены с четвертым входом узла, вторые входы соответственно с первым, пятым и третьим входами узла, третьи входы второго и третьего элементов И подключены к второму входу узла. На фиг. 1 показана блок-схема уст ройства; на фиг. 2 - функциональные схемл узла коммутации управляющих си налов и узла запрета записи. В состав устройства (фиг. 1) входят М каналов обмена, включающие ком таторы 1-3, регистры 4 состояния, пе вые передающие регистры 5, узлы 6 за прета записи,буферные регистры 7,вто рые передающие регистры 8,узлы 9 ком мутации управляющих сигналов, первые приемные регистры 10, вторые приемны регистры 11, узлы 12 сравнения и регистры 13 адреса, генератор 14 такто вых импульсов. Информационные вход и выход, управляющие входы и выходы каждого канала обмена соединены соот ветственно с информационным выходом и входом, управляющими выходами и зходами соответствующего модуля 15 вычислительной системы (эти же позиции встречаются в описании с индексомК для К-го канала обмена, где ,М). Первые, вторые и третьи коммутаторы 1-3 содержат буферные элементы (ИС 155ЛП8) с выходами на три состояния. Регистры 4 состояния содержат элементы занесения, сброса и выдачи информации и три триггера типа ms (основной-вспомогательный), указывающие состояние (Занят/Свободен.) соответственно вторых передающих регистров 8, первых передающих регистров 5 и первых приемных регистров 10 Узлы б запрета записи предназначены для формирования сигнала (Зап рет записи , запрещающего запись принятого сообщения К-м каналом обмена в приемные регистры (K-l)-ro ка нала обмена. Сигнал Запрет записи формируется узлами 6 запрета записи также при наличии сигнала Запрет записи на входах узлов 6 запрета записи. В состав узла б запрета записи К-го канала обмена (фиг. 2) входят .первый элемент И 16, элемент ИЛИ 17, второй элемент И 18, третий элемент И 19. Узлы 9 коммутации управляющих сигналов предназначены для коммутации управляющих сигналов, поступающих на и входы. Узлы 9 коммутации управляющих сигналов (фиг. 2) содержат: первый элемент И 20,/элемент ИЛИ 21, второй элемент К 22, третий элемент И 23, элемент НЕ 24, первый элемент И-НЕ 25, первый элемент ИЛИ 26, четвертый элемент И 27, пятый элемент И 28, второй элемент ИЛИ 29, второй элемент И-НЕ 30, шестой элемент И 31, третий элемент И-НЕ.32. Из регистра 4.К состояния в узел 9.К коммутации управляющих сигналов, поступают (фиг. 2) сигналы состояния Свободен третьего триггера, Свободен и Занят второго триггера, Свободен и Занят первогэ триггера. Из узла 9- К коммутации управляющих ригналов в регистр 4.К состояния поступают сигналы установки первого триггера, третьего триггера и второго триггера всостояния Свободен и Занят. Из узла 12.К сравнения в узел 9.К ком1чутации управляющих сигналов поступают сигналы Чужой С модуля 15.К вычислительной системы в узел 9.К коммутации управляющих сигналов поступают сигнаипы Принятои Запрос на передачу, и Отключение. Из узла 6. () запрета записи в узел 9.К коммутации управляющих сигналов поступает сигнал Запрет записи . Из узла 9.К коммутации управляющих,сигналов в узел 6.К запрета записи посту-, пает сигнал Запрет , по которому в узле 6.К запрета записи формируется сигнал Запрет записи , .в коммутатор 1..К поступает сигнал, по которому информация со входа коммутатора 1.К поступает на выход. В первый приемный регистр 10.К поступает сигнал приема информации, а в модуль 15.К вычислительной системы - сигнал Принять. Б буферный регистр 7. К поступает сигнал приема информации, а в модуль 15.К вычислительной системы сигнал Запрос удовлетворен . .В коммутатор З.К из узла 9.К коммутации управляющих сигналов поступает сигнал, по которому информация со входа поступает на выход коммутатора З.К. Узлы 12 сравнения содержат эле-, менты сложения по модулю 2, элемент ИЛИ и элемент НЕ и предназначены для сравнения полей адресов получателей в формате сообщения с адресами модулей 15 вычислительной системы, хранящимися в регистрах 13 адреса. Регистры 13 адреса предназначены для хранения адресов отправителей (адресов модулей 15 вычислительной системы). Адреса заносятся в реги.стры 13 адреса с помощью тумблерного набора с Пульта управления (не пока зан). В. качестве модуля 15 вычислитель ной систе могут использоваться пр цессоры, блоки памяти и т.п. Формат сообщения, передаваемого между каналами обмена, содержит сле дую14ие поля: адрес получателя; адре отправителя; данные (адрес ячейки памяти, признак Запрос/Ответ признак Чтение/Запись, собственно данные). Устройство работает следующим образом. В исходном состоянии все триггеры регистров 4 состояния находятся в состоянии Свободен. По пуску уст ройства генератор 14 начинает выраба тывать тактовые импульсы, под управлением которых между каналами обмена ,начинают циркулировать информационные сообщения. По каждому тактовому импульсу сообщение с выхода (К+1)-го канала обмена передается в один из приемных регистров К-го канала обмена, и состояние триггеров регистра 4.К состояния изменяется. До поступления тактового импульса поле адреса получателя сообщения сравнивается в узле 12.К сравнения с адресом модуля 15.К, хранящимся в регистре 13.К адреса, в результате чего на выходе узла 12.К сравнения появляется один Чужой . II II из сигналов Работу устройства рассмотрим на примере работы К-го канала обмена (Кг:1,М) , так как работа всех каналов обмен-а аналогична. При этом индекс канала в позициях узлов опущен там, где это не вызывает неоднозначности Каждый канал обмена может работать в четырех режимах: ЗАПИСЬ, ЧТЕ НИЕ , ПЕРЕДАЧА , ТРАНЗИТ . В режиме ЗАПИСЬ производится прием сообщения устройством от модуля 15. Он выполняется в два этапа: первый этап заключается в приеме сообщения от модуля 15 в буферный регистр 7 и передающий регистр 5, второй - в подключении буферного регист ра 5 к выходу К-го канала обмена через коммутатор 3. , При необходимости передать сообщение модуль 15 выставляет его (адрес получателя, данные) на своем информационном выходе и посылает сигнал Запрос на передачу в узел 9. Если второй триггер регистра 4 состояния находится в состоянии Свободен и есть сигнал Запрос на передачу узел 9 вырабатывает сигнал, разрешав ющий запись в буферный регистр 7 по переднему фронту тактового сигнала сообщения, из модуля 15 и адреса отправителя из регистра 13 адреса, а по заднему фронту тактового импульса это сообщение переписывается в передающий регистр 5 и сигн&л установки второго триггера 4 в состояние Занят. Сигнал, разрешающий запись в буферный рбгистр 7, посылается также в МОДУЛЬ 15, сообщая последнему что Запрос удовлетворен. По;, лучив этот сигнал, модуль 15 снимает сигнал Запрос на передачу и сообщение со своего выхода. Второй этап режима ЗАПИСЬ выполняется при условии нахождения первого триггера регистра 4 в состоСвободени второго триггера регистра 4 в состоянии Занят, в этом случае уз.ел 9 вырабатывает сигнал, разрешающий, прохождение информации через коммутатор 3, и снимает сигнал устанавливающий второй триггер состояния регистра 4 в состояние Занят. По переднему фронту тактового импульса второй триггер регистра 4 переходит в состояние Свобсден. Возможно одновременное выполнение обоих этапов, если первый триггер регистра 4 находится в состоянии Свободен, второй триггер регистра 4 в состоянии Занят, т.е. в передающем регистре 5 находится предыдущее сообщение, и есть сигнал Запрос на передачу . В этом случае узел 9 вырабатывает сигнал, разрешающий запись в буферный регистр 7, сигнал установки второго триггера регистра 4 в состояние Занят и сигнал, разрешающий прохождение сообщения из передающего регистра 5 через комг утатор 3. В режиме ЧТЕНИЕ производится прием сообщения, предназначенного для модуля 15, в приемный регистр 10. Если третий триггер регистра 4 нахоСвободендится в состоянии от модуля 15 поступит сигнал Принято об окончании обработки предыдущего сообщения и узел12 выработал сигнал Свой, то узел 9 вырабатывает сигнал, разрешающий запись в приемный регистр 10 сообщения (адрес отправителя, данные), и сигнал установки третьего регистра 4 в состояние Занят. Если третий триггер регистра 4 находится в состоянии За- . нят и нет сигнала Принято, узел 9 вырабатывает сигнал, подтверждающий состояние Занят третьего триггера регистра 4.Если третий триггер регистра.4 находится в состоянии Свободен или есть сигнал Принято , и узел 12 выработал сигнал Чужой, то узел 9 не вырабатывает сигнала установки третьего триггера регистра 4 в состояние Занят. В режиме ПЕРЕДАЧА осуществляется передача сообщения со входа К-го канала на его выход с записью сообщения в приемный регистр 11 и передающий регистр 8 по тактовому импульсу. Два.регистра необходима для развязки записи предыдущего сообщения в один из регистров следующего канала и записи сообщения со входа К-го канала. . Узел 9 не вырабатывает сигнал установки первого триггера регистра 4 в состояние Занято в следующих случаях: если на вход узла 9 коммутации управляющих сигналов поступает сигнал Запрет записи; если узел 12 сравне.ния выработал сигнал Свой и третий триггер регистра 4 находитс в состоянии Свободен, или от модуля 15 поступил сигнал Принято т.е. выполняется режим ЧТЕНИЕ; если первый триггер регистра 4 находится в состоянии Свободен, и второй триггер регистра 4 находится в состоянии Свободен, т.е. выполняется режим ТРАНЗИТ. Во всех остальных случаях узел 9 вырабатывает сигнал установки первого триггера регистра 4 в состояние Занят. Если первый триггер регистра 4 состояния находится в состо янии Занят, то это разрешает прохождение информации через коммутатор 2 на выход К-го канала. В режиме ТРАНЗИТ осуществляет ся передача сообщения со входа К-го канала на его выход в обход приемно го регистра 11 и передающего регистра 8 через коммутатор 1.Если первый и второй триггеры регистра 4 состояния находятся в состоянии Свободен, то узел 9 вырабатывает сигнал , разрешающий прохождение информ ции через коммутатор 1. Если при этом выполняется также режим ЧТЕНИЕ, то узел 6 вырабаты вает и передает на выход К-го канала сигнал Запрет записи , запреща ющий запись принятого К-ым каналом сообщения в приемный регистр следующего канала. Сигнал Запрет записи вырабатывается .узлом 6 также при наличии сигнала Запрет записи на входе К-го канала ( в режиме ТРАН ЗИТ). Кроме того, имеется возможность отключения модуля 15 отсистемы за счет постоянного открытия коммутато ра 1. Такое отключение происходит п сигналу от модуля 15 Отключение по которому первый триггер регистра 4 переходит в состояние Свободен в зависимости от которого коммутато 1 открыт для прохождения сообщений со входа К-го канала обмена на его выход а коммутаторы 2 и 3 закрыты. Таким образом устройство позволя ет производить статистический обмен сообщениями между модулями вычислительной системы и повысить пропус.кн способность устройства. Формула изобретения . J..Устройство связи для вычислител ной системы,содержащее генератор так товых импульсов и М каналов обмена, каждый из которых включает первый и второй приемные регистры, первый и второй передающие регистры, буферный регистр, узел коммутации управляющих сигналов, узел сравнения, регистр состояния и регистр адреса, выход которого связан с первыьда информационными входами буферного регистра и узла сравнения, вторым информационным входом соединенного с информационными входами первого приемного регистра и второго приемного регистра, информационный выход которого связан с информационным входом второго передающего регистра,управляющим входом соединенного с выходом генератора тактовых импульсов, первыми управляющими входами регистра состояния, первого приемного регистра и буферного регистра, управляющими входами второго приемного регистра и первого передающего регистра, информационный вход которого подключен к выходу буферного регистра, вторым управляющим входом связанного с первым выходом узла коммутации управляющих cигнcшoв второй выход которого соединен с вторым управляющим входом регистра состояния, выходом подключенного к первому входу узла коммутации управляющих сигналов, второй вход которого связан с первым выходом узла сравнения, вторым выходом соединенного с третьим входом узла коммутации управляющих сигналов, третий выход которого подключен к второму управляющему входу первого приемного регистра, первый и третий выходы , четвертый, пятый и шестой входы узла коммутации управляющих сигналов,выход первого приемного регистра и второй информационный вход буферного регистра К-го. канала (,М)- обмена являются соответствующими yпpaвляющи 1и выходами и входами и информационными выходом и входом К-ой группы входов и выходов устройства, о т л и ч а ющ е е с я тем, что, с целью повышения пропускной способности устройства, в каждый канал обмена введены три коммутатора и узел запрета записи, причем первый, второй и третий входы узла запрета записи соединены соответственно с седьмым: , третьим и четвертым входами узла коммутации управляющих сигналов, четвертым выходом соединенного с четвертым входом узла запрета, записи, пятый вход которого подключен к выходу регистра состояния и управляющему входу первого коммутатора, информационный вход которого соединен с выходом второго передающего регистра , информационный вход второго коммутатора соединен с информационным входом вторюго приемного регистра, управляющий вход с пятым выходом узла коммутации

управлякнцих сигналов, шестым выходом соединенного с управляюЕцим входом третьего коммутатора, информационный вход которого подключен к выходу первого передающего регистра, выход узла запрета записи К-го канала обмена связан с первым входом узла запрета записи (К-1)-го канала обмена, выход узла запрета записи первого канала омена связан с первым-входом узла запрета записи М-го канала обмена, выходы первого, второго и третьего коммутаторов К-го канала обмена соединены с информационным входом второго приемного регистра {К-1)-го канала обмена, выходы первого, второго и третьего коммутаторов первого канала обмена соединены с информационным входом второго приемного регистра М-го канала обмена.

2. Устройство по п.1, о т л и ч аю щ е е с я тем, что узел запрета записи содержит три элемента И и элемент ИЛИ, выходом соединенный с выходом узла, а -первым, вторым и третьим входами соответственно с выходами первого, второго и третьего элементов И, первые входы которых соединены с четвертым входом узла, вторые входы соответственно с первым, ПЯТЕЗМ и третьим входами узла, третьи вхо4ДЫ второго и третьего Элементов И подключены к второму входу узла.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР О 734654, кл. G 06 F 3/04, 1977.

2.Авторское свидетельство СССР по заявке № 2765316/18-24,

кл. G 06 F 3/04, 1979 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство связи для вычислительной системы | 1981 |

|

SU983699A1 |

| Устройство связи для вычислительной системы | 1982 |

|

SU1062678A1 |

| Устройство связи для вычислительной системы | 1980 |

|

SU898413A1 |

| Устройство связи для вычислительнойСиСТЕМы | 1979 |

|

SU802957A1 |

| Канал обмена | 1986 |

|

SU1410045A1 |

| Устройство связи для вычислительной системы | 1980 |

|

SU924694A1 |

| Устройство для сопряжения модулейВычиСлиТЕльНОй СиСТЕМы C KOHTPO-лЕМ | 1978 |

|

SU807258A1 |

| Устройство связи для вычислительной системы | 1982 |

|

SU1042008A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1280642A2 |

| Многоканальное устройство связи для вычислительной системы | 1980 |

|

SU943695A1 |

п

S.()

/5. л

фг/г 2

Авторы

Даты

1982-09-30—Публикация

1981-03-31—Подача