элементов И соответствующей группы элемв)атОв и, сторые входы элементов И Кйждой группы соединены с соответств эщими разрадными выходами регистра ЗЬйл, выходы элементов ИЛИ соединены с группой информационных выходов устройства, группа адресных входов уст ройствб соединена со входами дешифратбра и является первой группой адресHjbJX Выходов устройства, а второй группой адресных выходор устройства являются выходы регистра номера массива. первая и вторая группы выходов шифраТора соединены с разрядными входами соответственно регистра номера массива и регистра золы.

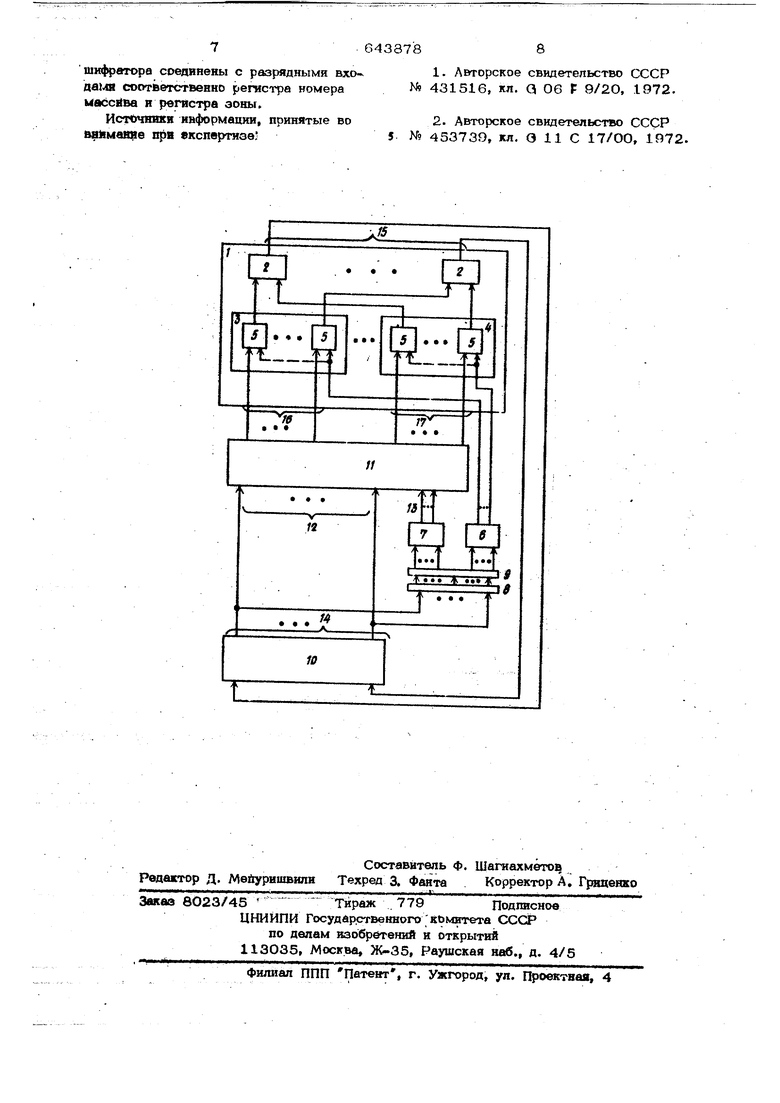

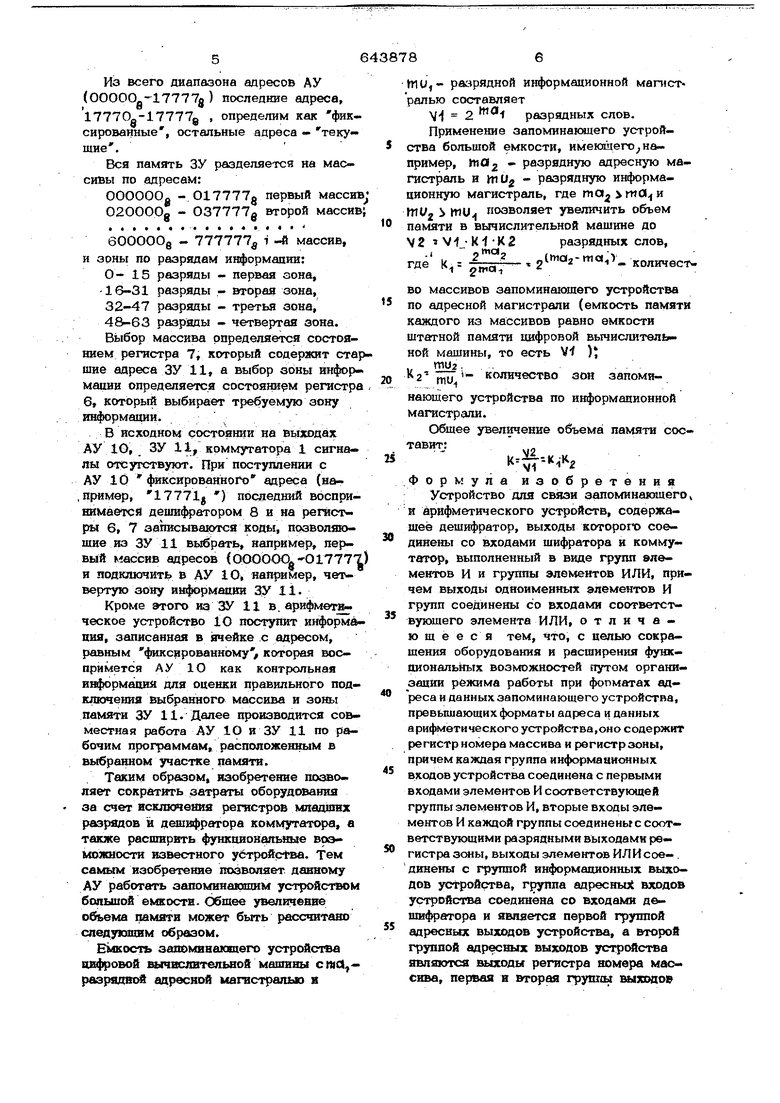

Структурная схема устройства приведена на чертеже.

Устройство для связи запоминающего и арифметического устройств содержит коммутатор 1, вьшолненный в виде группы элементов ИЛИ 2, групп 3 и 4 элементов И 5, регистр 6 зоны, регистр 7 номера массива, дешифратор 8, шифратор 9. Кроме того, на чертеже позициями 10 и 11 обозначены соот ветственно арифметическое устройство и аапоминакоцее устройство, позицией 12яврвая группа адресных выходов устройства, позицией 13 - вторая группа адресных выходов устройства, позицией 14 - группа адресных входов устройства, позицией 1 б - группа информационных выходов,. позициями 16, 17 - группы информационных входов устройства.

Устройство работает слёдуинцим образом.

Вся память запоминанмцего устройст ва (ЗУ) 11 делится на массивы {по адресам) и зоны (по разрядам информации). Выбор массива определяется состошшэм регистра 7, управлякшшм старшими разрядами адреса запоминакяцего устройства 11, и состоянием регистра 6, который управляет зоной информации.

Весь массив адресов, формируемых арифметическим устройством (АУ) 10 разделяется на два массива. Первый подмарсив адресов предназначен для рабочих программ вычислительной машины (текущие адреса). Второй подMecciiB адреса, являкшшеся кодами управпенва, 1фехшазваченные для переко точения/магистралей устройства адресаЕШи к памяти (фахсировант. ).

Во время работы вычислительной ыашнны и фиксированные адреса поступают в запоминающее устройство 11 н на вход дешифратора 8. При составлении программ учитывается, что формирование и выдача в ЗУ 11 текущих адресов вызывает появление в АУ 1Q рабочей информации. Фшссиро-: ванный адрес выполняет две функции. Во-первых, этот адрес воспринимается дешифратором 8, для подключения требуемого участка памяти ЗУ 11 к арифметическому устройству 10. Во-вторых, информация, которая считается по фиксированному адресу р АУ 10,является признаком для контроля правильного подключения участка ЗУ 11.

Алгоритм построения программ вычислительной машины следукйыий:

-АУ 1О формирует фиксированный адрес, который поступает в устр10йство,

вызывая переключение магистралей, и в ЗУ 11, где осуществляет контроль правильности подключения уч(астка йрог. рамм ЗУ Ну .;

- далее исполняются программы, расположенные в подключенном участке памяти ЗУ 11.

При переходе программ на другой участок ЗУ 11 указанный алгоритм повторяется.

ЗУ 11 реагирует на адреса, поступающие иа АУ 10 и регистра 7. Адрес на выходе регист ра 7 является базовым адресом АУ 1О. Информация на этот регистр в Виде кода фиксирс каЯ

ного адреса устанавливается перед Исполнением программ (текущих адресов). Регистр 6 также зК таиавцивается в определенное состояние кодоК фиксйрованного адреса. При этом снгнал с этого регистра разрешает прохоясдение через коммутатор 1 в, АУ Ю наформации с выбранной аотл ЗУ 11. Оставшиеся разряды ииформаяии ЗУ 11 блокируются коммутатором 1.

Блокировка изменения состояния регистра 6t 7 устройства выполняется программным способом.

Приведем описание работы устройств ва адресации к памяти ва спедукшем числовом примере.

Пусть разрядность алресных и инфо мадионных магистралей АУ 10 и ЗУ 11 такова, го

-адреса А У содержат 13 разрядов,

-информации А У содержит 16 разрядов,

-адреса ЗУ имеют 18 разрвдов,

-информация ЗУ имеет 64 разряда;

Из всего диапазона адресов АУ (OOOOO--17777g ) последние адреса, l7770g-17777g , определим как фиксированные, остальные адреса - текущие.

Вся память ЗУ разделяется на массивы по адресам:

OOOOOQg - O17777g первый массив;

020OOOg - 037777g эторой массив; бОООООд - 777777д i -и массив, и зоны по разрядам информапии: О- 15 разряды - первая оона, 16-31 разряды - вторая зона, 32-47 разряды - третья зона, 4S-63 разр;яды - четвертая зона. Выбор массива определяется состоянием регистра 7t который содержит ста шие адреса ЗУ 11 а выбор зоны инфор мации определяется состоянием регистр 6, который выбирает требуемую зону информации. В исходном состоянии на выходах АУ 1О, ЗУ 11, коммутатора 1 сигналы отсутствуют. При поступлении с АУ 10 фиксированного адреса (на, пример, 17771 ) последний воспри нимаетсй дешифратором 8 и на регастры 6, 7 записыва1отся коды, позволяющие из ЗУ 11 выбрать, например, первый массив адресов {QOOOOO «O1777 и подключить в АУ Ю например, четвертую зону информации ЗУ 11. Кроме этого та ЗУ 11 в. арифметв ческое устройство 1О поступит информа ция, записанная в ачейке с адресом, равтлм фиксированному, которая вое- примется АУ Ю как контрольная информация для оценки правильного подключения выбранного массива и зоны памяти ЗУ 11 Далее производится совместная работа АУ 1О и ЗУ 11 по рабочим программам расположенным в выбранном участке памяти. Таким образом, изобретение позволяет сократить затраты оборудовашш за счет исключения регистров младших разрадов и дешифратора коммутатора а также расширить функциональ эле возможности известного y6тpoйctвa. Тем самым изобретение гахзволяет данному АУ работать запоминающим устройством большой емкости. Общее увеличевве объема памяти может быть рассчитано следуплцвм образом. Емкость запомвнаюшего устройства цифровой Ш11Ч11сявтельво9 машины cracl,- разрядвс адресной магистралью 8

tnu,- разрядной информационной мап страпью составляет

VI 2 1 разрядных слов.

Применение запоминакндего устройства большой емкости, имeющeгo например, жа2 - разрядную адресную магистраль и жи - разрядную информационную магистраль, где щу V позволяет увеличить объем памяти в вычислительной машине до V2 V1.-K1-K2 разрядных слов, . 2 г ,2 °2-tta.V, количест i gwo-, во массивов запоминаимцего устройства по адресной магистрали (емкость памяти каждого из массивов равно емкости штатной памяти цифровой вычислительной машины, то есть Vf ) muj: Кг 1- количество зон запоминающего устройства по информапионной магистрали. Общее увеличение объема памяти составит:Ф ормула изобретения Устройство для связи запоминающего и арифметического устройств, содержащее дешифратор, выходы которогт) соединены со входами шифратора и коммутатор, выполненный в виде групп алементов И и группы элементов ИЛИ, причем выходы одноименных элементов И групп соединены со входами соответствующего элемента ИЛИ, отличающееся тем, что, с целью сокращения оборудования и расширения функциональных возможностей путом организации режима работы при фрпматах адреса и данных запоминающего устройства, превышающих форматы адреса и данных apH(JHvfeTH4ecKoro устройства,оно содержит регистр номера массива и регистр зоны, причем каждая группа информацисжных входов устройства соединена с первыми входами элементов И соответствующей группы элементов И, вторые входы элементов И каждой группы соединены с соответствующими разрядными выходами регистра зоны, выходы элементов ИЛИсое-. динены с группой информационных выходов устройства, группа адресный входов устройства соединена со входами дешифратора и является первой группой адресных выходов устройства а второй группой адресных выходов устрсЛства являкпч::я выходы регистра массива первая и вторая грутол выходов

шифратора соединены с разрядными вхо-к aeiJta соответственно регистра номера массива R регистра зоны

Источники ивформадии, принятые во2. Авторское свидетельство СССР

ваиманае при вкспвртиае5 № 453739, кл, О 11 С 17/00. 1072.

6438788

1. Авторское свидетельство СССР № 431516, кп. Q Об F 9/20, 1972.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для связи процессора с запоминающим устройством | 1983 |

|

SU1083196A1 |

| Микропроцессор для вводавывода данных | 1976 |

|

SU618733A1 |

| Устройство для обмена двухмашинного вычислительного комплекса | 1981 |

|

SU991403A1 |

| Устройство для управления режимамиОбМЕНА РЕзЕРВиРОВАННОй СиСТЕМы | 1979 |

|

SU849216A1 |

| Устройство для сопряжения ЦВМ с внешним устройством | 1989 |

|

SU1661779A1 |

| Устройство для контроля цифровых узлов | 1985 |

|

SU1238085A2 |

| Устройство для формирования исполнительных адресов цифровой вычислительной машины | 1978 |

|

SU728129A1 |

| СПОСОБ ДЛЯ ЦИФРОВОЙ СУБСТРАКЦИОННОЙ АНГИОГРАФИИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1992 |

|

RU2043073C1 |

| Имитатор абонентов | 1983 |

|

SU1291987A1 |

| Устройство для сопряжения эвм с абонентами | 1984 |

|

SU1215114A1 |

Авторы

Даты

1979-01-25—Публикация

1976-08-05—Подача