ТТГ

h f

Изобретение относится к вычисли тельной технике, предназначено для вычисления значения логической функ ции на входном наборе ее аргументов и может использоваться при построё, НИИ комбинационных узлов цифровых автоматов.

Известно устройство, которое используется для в 1числения логических выражений, содержащее 41 информационных входов И 211 управляющих входов, п элементов НЕ, 2бэлементов И и элемент ИЛИ, выход которого является выходом устройства, а его входы подключены к выходам элементов И, первые входы которых управляющие, а остальные п входов каждого элемента И подключены соответствующим об разом к выходам элементов НЕ и информационным входам модуля..

Устройство путем настройки peaлизует любые логические функции г} . переменных l

Недостатком устройства является большая сложность.

Наиболее близким по технической сущности к предлагаемому является устройство, которое имеет каскадную структуру и содержит 2 универсальных логических модулей, информацион ные входы которых подключены к (п-т) информационным входам устройства, а их управляющие -входы являются управляющими входами устройства, выводы универсальных логических-модулей подключены к входам коммутатора, управляющие входы которого подключены к остальным и информационным входам модуля, выход коммутатора является выходом устройства 2J .

Недостатком известного устройства является его сложность, что не позволяет использовать его при обработке многоразрядной информации. Например, при П 10 и использовании универсальных логических модулей с двухъярусной канонической структурой схема устройства имеет сложность, по Квайну равную 7590.

Целью изобретения является упрощение устройства для вЕлчисления логических выражений.

Поставленная цель достигается тем, что устройство для вычисления логических выражений п переменных, содержащее универсальный логический модуль,информационные входы goToрого подключены к m информационным входам устройства (), содержит блок памяти, адресные входы которого подключены к (п -tn) информационным входам устройства, выходы блока памяти подключены к 2™ управляющим вхо дам универсального логического модуля соответственно, выход которого является выходом устройства, входы записи и считывания блока памяти под

ключены к входам записи и считывания устройства соответственно.

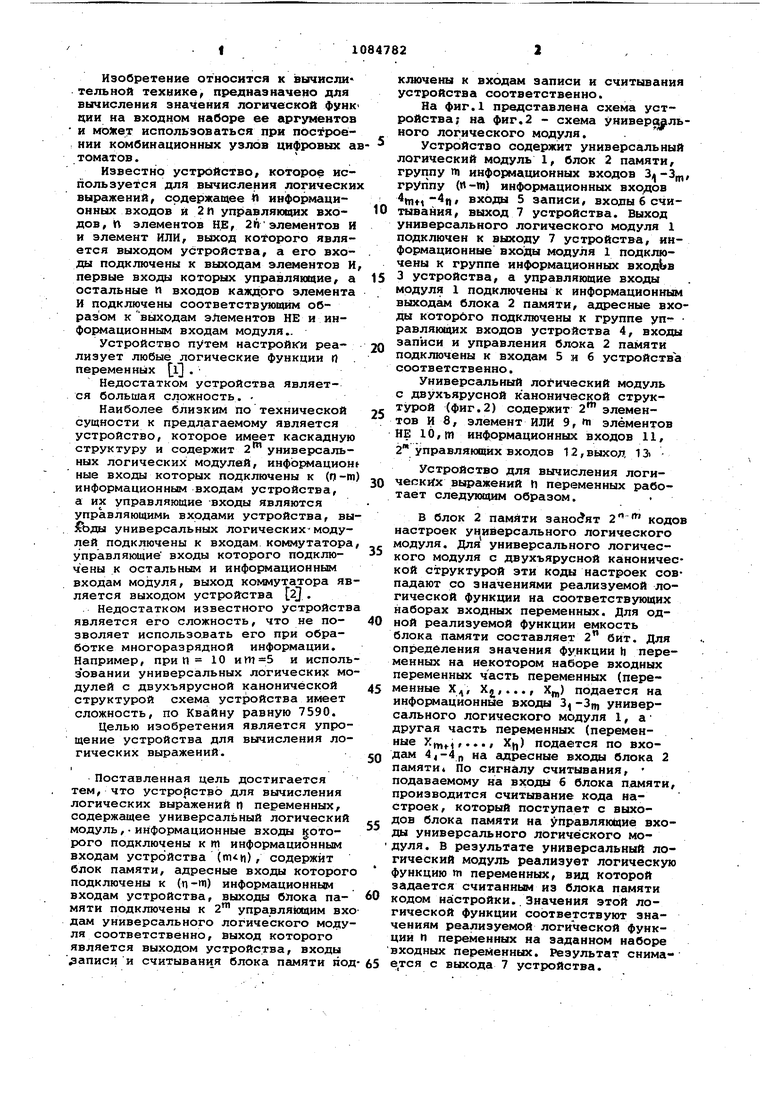

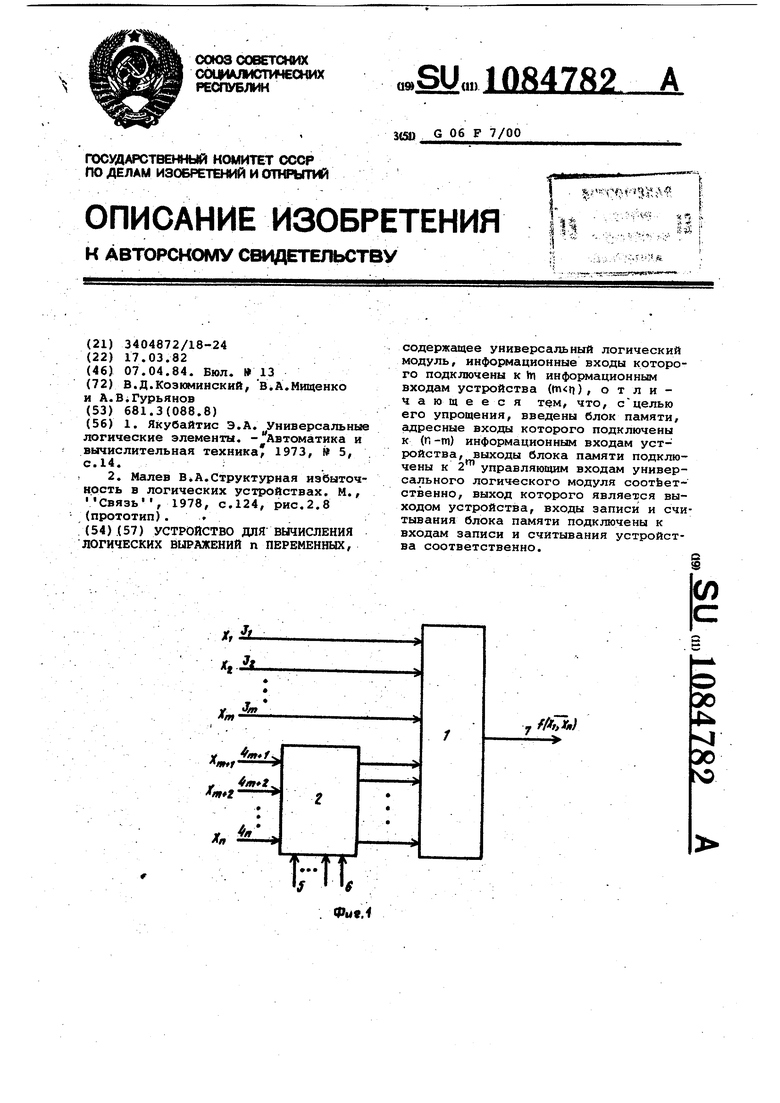

На фиг.1 представлена схема устройства; на фиг.2 - схема универс1|1льного логического модуля.

Устройство содержит универсальный логический модуль 1, блок 2 памяти, группу П) информационных входов группу (tt-tn) информационных вхрдов входы 5 записи, входы б считывания, выход 7 устройства. Выход универсального логического модуля 1 подключен к выходу 7 устройства, информационные входы модуля 1 подключены к группе информационных входЬв 3 устройства, а управляющие входы модуля 1 подключены к информационным выходам блока 2 памяти, адресные входы которбго подключены к группе управляющих входов устройства 4, входы записи и управления блока 2 памяти подключены к входам 5 и 6 устройства соответственно.

Универсальный логический модуль с двухъярусной канонической структурой (фиг.2) содержит 2 элементов И 8, элемент ИЛИ 9, ш элементов НЕ l6,m информационны: входов 11, 2 управляющих входов 12, выход 13i

Устройство для вычисления логических выражений п переменных работает следующим образом.

В блок 2 памяти кодо настроек универсального логического модуля. Для универсального логического модуля с двухъярусной канонической структурой эти коды настроек совпадают со значениями реализуемой логической функции на соответствующих наборах входных переменных. Для одной реализуемой функции емкость блока памяти составляет 2 бит. Для Определения значения функции И переменных на некотором наборе входных переменных часть перемЕ Нных (переменные Хд, Xj,..., Х,„) подается на информационные входы универсального логического модуля 1, а другая часть переменных (переменные Х,..., Х|,) подается по входам 4|-4 на адресные входы блока 2 памяти По сигналу считывания, подаваемому на входы 6 блока памяти, производится считывание кода настроек, который поступает с выходов блока памяти на управляющие входы универсального логического модуля, в результате универсальный логический модуль реализует логическую функцию m переменных, вид которой задается считанным из блока памяти кодом настройки..Значения этой логической функции соответствуют значениям реализуемой логической функции п переменных иа заданном наборе входных переменных. Результат снимается с выхода 7 устройства.

Для оценки технико-экономической эффективности предлагаемого устройства в качестве базового устройства может, быть выбран мультиплексор, который может использоваться для реализации логических функций п перемен(1ых.

При П -10 мультиплексор имеет сложность, по Квайну равную 12248, и 1024 управляющих входа. Из-за большого числа управляющих входов такая схема не может быть реализована с использованием интегральной технологии. Поэтому для хранения кодов настроек необходимо применение наряду с мультиплексором блока памяти на 1024 выхода. Схему для реализации логических функций 10 переменных, можно построить путем каскадного объединения 33 мультиплексоров, реализующих логические функции 5 переменных. В этом случае сложность сХ мы составит 7392 по Квайну, а быстродействие уменьшится примерно в два раза.

При реализации- логических функций 10 переменных предлагаемым устройством дли nt 5 потребуется блок памяти емкостью 32-разрядных слова (1024 бит) и универсальный логический модуль на 5 переменных (например, мультиплексор, сложность которого при in 5 составит 224 по Квайну).

Таким образом, по сравнению с базовым объектом получен выигрыш в сложности в раз без учета памяти хранения кодов настроек-, емкость которой как для базового, так и для предлагаемого устройства одинаковая.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления логических выражений @ переменных | 1981 |

|

SU962918A1 |

| Устройство выдачи команд и сбора информации на основе семи универсальных регистров ввода/вывода с изменяемой логикой работы | 2017 |

|

RU2678667C1 |

| Устройство для вычисления логических выражений @ переменных | 1983 |

|

SU1119004A1 |

| Ассоциативное запоминающее устройство | 1989 |

|

SU1741175A1 |

| Табличный процессор | 1982 |

|

SU1108446A1 |

| УСТРОЙСТВО КОМПЕНСАЦИИ РАЗЛИЧИЙ В ЧУВСТВИТЕЛЬНОСТИ ЭЛЕМЕНТОВ МАТРИЦЫ ФОТОПРИЕМНИКОВ | 1995 |

|

RU2108685C1 |

| Устройство для выполнения команд реализации систем многоместных логических функций | 1981 |

|

SU999051A1 |

| Многофункциональный запоминающий модуль для логической матрицы | 1989 |

|

SU1642525A1 |

| Запоминающее устройство с параллельным произвольным доступом к строкам и окнам данных | 1987 |

|

SU1499355A1 |

| Устройство для управления операцией записи | 1981 |

|

SU1003091A1 |

УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ЛОГИЧЕСКИХ ВЫРАЖЕНИЙ П ПЕРЕМЕННЫХ, содержащее универсальный логический модуль, информационные входы которого подключены к tn информационным входам устройства () отличающееся , что, сцелью его упрощения, введены блок памяти, адресные входы которого подключены к (П -т) информационным входам устройства, выходы блока памяти подключены к 2 управляющим входам универсального логического модуля состЬетственно, выход которого является выходом устройства, входы записи и считывания блока памяти подключены к входам записи и считывания устройства соответственно. (Л с

ff.

12

П

фиг. 2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Якубайтис Э.А | |||

| Универсальные логические элементы | |||

| Приспособление для склейки фанер в стыках | 1924 |

|

SU1973A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Малев .Структурная избыточность в логических устройствах | |||

| М., Связь, 1978, с.124, рис.2.8 (прототип) | |||

| . | |||

Авторы

Даты

1984-04-07—Публикация

1982-03-17—Подача