Устройство относится к вычислительной технике и автоматике, предназначено для вычисления значений логических выражений и может использоваться при построении комбинационных узлов и цифровых автоматов.

Известны устройства, которые могут использоваться для вычисления логических выражений, например универсальный логический модуль, содержащий п информационных и 2 управляющих входов, п элементов НЕ, 2 элементов И и элемент ИЛИ, выход которого является выходом устройства, а его входы подключены к выходам элементов И, первые входы которых управляющие, а остальные п входов подключены соответствующим образом к выходам элементов НЕ и информационным входам устройства. Устройство путем настройки реализует любые логические функции входных булевых переменных 1 Недостатком известного устройства является большая сложность.

Наиболее близким к предлагаемому по технической сущности является устройство, которое имеет каскадную структуру и содержит 2 универсальных логических модулей, информационные входы которых подключены к n-m инфорглационным входам устройства, а их управляющие входы являются управляющими входами устройства, выходы универсальных логических модулей подключены к входам коммутатора, управляющие входы которого подключены к остальным m информационным входам модуля 2.

10

Недостатком известного устройства является СЛОЖНОСТИ, что не позволяет использовать его при обработке многоразрядной информации. Например, при п 10, m 5 и использо15вании универсальных логических модулей с двухъярусной канонической структурой схема устройства будет иметь сложность по суммарному числу входов логических элементов, рав20ную 7590.

Цель изобретения - упрощение устройства для вычисления логических выражений.

Поставленная цель достигается

25 тем, что устройство для вычисления логических выражений п переменных, содержащее два мультиплексора, выход первого мультиплексора является выходом устройства, управляющие

30 входы первого мультиплексора подключены к m информационныь входам устройст а, п-т информационные входы второго мультиплексора подключены к информационным входам устройства, управляющие входы которого подключены к управляющим входам второго мультиплексора, содержит блок памяти, входы записи которого подключены к выходу второго мультиплексора, а входы управления - к дополнительным управляющим входам устройства, выходы блока памяти подключены к информационным входам первого мультиплексора.

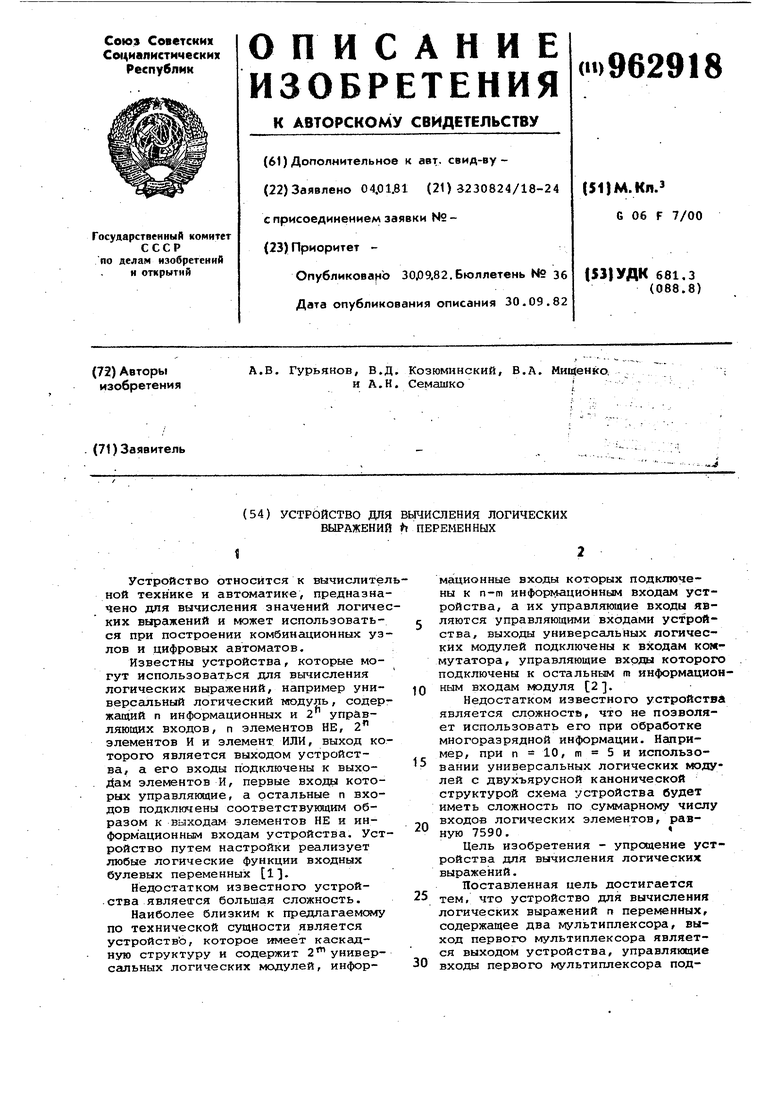

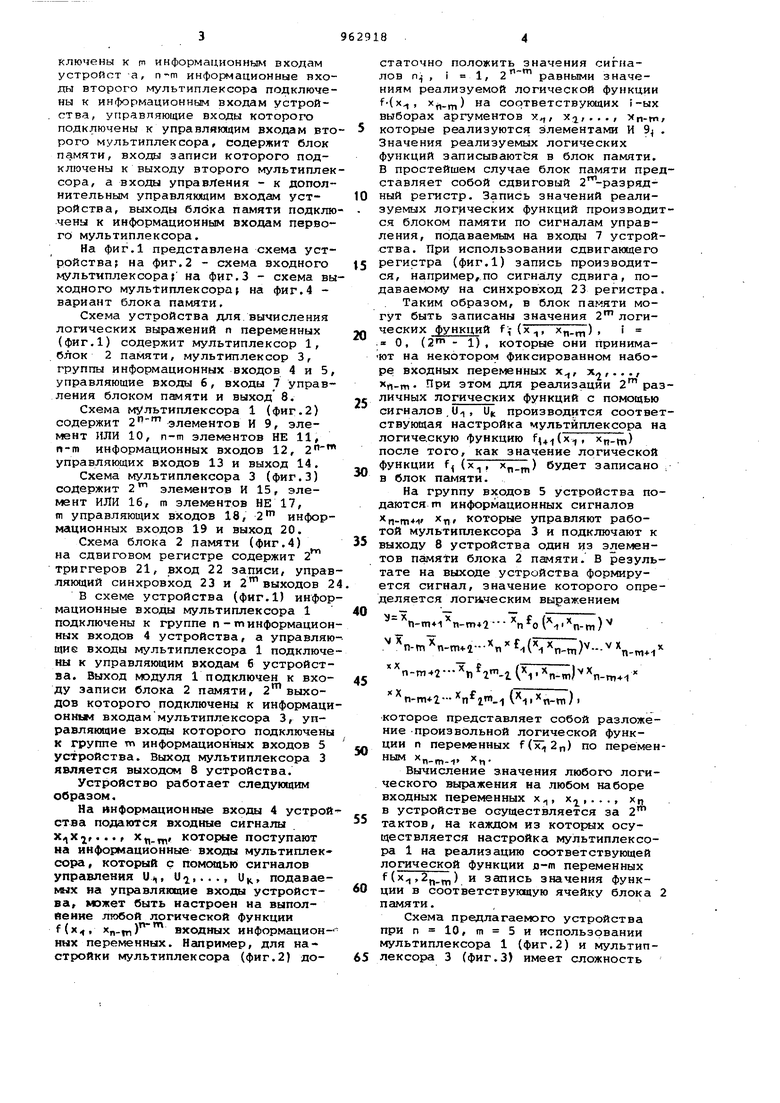

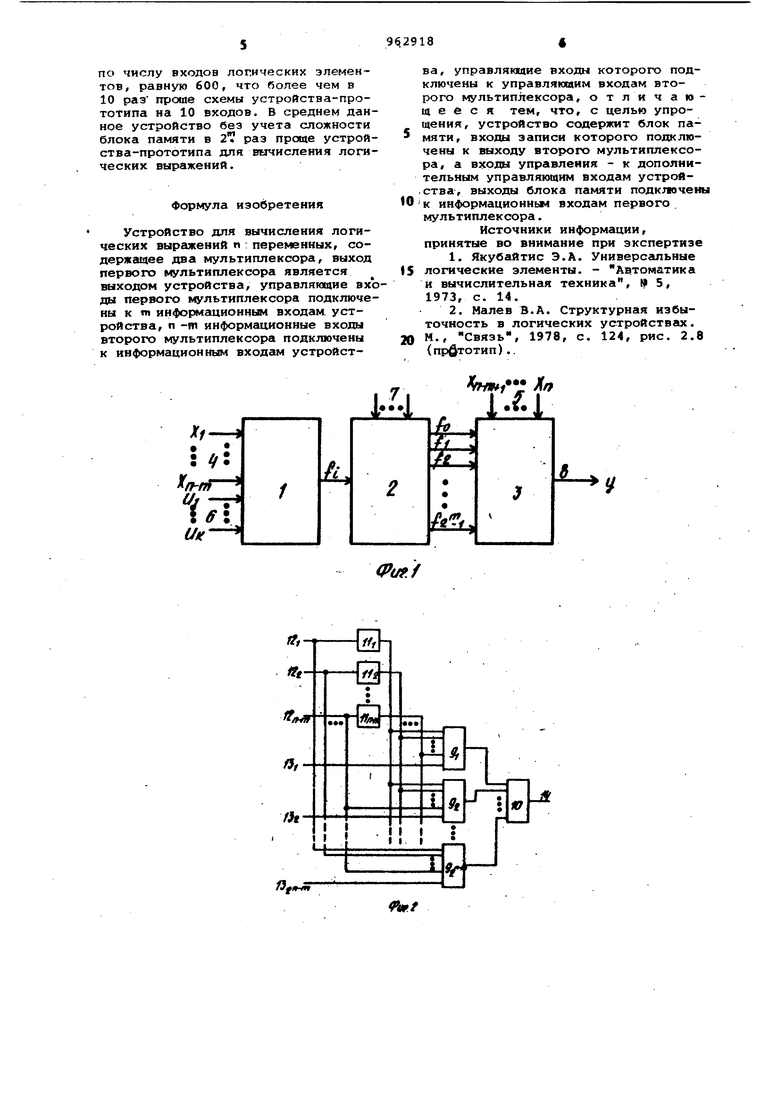

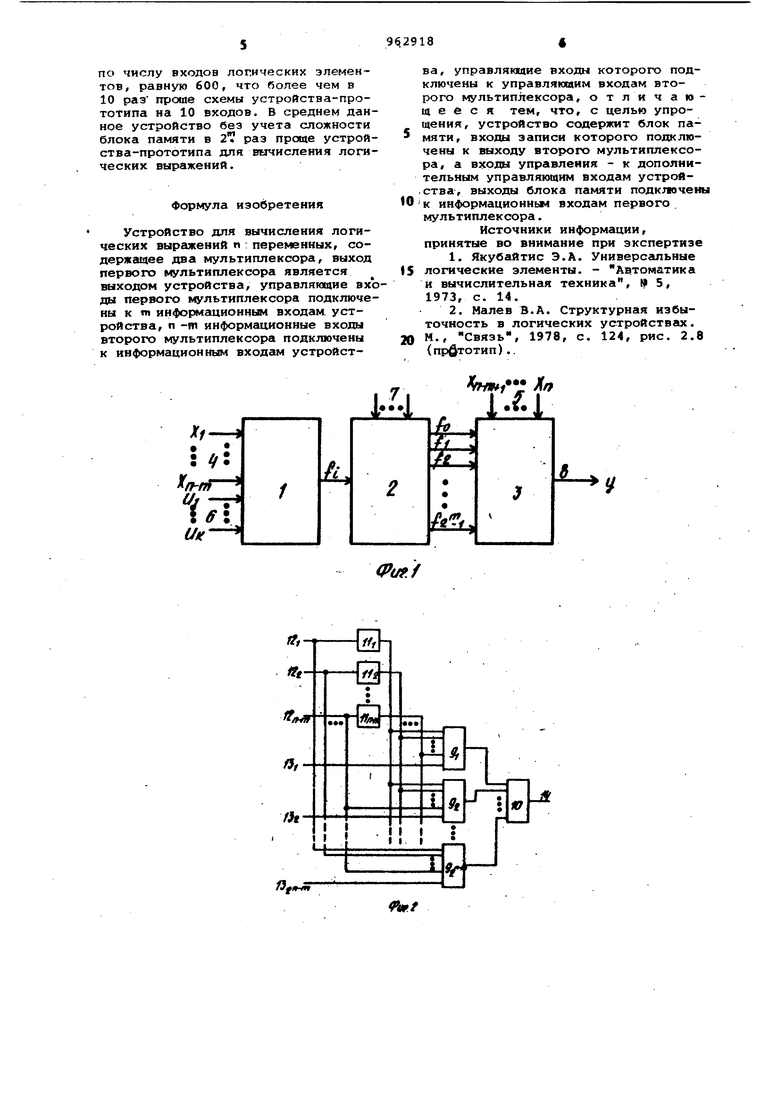

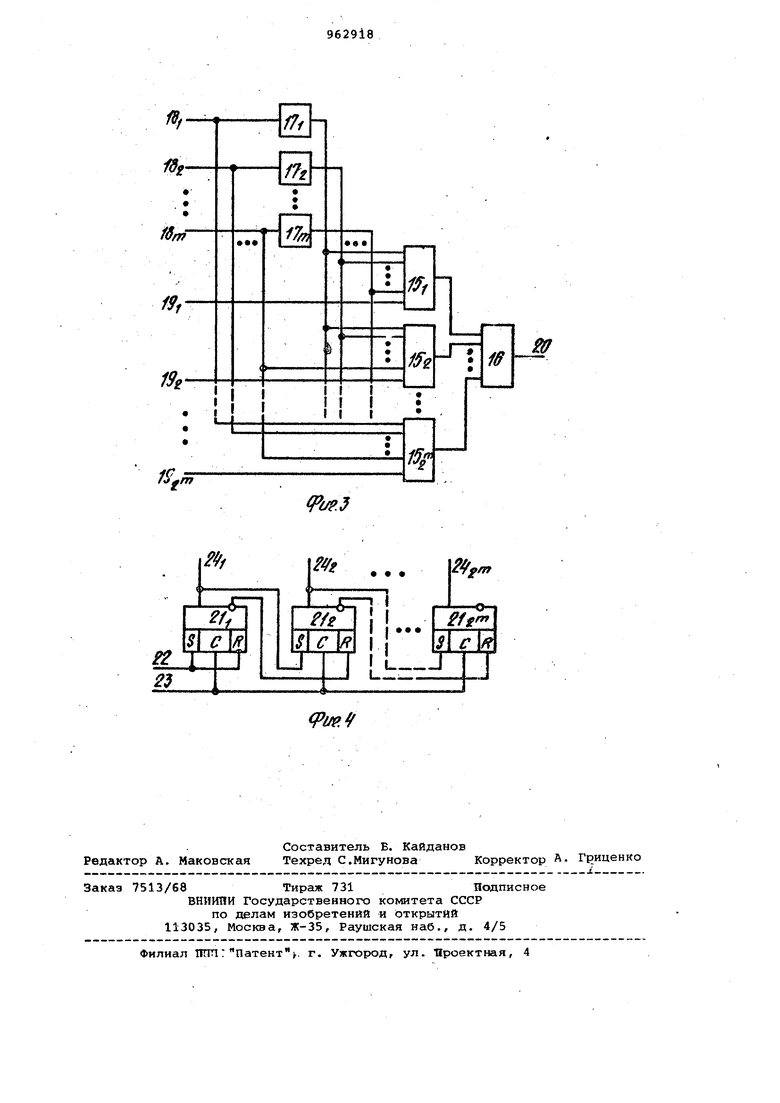

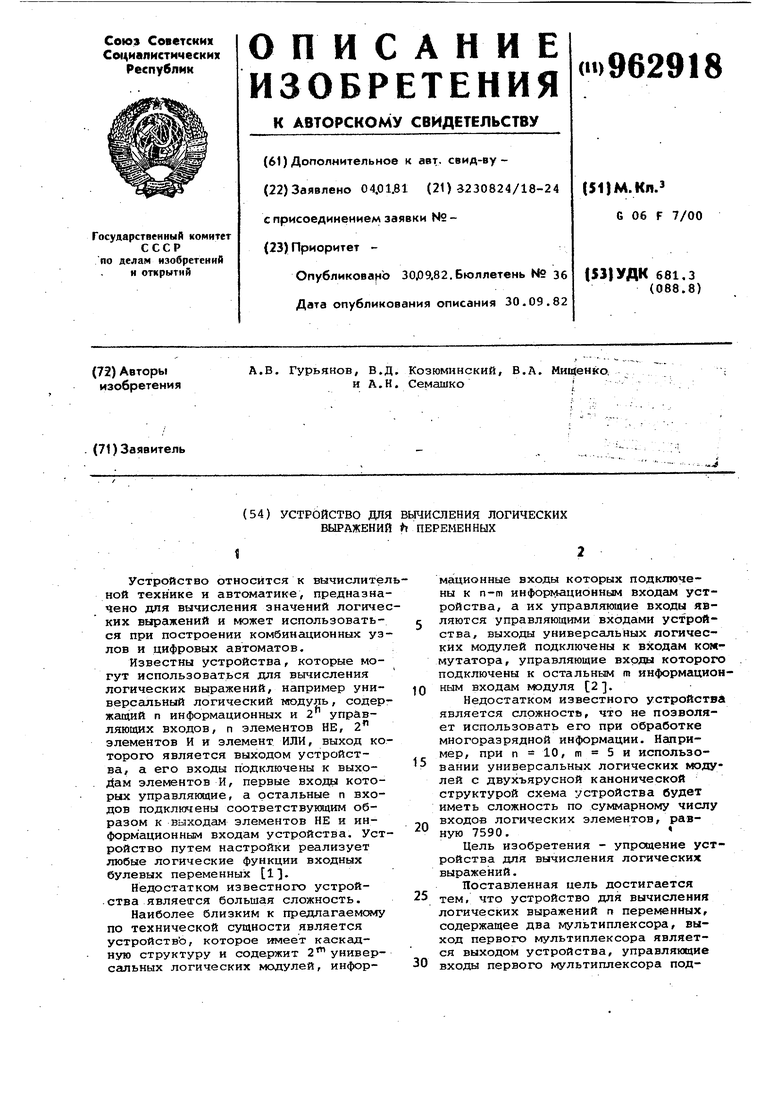

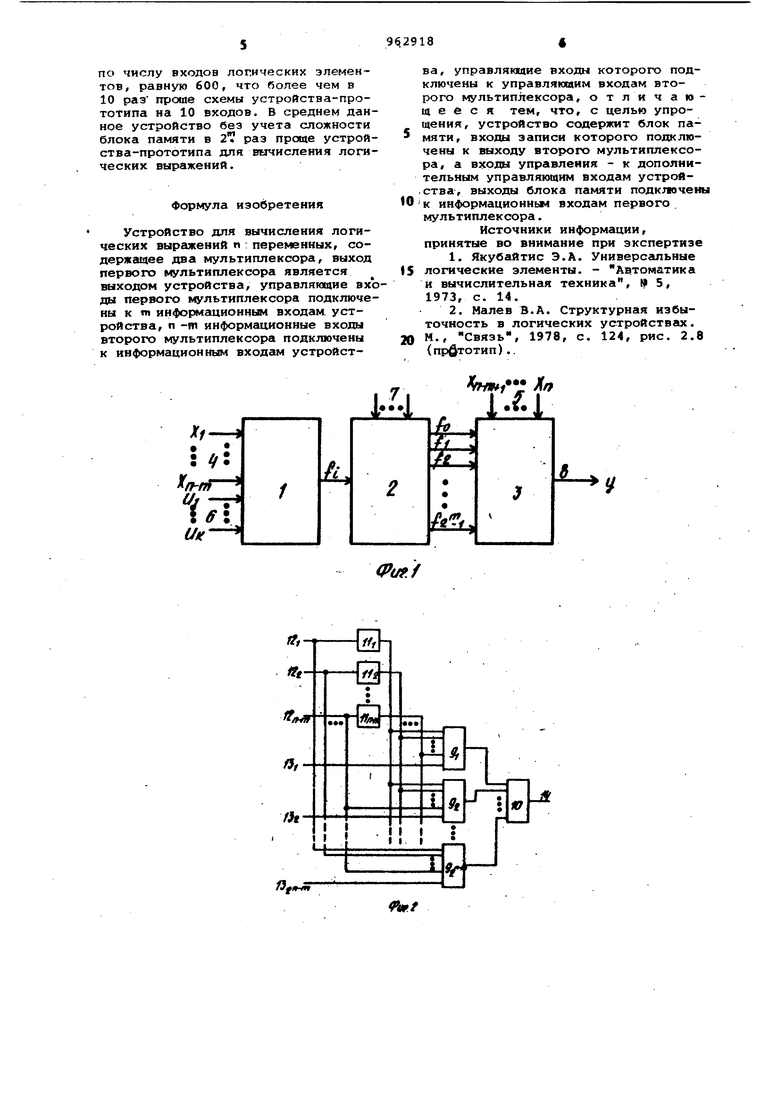

На фиг,1 представлена схема устройства; на фиг.2 - схема входного мультиплексора на .З - схема выходного мультиплексора на фиг.4 вариант блока памяти.

Схема устройства для вычисления логических выражений п переменных (фиг.1) содержит мультиплексор 1, блок 2 памяти, мультиплексор 3, группы информационных входов 4 и 5, управляющие входы 6, входы 7 управления блоком памяти и выход 8.

Схема мультиплексора 1 (фиг-2) содержит элементов И 9, элемент ИЛИ 10, n-m элементов НЕ 11, n-m информационных входов 12, управляющих входов 13 и выход 14.

Схема мультиплексора 3 (фиг.З) содержит 2 элементов И 15, элемент ИЛИ 16, m элементов НЕ 17, m управляющих входов 18, 2 информационных входов 19 и выход 20.

Схема блока 2 памяти (фиг.4) на сдвиговом регистре содержит 2 триггеров 21, вход 22 записи, управляющий синхровход 23 и 2 выходов 24

В схеме устройства (фиг.1) информационные входы мультиплексора 1 подключены к группе п-mинформационных входов 4 устройства, а управляющие входы мультиплексора 1 подключены к управляющим входам 6 устройства. Выход модуля 1 подключен к входу записи блока 2 памяти, 2 выходов которого подключены к информационным входам мультиплексора 3, управляющие входы которого подключены к группе m информационных входов 5 устройства. Выход мультиплексора 3 является выходом 8 устройства.

Устройство работает следующим образом.

На информационные входы 4 устройства подаются входные сигналы , ...г х., которые поступают на информационные входы мультиплексора , который с помснцыб сигналов управления Uj,, U,.,., U, подаваемых на управляющие входы устройства может быть настроен на выполнение любой логической функции f (х, х.р) входных информацион- ных переменных. Например, для настройки мультиплексора (фиг.2) достаточно положить значения сигналов п , i 1, равными значениям реализуемой логической функции

) на соответствующих i-ых

f-ix-,.

n-m

выборах аргументов У., х,..., Xn-rn, которые реализуются элементами И 9 . Значения реализуемых логических функций записываются в блок памяти. В простейшем случае блок памяти представляет собой сдвиговый 2 -разрядный регистр. Запись значений реализуемых логических функций производится блоком памяти по сигналам управления, подаваемым на входы 7 устройства. При использовании сдвигающего регистра (фиг.1) запись производится, например,,по сигналу сдвига, подаваемому на синхровход 23 регистра. Таким образом, в блок памяти могут быть записаны значения 2 логических f i (X , Xff.rn) .я О, (2 - 1), которые они принимают на некотором фиксированном наборе входных переменных к

1--г

Ч

хп. При этом для реализации 2 различных логических функций с помощью сигналов ,U-, , и,с производится соответствующая настройка мультиплексора на логическую Функцию fui( n-rn) после того, как значение логической функции f (х.,, х„) будет записано , в блок памяти.

На группу входов 5 устройства подаются гп информационных сигналов которые управляют работой мультиплексора 3 и подключают к выходу 8 устройства один из элементов памяти блока 2 памяти. В результате на выходе устройства формируется сигнал, значение которого определяется логическим выражением

Vm i п-т42 0 (VV) VmVm..(VV;;; - Vmi n-rr,42-% (VV)

n-m+l- n ln., (,)«

которое представляет собой разложение произвольной логической функции п переменных f (3(20) по переменным х„., х„.

Вычисление значения любого логического выражения на любом наборе входных переменных х., х , . . . , Х( в устройстве осуществляется за 2 тактов, на каждом из которых осуществляется настройка мультиплексора 1 на реализацию соответствующей логической функции в-т переменных f(x,2f,.) и запись значения функции в соответствующую ячейку блока памяти.

Схема предлагаемого устройства при п 10, m 5 и использовании мультиплексора 1 (фиг.2) и мультиплексора 3 (фиг.З) имеет сложность

по числу входов логических элементов, разную 600, что более чем в 10 раз проше схемы устройства-прототипа на 10 входов. В среднем данное устройство без учета сложности блока памяти в 2 раз проще устройства-прототипа для вычисления логических выражений.

Формула изобретения

Устройство для вычисления логических выражений п : переменных, содержащее два мультиплексора, выход первого мультиплексора является выходом устройства, управляющие входы первого мультиплексора подключены к «п информационным входам устройства, п -т информационные входы второго мультиплексора подключены к информационным входам устройства, управляющие входы которого подключены к управляющим входам второго мультиплексора, отличающее с я тем, что, с целью упрощения , устройство содержит блок памяти, входы записи которого подключены к выходу второго мультиплексора, а входы управления - к дополнительным управляющим входам устрой,ства, выходы блока памяти подключены К информационные входам первого, мультиплексора.

Источники информации, принятые во внимание при экспертизе

1.Якубайтис Э.А. Универсальные логические элементы. - Автоматика

s и вычислительная техника, 1 5, 1973, с. 14.

2.Малев В.А. Структурная избыточность в логических устройствгис. М., Связь, 1978, с. 124, рис. 2.8

0

(прототип)..

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления логических выражений @ переменных | 1982 |

|

SU1084782A1 |

| Устройство для вычисления логических выражений @ переменных | 1983 |

|

SU1119004A1 |

| ПОЛИНОМИАЛЬНЫЙ МОДУЛЯРНЫЙ ВЫЧИСЛИТЕЛЬ СИСТЕМ БУЛЕВЫХ ФУНКЦИЙ С ОБНАРУЖЕНИЕМ ОШИБОК | 2015 |

|

RU2586574C1 |

| Многофункциональный логический модуль | 1983 |

|

SU1109735A1 |

| Устройство для вычисления логических производных многозначных данных | 1989 |

|

SU1670690A1 |

| МОДУЛЯРНЫЙ ПОЛИНОМИАЛЬНЫЙ ВЫЧИСЛИТЕЛЬ СИСТЕМ БУЛЕВЫХ ФУНКЦИЙ | 2015 |

|

RU2586575C1 |

| Логический вычислитель в системе остаточных классов | 2016 |

|

RU2637488C1 |

| САМОПРОВЕРЯЕМЫЙ СПЕЦИАЛИЗИРОВАННЫЙ ВЫЧИСЛИТЕЛЬ СИСТЕМ БУЛЕВЫХ ФУНКЦИЙ | 2012 |

|

RU2485575C1 |

| МОДУЛЯРНЫЙ ВЫЧИСЛИТЕЛЬ СИСТЕМ БУЛЕВЫХ ФУНКЦИЙ | 2007 |

|

RU2373564C2 |

| Устройство для моделирования конечных автоматов | 1980 |

|

SU955080A1 |

fPuf.f

fPf/P.

М

2,

fm

Авторы

Даты

1982-09-30—Публикация

1981-01-04—Подача