Ё

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофункциональный запоминающий элемент для логической матрицы | 1983 |

|

SU1104584A1 |

| Многофункциональный элемент для логической матрицы | 1982 |

|

SU1037344A1 |

| ВЫЧИСЛИТЕЛЬНАЯ ОТКРЫТАЯ РАЗВИВАЕМАЯ АСИНХРОННАЯ МОДУЛЬНАЯ СИСТЕМА | 2009 |

|

RU2453910C2 |

| ОПЕРАЦИОННОЕ УСТРОЙСТВО ДЛЯ ПРОЦЕССОРА С АССОЦИАТИВНОЙ МАТРИЦЕЙ ОДНОРОДНОЙ СТРУКТУРЫ | 1984 |

|

RU2087031C1 |

| Ассоциативное запоминающее устройство | 1978 |

|

SU701349A1 |

| Ассоциативная запоминающая матрица | 1982 |

|

SU1112410A1 |

| Однокристальный микропроцессор | 1978 |

|

SU734695A1 |

| АССОЦИАТИВНЫЙ ПРОЦЕССОР | 1988 |

|

SU1521118A1 |

| Ассоциативный матричный процессор | 1982 |

|

SU1164720A1 |

| ЯЧЕЙКА ОДНОРОДНОЙ СТРУКТУРЫ | 2005 |

|

RU2300800C1 |

Изобретение относится к вычислительной технике и может быть использовано в матричных ассоциативных логических устройствах. Целью изобретения является упрощение модуля. Это достигается за счет замены арифметических и логических блоков блоком постоянной памяти. Модуль содержит триггер 1, мультиплексоры 2-4, элемент И 5. блок 6 постоянной памяти, а также входы управления записью, типом и видом операций. Модуль позволяет выполнять операции записи, считывания, сдвига информации, логические и арифметические операции между строками двух записанных в матрицу массивов данных. 1 ил.. 2 табл.

О

|Ь ю ел

N3 01

Изобретение относится к вычислительной технике и может быть использовано в матричных ассоциативных логических устройствах.

Цель изобретения - упрощение многофункционального запоминающего модуля и в связи с этим повышение его надежности и быстродействия.

На чертеже приведена схема модуля.

Многофункциональный запоминающий модуль содержит D-триггер 1, первый 2, второй 3 и третий 4 мультиплексоры, элемент И 5, блок б постоянной памяти.

На чертеже показаны также вход 7 управления записью, входы 7 стробирования модуля: в строке 8, в столбце 9 и в матрице 10; информационные входы 11-13, входы 14 и 15 переноса, входы 16 и 17 управления приемом информации, вход 18 задания типа операций, вход 19 считывания, входы 20 задания вида операций, выходы переноса 21 и информационый 22.

При построении логической матрицы осуществляются следующие соединения: входы 8 и 18 всех многофункциональных запоминающих модулей строки объединены и подключены к устройству управления матрицей (не показано). Выход 22 каждого модуля соединен с входом 11 предыдущего модуля, входом 12 последующего модуля в строке и входом 13 модуля, расположенного в столбце выше. Выход 21 соединен с входом 14 предыдущего модуля и входом 15 последующего модуля в строке. У модулей, расположенных в одном столбце, объединены входы 7, 9, 16, 17, 18, 20 и подключены к устройству управления матрицей. Входы 10 объединены у всех модулей. На вход 13 модулей нижней строки матрицы поступают входные данные. На свободные входы 11, 12, 14, 15 запоминающих элементов крайних столбцов поданы константы.

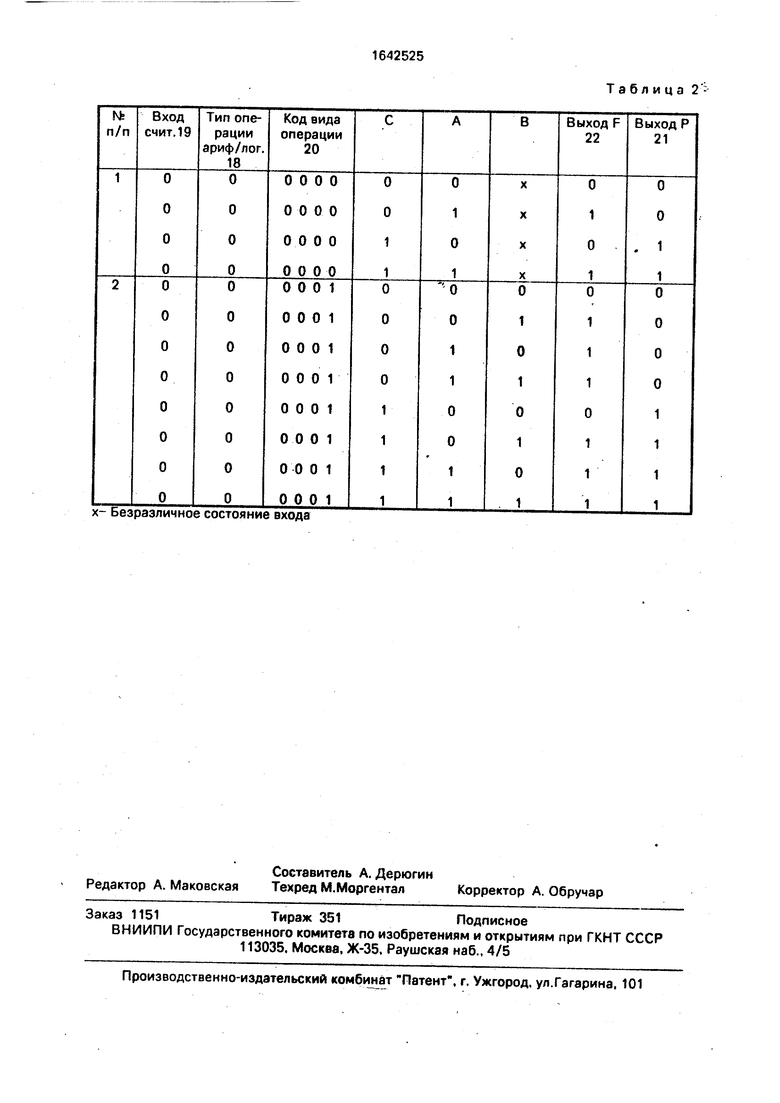

Работа устройства поясняется табл. 1, в которой приняты следующие обозначения: А - сигнал для выхода мультиплексора 3, В - содержимое триггера 1, С - сигнал переноса на выходе мультиплексора 4.

Во второй графе табл. 1 приведено значение сигнала на входе 19, в третьей - значение сигнала (тип операций арифметика/логика), подаваемого на вход 18, в четвертой, пятой, шестой и седьмой графах табл. 1 приведены коды операций, подаваемые на входы 20; соответствующие значения переменных С, А, В приведены в восьмой, девятой, десятой графах соответственно, значения результата операций на выходе 22 - в одиннадцатой графе, сигнала переноса на выходе 21 - в двенадцатой граПредложенное устройство работает следующим образом.

Запись информации в триггер 1 осуществляется при подаче строба записи на вход

0 22 данного элемента, при единичном - с выхода мультиплексора 3 (сигнал А), Сигнал А на входы 11-13 мультиплексора 3 поступает с выходов 22 соседнего левого, правого или нижнего модуля в зависимости

5 от кода на входах 16 и 17: 01, 10 или 11. Содержимое блока 6 (выход F, выход Р) в зависимости от кода адреса показано в табл 2. для пп. 1, 2 табл. 1.

Рассмотрим работу модуля в матрице.

0 Запись исходной информации можно осуществить тремя способами.

Первый способ. Информация подается на вход 13 нижней строки матрицы. На входы модулей подаются коды: входы 1, 17 5 11, вход 7 - 1, входы 20 - 0000, входы 18, 19 - О. При этом в каждом модуле сигнал проходит с входа 13 на выход 22 без изменения и одновременно поступает через мультиплексор 2 на вход триггера 1. Таким

0 образом, каждый разряд входной информации поступает на входы триггеров 1 всех модулей столбца, но запись производится только в ту строку и только в те разряды этой строки, на которые по входам 8 и 9 поданы

5 сигналы разрешения записи.

Второй способ. Первое слово исходной информации записывается в нижнюю строку матрицы. Затем с каждым тактом оно сдвигается вверх на одну строку, а в освобо0 дившуюся нижнюю строку записывается следующее слово. Управляющие сигналы, подаваемые на входы модулей матрицы, при этом следующие: входы 16, 17 - 11, вход 7 - 1, входы 18, 19 - О, входы 20 5 0101. Сигнал разрешения записи подается при этом на все модули матрицы. Разряды могут быть замаскированы подачей кода О на вход 8 модулей соответствующих столбцов. Этот способ позволяет записы0 вать входную информацию с тактовой частотой, ограниченной только задержкой на время срабатывания одного модуля матрицы.

Третий способ аналогичен предыдуще5 му, только запись происходит не снизу по словам, а слева и справа поразрядно. Первые разряды всех слов записываются в модули первого столбца матрицы, а затем сдвигаются. При этом в освободившийся первый столбец записываются следующие

разряды слов входной информации. Управляющие коды при этом такие же. как при втором способе, кроме входов 16, 17, на которые нужно подать код 01 или 10 в зависимости от того, слева или справа ведется запись информации в матрицу.

Считывание происходит следующим образом.

Информация с триггеров 1 данной строки матрицы проходит через все расположенные выше запоминающие элементы на выходы 22 верхней строки матрицы. Управляющие коды: входы 16, 17 - 11, входы 8, 9, 10,18 - О, входы 20 - 0000. На вход 19 считываемой строки подается код 1, на входы 19 остальных строк - код О. Если нужно считать всю информацию, записанную в матрице, то ее можно считывать пословно с выходов - 22 верхней строки матрицы, каждый раз сдвигая информацию на одно слово вверх,

Многофункциональный элемент выполняет операции над переменными А, В и С, приведенные в табл. 1, в соответствии с кодами, подаваемыми на входы 20 и 18. При подаче на вход 18 кода О выполняются логические операции согласно третьей графе таблицы, при этом сигнал С с входа мультиплексора 4 проходит на выход 21 без изменения. При коде 1 на входе 18 модуль выполняет арифметические операции, на выходах 22, 21 формируются сигналы согласно операциям в пятой и шестой графах таблицы.

Сигнал С - значение переноса из левого или правого соседнего разряда. Его прохождение определяется кодом на входе 17: 1 - проходит сигнал с входа 15,О - проходит сигнал с входа 14,

В матрице, построенной из предложенных многофункциональных запоминающих модулей, арифметические и логические операции выполняются попарно между соседними строками матрицы, в каждой из которых расположено одно слово. Результат операции запоминается на месте одного из операндов.

Рассмотрим выполнение таких операций на примере арифметического сложения. Первое слагаемое записывается в нечетные строки матрицы, второе - в четные. На входы 18 подается код 1. на входы 20- 1001. чему согласно строке 10 табл. 1 соответствует операция А ф В фС. На входы 19 нечетных строк матрицы поступает сигнал 1, Операция сложения в этих строках блокируется, вместо нее выполняется операция считывания. Информация с триггеров 1 нечетных строк поступает на выходы 22 и далее (управляющий код на

входах 16, 17 - 11) проходит на открытые- входы 13 модулей четных строк матрицы в качестве переменной А. На входах 19 четных строк - код О. В этих строках выпол5 няется операция сложения. Результат операции через мультиплексор 2 (на входах 7 - код 1) записывается в триггер 1 (разрешение записи подается на входы 9 всех столбцов и на входы 8 только четных строк).

0 Чтобы сложить несколько строк матрицы, надо на вход 19 нижней из них подать код 1, в ней будет выполняться операция считывания. На входы 19 остальных строк подается код О. В них будет выполняться

5 операция сложения А ф В Ф С, обусловленная подачей на входы 20 и 18 всех столбцов матрицы управляющих кодов 1001 и 1 соответственно, Управляющий код на входах 16, 17 - 11. Сигнал разрешения

0 записи подается на вход 8 верхней строки, куда записывается результат сложения. Остальные управляющие коды такие же, как при попарном сложении чисел.

Выполнение других арифметических и

5 логических операций отличается от опера- . ции сложения только управляющими кодами на входах 20, сигналами на входах 18, 19 и направлением передачи информационных сигналов А и переноса С многофункцио0 нального запоминающего элемента в зависимости от управляющих кодов на входах 16, 17.

Таким образом, предложенный многофункциональный запоминающий модуль

5 для логической матрицы позволяет выполнять операции записи, считывания, сдвига информации, логические и арифметические операции, перечисленные в табл. 1, между строками двух записанных в матрицу масси0 BOB данных.

Формула изобретения Многофункциональный запоминающий модуль для логической матрицы, содержа5 щий D-триггер, элемент И и три мультиплексора, причем С-вход D-триггерэ соединен с выходом элемента И, первый, второй и третий входы которого являются входами стро- бирования модуля в строке, в столбце и в

0 матрице соответственно, D-вход D-триггера соединен с выходом первого мультиш1ексо- ра, первый информационный вход которого является информационным выходом модуля, второй информационный вход соединен

5 с выходом второго мультиплексора, а управляющий вход является входом управления записью модуля, первый, второй и третий информационные входы второго мультиплексора являются соответствующими информационными входами модуля, а первый

и второй управляющие входы второго мультиплексора являются соответствующими входами управления приемом информации модуля, первый и второй информационные входы третьего мультиплексора являются соответствующими входами переноса модулей, а управляющий вход третьего мультиплексора соединен с вторым управляющим входом второго мультиплексора, отличающийся тем, что, с целью упрощения модуля, он содержит блок постоянной памяти, первый, второй и третий адресные входы

которого соединены соответственно с выходами D-триггера, второго и третьего мультиплексоров, четвертый, пятый, шестой и седьмой адресные входы являются входами задания вида операции модуля, восьмой и девятый адресные входы являются соответственно входом задания типа операции и входом считывания модуля, первый выход блока постоянной памяти соединен с первым информационным входом первого мультиплексора, а второй выход является выходом переноса модуля.

Таблица 1

х- Безразличное состояние входа

Таблица 2

| Запоминающий модуль для матричных блоков памяти | 1978 |

|

SU746728A1 |

| кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Механическая топочная решетка с наклонными частью подвижными, частью неподвижными колосниковыми элементами | 1917 |

|

SU1988A1 |

| Многофункциональный запоминающий элемент для логической матрицы | 1983 |

|

SU1104584A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1991-04-15—Публикация

1989-03-15—Подача