Изобретение относится к области автоматики и вычислительной техники и может быть использовано в цифровых системах управления и контроля.

Известен преобразователь временного интервала в двоичный код, содержащий генератор эталонной частоты, счетчик импульсов, элемент И,триггер управления и блок округления результата измерения 1 .

Недостатком устройства является узкий диапазон измеряемых интерваов.

Наиболее близким по технической сущности к предлагаемому- является преобразователь интервалов времени в двоичный код, содержащий генератор импульсов эталонной частоты, элемент И, триггер управления, воичный счетчик импульсов, причем выход генератора импульсов эталонной частоты подключен к первому входу элемента И, второй вход которого соединен с выходом триггера управления, единичный и нулевой входы которого подключены к входам Начало и Конец устройства,выход элемента И подключен к суммирующему входу двоичного счетчика, выход которого является выходом устройства С 2.

Однако такой преобразователь также не обеспечивает преобразования временных интервалов в широком диапазоне и обладает неодинаковой относительной точностью преобразования по всему диапазону временных интервалов.

Цель изобретения - расширение функциональных возможностей путём расширения диапазона преобразования временных интервалов в двоичный код при ограниченной разрядности п преобразования путем формирования двоичного п -разрядного кода в форме с плавающей запятой.

Указанная цель достигается тем, что в преобразователь временного интервала в двоичный код, содержа- щий генератор импульсов, п-разрядный счетчик, элемент И,триггер, единичный вход которого подключен к входу Начало временного интервала, а нулевой вход - к входу Конец временного интервала, единичный выход триггера подключен к первому входу элемента И, выход которого соединен со счетным входом п -разрядного счетчика, введены m -разрядный счетчик, группа из m +1 элементов И,элемент задержки, элемент ИЛИ, (m+l)-разрядный сдвигающий регистр, шифратор, выход которого является выходом порядка числа устройства, а входы подключены к выходам (т+1)-разрядного сдвигающего регистра и соответственно к первым

g входам элементов И группы, второй вход первого элемента И группы соединен с входом 1т -разрядного счетчика, выходы разрядов которого соединены соответственно с вторыми входами остальных элементов И группы, счетный вход m -разрядного счетчика соединен с выходом генератора импульсов, а вход сброса соединен с вторым входом элемента И и выходом элемента ИДИ, т + 1 входов которого соединены с выходами элементов И группы, вход Начало временного интервала устройства соединен с входами начальной установки гп+1)-разрядного сдвигающего регистра и сброса в нуль п -разрядного счетчик, выход п-го разряда которого соединен с входом управления сдвигом (т+1)-разр ядного сдвигающего регистра и входом элемента задержки, выход которого соединен с входом п-го разряда п-разрядного счетчика, выходы разрядов которого образуют выход мантиссы числа устройства.

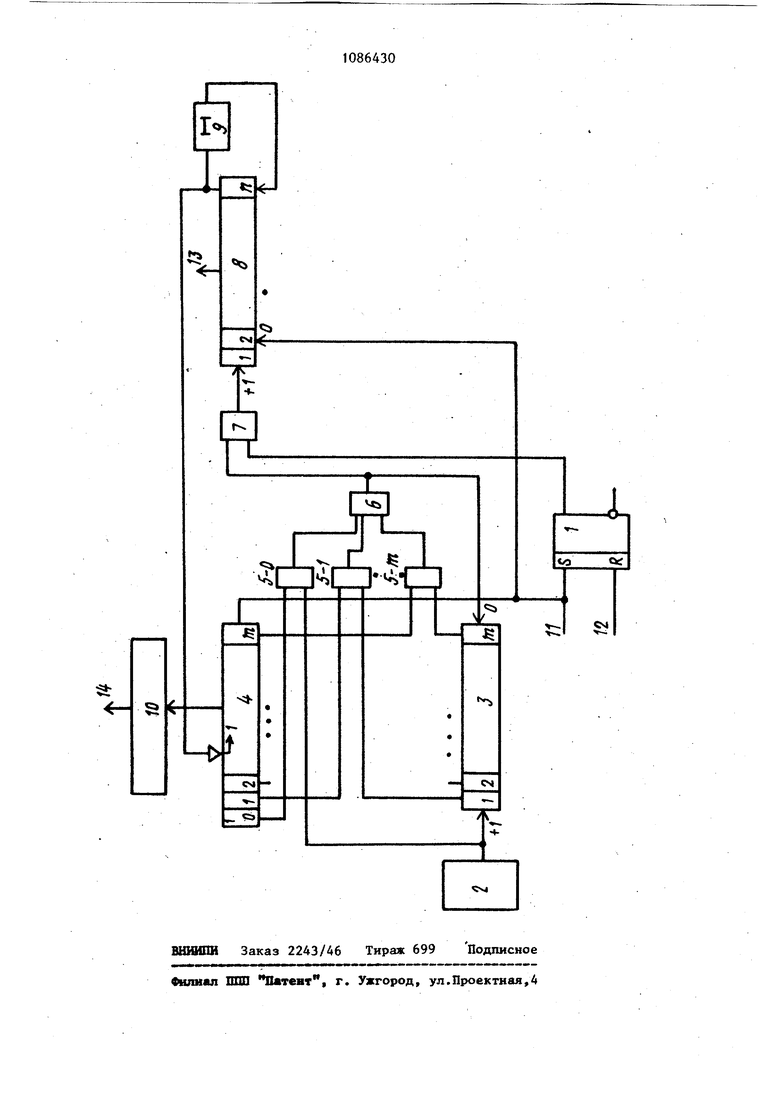

5 На чертеже представлена функциональная схема преобразователя временного интервала в двоичный код.

Схема содержит триггер 1, гене ратор 2 импульсов, m -разрядный счетчик 3, (т+1)-разрядный сдвигающий регистр 4, группу 5 элементов И, элемент 6 ИЛИ, элемент 7 И, п-разрядный счетчик 8, элемент 9

5 задержки, шифратор 10, входы 11 Начало временного интервала и 12 Конец временного интервала, выходы мантиссы 13 и порядка 14 двоичного кода.

Преобразователь работает следующим образом.

С поступлением импульса Начало временного интервала на вход 11 5 п-разрядный счетчик 8 обнуляется, все триггеры (т+1)-разрядного сдвигающего регистра 4, за исключением нулевого, устанавливаются в нулевое сосгояние, а триггер нулевого разряда m-разрядного сдвигающего регистра 4 и триггер 1 устанавливаются в единичное состояние. Импульсы с генератора 2 импульсов через первый элемент И группы 5 и элементы 6 ИЛИ и 7 И поступают на вход п -разрядного счетчика 8 и подсчитываются им. Эти же импульсы поступают на m -разрядньш счетчик 3, которьй также считает их. Единичные значения последующих разрядов m -разрядного счетчика поступают на входы оставшихся элементов И группы 5, которые в это время за крыты нулевыми значениями остальных разрядов (m+l)-разрядного сдвигающего регистра 4. Если в это время поступает импульс Конец временного интервала на вход 12, то триггер 1 устанавливается в нулевое состояние элемент 7И закрывается, счет прекращается, и с п-разрядного счетчика 8 на выходе 13 снимается код мантиссы числам а с шифратора 10 на выходе 14 - код нулевого порядка. Если же временной интервал продол жительный, то происходит переполнение tA-разрядного счетчика 8.Импульс переполнения с п -го разряда п-разрядного счетчика 8 поступает на сдвигающий вход регистра 4 и устанав ливает единицу в следующем (первом) разряде и нуль в предыдущем (нулевом) разряде. Этот же импульс через элемент з4держки 9 поступает на вход старшего разряда п -разрядного счетчика 8 и устанавливает его в еди ницу. Импульсы эталонной частоты че- рез m -разрядньй счетчик 3, второй элемент И группы 5 и з1лементы 6 ИЛИ, 7И поступают на вход п -разрядного счетчика 8 с частотой, умноженной на коэффициент 1/2, а на счетчике 8 формируется число, равное текущей длительности интервала с коэффициентом 1/2. На каждом втором такте -разрядный счетчик 3 обнуляется импульсом с элемента 6 ИЛИ. На протяжении первого цикла п -разрядного счетчика 8шифратор формирует порядок числа 1. Если же и в этом цикле п -разрядный счетчик 8 переполняется, то в (tn+1)разрядном регистре 4 устанавливается код 0010...О, что соответствует порядку 2, а счетчик 8 заполняется импульсами с частотой умноженной на коэффициент 2 число на счетчике 8 равняется значению интервала с коэффициентом 2 2 и т.д.: С приходом импульса Конец временного интервала на вход 12 триггер 1 переходит в нулевое состояние, элемент 7 И закрывается, и счет импульсов п -гразряднЫм счетчиком 8 прекращается. Мантисса числа снимается с выхода 13, а порядок - с выхода 14. Такая структ5Фа преобразователя позволяет получить на выходе двоичный код, представленный в форме плавающей запятой, что значительно сокращает разрядную сетку при преобразовании больших интервалов и обеспечивает прибилизительно постоянную относительную погрешность преобразования по всему диапазону измеряемых величин. .

I

Г

«5:«-J

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь временного интервала в двоичный код | 1986 |

|

SU1315973A2 |

| Преобразователь частоты в код | 1985 |

|

SU1356207A1 |

| Специализированный процессор обработки данных | 1982 |

|

SU1062715A1 |

| Устройство для деления чисел | 1981 |

|

SU1012241A1 |

| Устройство для сложения и вычитания чисел с плавающей запятой | 1980 |

|

SU959070A1 |

| Преобразователь напряжения в код | 1987 |

|

SU1427568A1 |

| Цифровой измеритель длительности одиночных импульсов | 1986 |

|

SU1318986A1 |

| Устройство для регистрации аналогового процесса | 1989 |

|

SU1774379A1 |

| Преобразователь двоичных чисел в двоично-десятичные числа | 1980 |

|

SU941990A1 |

| Устройство для преобразования частоты в код | 1977 |

|

SU661787A1 |

ПРЕОБРАЗОВАТЕЛЬ ВРЕМЕННОГО ИНТЕРВАЛА В ДВОИЧНЫЙ КОД, содержа1ЦИЙ генератор импульсов, h-разрядный счетчик, элемент И, триггер,единичный вход которого подключен к входу Начало временного интервала устройства, а нулевой вход - ко входу Конец временного интервала устройства, причем единичный выход триггера подключен к первому входу элемента И, выход которого соединен со счетным входом п-разрядного счетчика,отличающийся тем, что, с целью расширения функциональных возможностей путемрасширения диапазона преобразования временных интервалов в двоичный .код при ограниченной разрядности п преобразования путем формирования двоичного п -разрядного кода в форме плавающей запятой, в него введены ЦТ-разрядный счетчик, группа из т+1 элементов И, элемент задержки, элемент ИЛИ, (т+1)-разрядньй сдвигающий регистр, шифратор, выход которого является выходом порядка числа устройства, а входы подключены к выходам (т+1)-разрядного сдвигающего регистра и соответственно к первым входам элементов И группы, второй вход первого элемента И группы соединен с входом m-разрядного счетчика, выходы разрядов которого соединены соответственно с ВТОРЫМИ входами остальных элементов И группы, счетный вход m -раза S рядного счетчика соединен с выходом генератора импульсов, а вход (Л сброса соединен с вторым вхЬдом элемента И и выходом элемента ИЛИ, tn+1 входов которого соединены с выходами элементов И группы, вход Начало временного интервала устройства соединен с входами начальной установки (т+1)-разрядного сдвигающего регист00 С5 ра и сброса в нуль h-разрядного счетчика, выход h-го-разряда кото4 00 рого соединен с входом управления сдвигом (т+1)-разрядного сдвигающего регистра и входом элемента задержки, выход которого соединен с входом п-го разряда п-разрядного счетчика, выходы разрядов которого образуют выход мантиссы числа устройства.

03

r-

u

см

CN

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Авторское свидетельство СССР № | |||

| Преобразователь интервала времени в двоичный код | 1976 |

|

SU631913A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Гитис Э.И | |||

| Пискулов Е.А | |||

| Аналого-цифровые преобразователи, М., Энергоиздат, 1981, с | |||

| Топливник с глухим подом | 1918 |

|

SU141A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1984-04-15—Публикация

1983-01-11—Подача