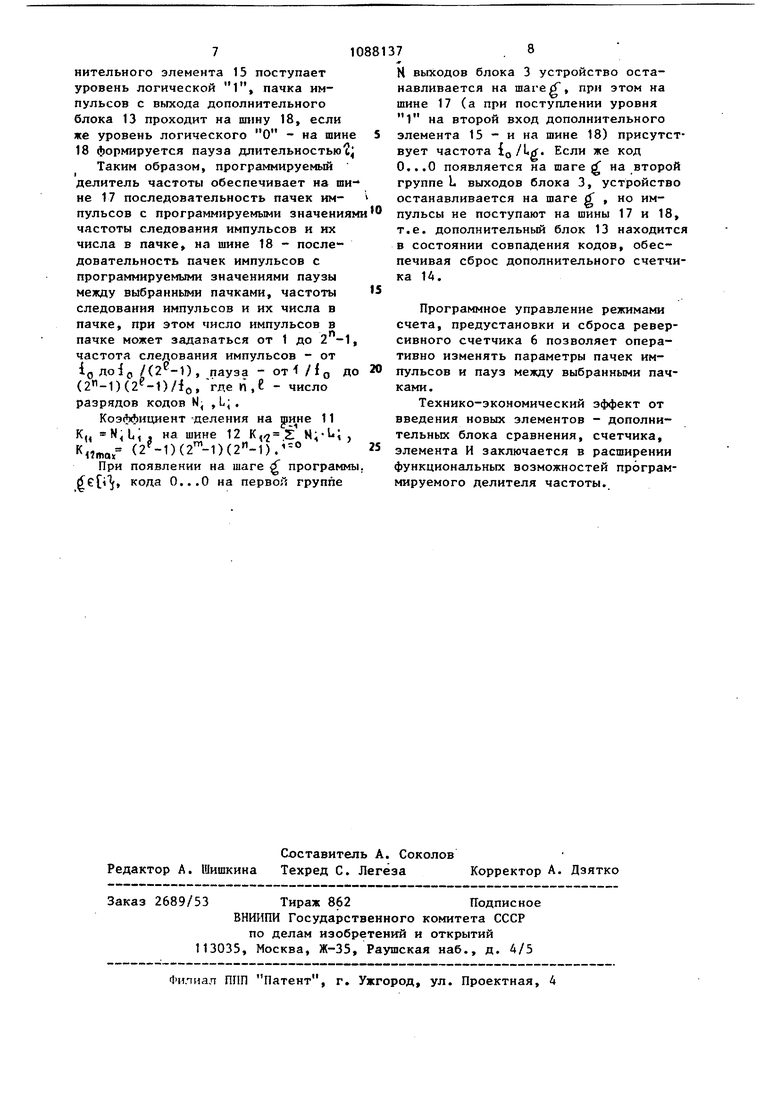

1 Изобретение отно.сится к импульсн технике. По основному авт.св. № 953742 известен программируемый делитель частоты, содержащий счетчик, информационный вход которого соединен с входной шиной, а выходы поразрядно соединены с первой группой входов блока сравнения, вторая группа входо которого соединена с группой входов блока контроля и группой N выходов блока памяти, входы которого соедине ны с выходами блока перезаписи, причем выход блока сравнения соединен с выходной шиной, входом управления счетчика и первым входом элемента И второй вход которого соединен с N -м выходом блока памяти и первым дополнительным входом блока контроля, второй дополнительный вход которого соединен с (М-1)-м выходом блока памяти, а также реверсивный счетчик, элемент ИЛИ и генератор одиночных импульсов, выход которого соединен с первым входом элемента ИЛИ, второй вход которого подключен к .выходу блока сравнения, а выход соединен с первым входом реверсивного счетчик второй вход которого соединен с выходом элемента И, третий вход подклю чен к (N-l)-My выходу блока памяти, четвертый вход соединен с выходом блока контроля и второй выходной шиной, а выходы реверсивного счетчика соединены с дополнительной группой входов блока памяти. Этот программируемьй делитель час тоты производит пересчет импульсов входной частоты с программируемыми коэффициентами деления на первой и второй выходной шине и оперативным и менением их значения m. Недостатком устройства является невозможность получения выходной последовательности пачек импульсов с программируемыми и изменяемыми значениями частоты следования импульсов и их числа в каяодой пачке, а также паузы между пачками импульсов. Целью изобретения является расширение функциональных возможностей программируемого делителя частоты путем обеспечения возможности получения выходной последовательности пачек импульсов с программируемыми и изменяемыми значениями паузы между пачками, частоты следования импульсо и их числа в каждой пачке. 37 Поставленная цель достигается тем, что в программируемьй делитель частоты, содержащий счетчик импульсов, информационный вход которого соединен с входной шиной, а выходы поразрядно соединены с первой группой входов блока сравнения, вторая группа входов которого соединена с группой входов блока контроля и группой N выходов блока памяти, входы которого соединены с выходами блока перезаписи, причем выход блока сравнения соединен с выходной шиной, входом управления счетчика импульсов и первым входом элемента И, второй вход которого соединен с N-M выходом блока памяти и первым дополнительным входом блока контроля, второй дополнительный вход которого соединен с (N-1)-M выходом блока памяти, реверсивный счетчик, элемент ИЛИ и генератор одиночных импульсов, выход которого соединен с первым входом элемента ИЛИ, второй вход которого подключен к выходу блока сравнения, а выход соединен с первым входом реверсивного счетчика импульсов, второй вход которого соединен с выходом элемента И, третий вход подключен к (N-l)-My выходу блока памяти, а четвертый вход соединен с выходом блока контроля и второй выходной шиной, а выходы реверсивного счетчика импульсов соединены с дополнительной группой входов блока памяти, введены дополнительные блок сравнения, счетчик импульсов и элемент И, причем первая группа входов дополнительного блока сравнения соединена с второй группой выходов блока памяти, вторая группа входов - с выходом дополнительного счетчика импульсов, информационный вход которого соединен с второй входной шиной, а вход управления - с выходом дополнительного блока сравнения, третьей выходной шиной и первым входом дополнительного элемента И, второй вход которого соединен с дополнитепьным выходом блока памяти, а выход - с четвертой выходной шиной. На чертеже приведена структурная электрическая схема программируемого делителя частоты. Устройство содержит счетчик 1 импульсов, выходы которого поразрядно соединены с первой группой входов блока 2 сравнения, вторая группа входов которого соединена с группой

31

N выходов блока 3 памяти, входы которого соединены с выходами блока 4 перезаписи, генератор 5 одиночных импульсов, реверсивный счетчик, 6 импульсов, элемент И 7,элемент ИЛИ 8, первый вход которого соединен с выходом генератора 5, второй вход которого соединен с выходом блока 2 и первым входом элемента 7. Выход элемента ИЛИ 8 соединен с первым входом реверсивного счетчика 6, второй вход которого соединен с выходом элемента 7, третий вход --с (Н-1)-м выходом блока 3, а четвертый вход - с выходо блока 9 контроля, первый дополнитель ный вход которого соединен с вторым входом элемента 7, второй дополнительный вход - с третьим входом реверсивного счетчика 6 импульсов, вторая группа входов блока 2 соединена с группой входов блока 9 и группой N выходов блока 3. Первая входная шина 10 соединена с информационньи входом счетчика 1. Первая выходная шина 11 соединена с выходом блока 2 и входом управления счетчика 1. Вторая выходная шина 12 соединена с выходом блока 9. Первая группа входо дополнительного блока 13 сравнения соединена с второй группой выходов блока 3, вторая группа входов - с выходом дополнительного счетчика 14, вход управления которого соединен с выходом дополнительного блока 13, с шиной 10 и первым входом дополнительного элемента И 15, второй вход которого соединен с дополнительным входом блока 3. Информационный вход дополнительного счетчика 14 импульсов соединен с второй входной шиной 16, вход управления которого соединен с третьей выходной шиной 17, а выход дополнительного элемента И 15 соединен с четвертой выходной шиной 18. .

Устройство работает следую1цим образом.

В режиме записи микрокоманд в работе находятся блоки 4 и 3, генерато 5, счетчик 6 импульсов, элемент 8. После сброса в исходное состояние в блок 3 на калсдом шаге программы, определяемом кодом на выходах реверсивного счетчика 6, по п выходам ввода от блока 4 записывается г -разрядный код N; , соответствующий требуемому коэффициенту деления на данном шаге, по ()му входу - логический уро374

вень управления реверсом, по (п+2)-м входу - логический уровень управлени предустановкой реверсивного счетчика 6. ,

Переход от -го на шаг осуществляется путем прохождения (l+1)-ro импульса на счетный вход счетчика 6 от генератора 5 через элемент 7, при этом в блоке 3 памяти запоминается код, находившийся на входах ввода микрокоманд непосредственно перед переходом на (+1)-й шаг.

По окончании формирования программы устройство переводится в режим исполнения программы, и в работе находятся счетчик 1, блок 2, реверсиный счетчик 6, элементы 7 -и 8, блок 9. При сбросе в исходное состояние и отсутствии предустановки реверсивного счетчика 6 оно находится на нулевом шаге, 0, на п выходах блока 3 устанавливается код NQ, и по шине 10 на вход счетчика 1 начинают поступать импульсы входной частоты. При достижении кодом на выходах счетчика 1 значения,равного NQ, на выходе блока 2 формируется логический уровень, сбрасывающий счетчик 1. Если на нулевом шаге в блоке 3 по Сп+1)-му входу ввода микрокоманд записи уровень управления реверсом, соответствующий прямому счету, а. по (П+2)-му - уровень, соответствующий нулевой предустановке, то в режиме исполнения программы счетчик 6, просчитав импульс управления с выход блока 2 через элемент 8, вызовет на выходах блока 3 код N , обеспечивающий переход блока 2 в состояние несовпадения кодов, разрешая тем самым счет импульсов счетчику 1. Программа автоматически переходит на первый шаг.

При записи микрокоманд на всех шагах импульс управления по окончании последнего шага перебросит реверсивный счетчик 6 из полностью заполненного состояния в нулевое, обеспечив переход программы на нулевой шаг и зацикливание программы с числом шагов, равным 2 . Если код N, постоянен на всех шагах программы,.устройство выполняет функции делителя частоты с коэффициентом пересчета

К„ N, const,

10 о 1

где N I ,,...,Z - 1. 510 При значении N. Ф const устройство осуществляет деление частоты импульсов с коэффициентом пересчета, изменяющимся по заранее заданной програм ме. При необходимости частичных изменений или полной замены программы устройство снова переводится в режим записи, и в блок 3 переписывается новая программа. При этом микрокоманды предьздущей программы стираются на выбранном шаге. Если на шаге ,( в блок 3 по (n + Dму входу ввода микрокоманд записан уровень управления реверсом, соответ ствующий обратному счету, в режиме исполнения программы очередной импульс управления переводит программу с ( -го на очередной импульс управления на (1-1)-й шаг, делая возможным вариации в программном изменении коэффициента пересчета К и расширяя функции программы. Запись по (п+2)-му входу ввода микрокоманд на шаге уровня предустановки реверсивного счетчика 6 дает возможность в режиме исполнения программы переводить программу на шаг (v+1+), где - величина предустановки в единицах младшего разряда реверсивного счетчика 6, и исполь зовать программу лишь на определенных шагах. При этом с выхода элемента 7 импульс поступает на шину предустановки только в случае йоявления импульса управления в конце -то шага. Если в блоке 3 на по П входам ввода микрокоманд записи код N равен коду на выходах счетчика 1 в сброшенном состоянии, то логический уровень сброса счетчика 1, появившийся на выходе блока 4 в результате совпадения кодов на вьпсодах блока 3 и счетчика t в конце (d-1)-r шага, остается таким независимо от дальнейшего состояния импульсов по шине 10 на входе счетчика 1, обеспечив однократное повторение программы с количеством шагов, равным. Блок 9 сработает при переходе программы на шаг ce{i, О в том случае, если только на этом шаге . по h входам ввода микрокоманд блока 3 записан колК(. 1, а по (П + 1)и (п+2)-му - уровни, равные соответственно уровням реверса и предустановки счетчика 6. 7 Сигнал с выхода блока 9 сбросит в исходное состояние реверсивньп счетчик 6, обеспечив цикличность работы устройства с количеством шагов, равным С, при отсутствии предустановки реверсивного счетчика 6 на шагах программы . Коэффициент пересчета делителя по шине 12 максимальное значение .1. () К Если в качестве входной шины вместо шины 10 используется только шина 16, устройство работает следующим образом. На каждом шаге программы i на первой группе N выходов, второй группе выходов и дополнительном выходе блока 3 присутствуют соответственно код N; , код li и уровень или 1гическогозаписанные в режиме записи по соответствующим входам блока 3 от блока 4. С приходом импульса частоты Iо на шину 16 дополнительный блок 13 оказывается в состоянии совпадения кодов, и на его выходе формируется импульс, поступающий на шину 17, первый вход дополнительного элемента 15, вход счетчика 1 и сбрасывающий по входу управления дополнительный счетчик 14, который переводит дополнительный блок 13 в состояние несовпадения кодов. Импульс на выходе блока 2, сбрасывающий счетчик 1 и поступающий на шину 11 и через элемент 8 на первый вход реверсивного счетчика 6, появляется в момент времени, когда на вход счетчика 1 поступило N импульсов следующих с частотой /U;, и на пгане 17 сформировалась пачка из импульсов, частота следования которых о /L, а длительность пачки L,/lo. импульсов С N; С приходом импульса на первый ход реверсивного счетчика 6 устройтво переходит на соответствующий аг программы на первой группе N выодов и на второй группе t выходов лока 3 появляются соответствующие начения кодов, задающие следующую ачку импульсов на шине 17 и т.д. Если на шаге i с дополнительного ыхода блока 3 на второй вход допол7нительного элемента 15 поступает уровень логической 1, пачка импульсов с выхода дополнительного блока 13 проходит на шнну 18, если же уровень логического О - на шин 18 формируется пауза длительностью Таким образом, программируемый делитель частоты обеспечивает на т не 17 последовательность пачек импульсов с программируемыми значени частоты следования импульсов и их числа в пачке, на шине 18 - последовательность пачек импульсов с программируемыми значениями паузы между выбранными пачками, частоты следования импульсов и их числа в пачке, при этом число импульсов в пачке может задаваться от 1 до 2 частота следования импульсов - от ig дoi(, /(), пауза - отf / f о ()()/io. где П,Е - число разрядов кодов N ,L;. Коэффициент -деления на шине 11 bi . на шине 12 К,,2 N;l«i к . Г9 -ПГ9 -1 Г7 -П о ()()(). При появлении на шаге програм tfcti, кода 0...0 на первой группе N выходов блока 3 устройство останавливается на шаге, при этом на шине 17 (а при поступлении уровня 1 на второй вход дополнительного элемента 15 - и на шине 18) присутствует частота ig /W. Если же код 0...0 появляется на шаге на второй группе L выходов блока 3, устройство останавливается на шаге , но импульсы не поступают на шины 17 и 18, т.е. дополнительный блок 13 находится в состоянии совпадения кодов, обеспечивая сброс дополнительного счетчика 14. Программное управление режимами счета, предустановки и сброса реверсивного счетчика 6 позволяет оперативно изменять параметры пачек импульсов и пауз между выбранными пачками. Технико-экономический эффект от введения новых элементов - дополнительных блока сравнения, счетчика, элемента И заключается в расширении функциональных возможностей программируемого делителя частоты.

| название | год | авторы | номер документа |

|---|---|---|---|

| Программируемый делитель частоты | 1980 |

|

SU953742A1 |

| Цифровой генератор функций | 1983 |

|

SU1108426A1 |

| Цифровой генератор синусоидальных колебаний | 1983 |

|

SU1133646A1 |

| Устройство для анализа логических состояний | 1980 |

|

SU1096648A1 |

| Устройство микропрограммного управления | 1984 |

|

SU1239715A1 |

| КОММУТАТОР ДЛЯ УПРАВЛЕНИЯ ШАГОВЫМ ДВИГАТЕЛЕМ | 1995 |

|

RU2103716C1 |

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1993 |

|

RU2079876C1 |

| Устройство для отладки и контроля микропроцессорных систем | 1988 |

|

SU1647568A1 |

| Микропроцессорное устройство для цифрового преобразования координат | 1982 |

|

SU1104523A1 |

ПРОГРАММИРУЕМЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ по авт.св. № 953742, отличающийся тем, что, с целью расширения его функциональных возможностей путем обеспечения возможности получения выходной последовательности пачек импульсов с программируемыми и изменяемыми значениями паузы между пачками, частоты следования импульсов и их числа в каждой пачке, в него введены дополнительные блок сравнения, счетчик импульсов и элемент И, причем первая группа входов дополнительного блока сравнения соединена с второй группой выходов блока памяти, вторая группа входов с выходом дополнительного счетчика импульсов, информационный вход которого соединен с второй входной шиной, а вход управления - с выходом дополнительного блока сравнения, третьей выходной шиной и первым входом дополнительного элемента И, второй вход, которого соединен с дополнительном выходом блока памяти, а выход - с (Л четвертой выходной шиной. ИЗОБРЕТЕНИЯ 1 ИсиШСТЕйА ЭО Оо :лэ ч1

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Программируемый делитель частоты | 1980 |

|

SU953742A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1984-04-23—Публикация

1982-12-23—Подача