1

Изобретение относится к .ли- гельной технике и может быть использовано в специ;1лизированных вычислителях в системах преобразования координат.,

Цель изобретения - расширение класса решаемых задач за счет обеспечения возможности вычисления квадратного корня из суммы квадратов двух аргументов и операции вйзведе- ния в квадрат одного аргумента, представленных число-импульсными кодами.

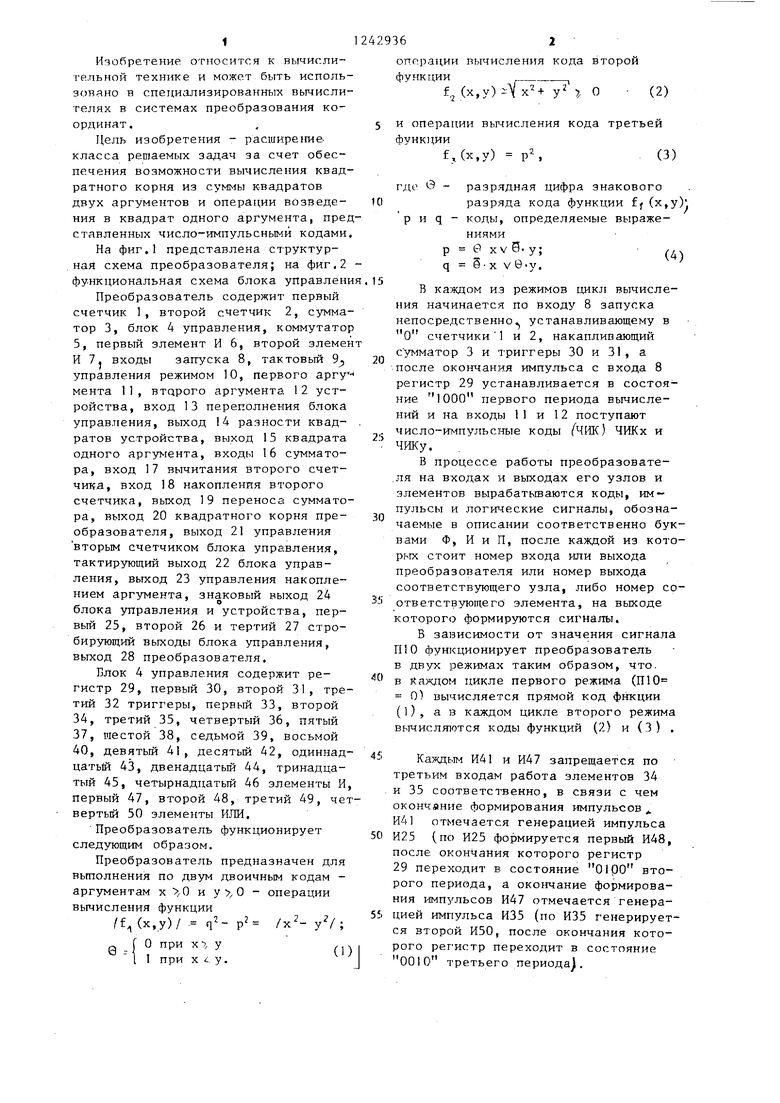

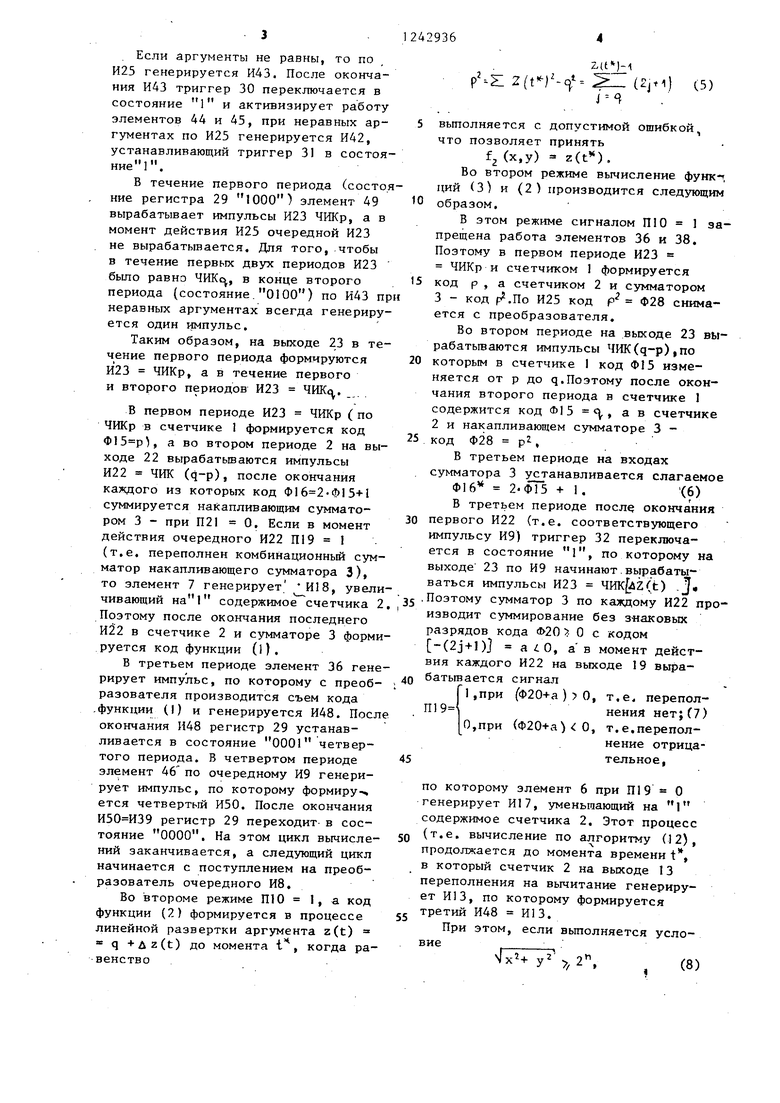

На фиг.1 представлена структурная схема преобразователя; на фиг.2 - функциональная схема блока управления

Преобразователь содержит первый счетчик 1, второй счетчик 2, сумматор 3, блок 4 управления, коммутатор 5, первый элемент И 6, второй злемент И 7. входы запуска 8, тактовый 9 управления режимом 10, первого apry -i мента 11, BTQporo аргумента 12 устройства, вход 13 переполнения блока управления, выход 14 разности квад- ратов устройства, выход 15 квадрата одного аргумента, входы 16 сумматора, вход 17 вычитания второго счетчика, вход 18 накопления второго счетчика, выход 19 переноса сумматора, выход 20 квадратного корня преобразователя, выход 21 управления вторым счетчиком блока управления, тактирующий выход 22 блока управления, выход 23 управления накоплением аргумента, знаковый выход 24 блока управления и устройства, первый 25, второй 26 и тертий 27 стро- бирующий выходы блока управления, выход 28 преобразователя.

Блок 4 управления содержит регистр 29, первый 30, второй 31, третий 32 триггеры, первый 33, второй 34, третий 35, четвертый 36, пятый 37, шестой 38, седьмой 39, восьмой 40, девятый 41, десятый 42, одиннад- цатьм 43, двенадцатый 44, тринадцатый 45, четырнадцатый 46 элементы И, первый 47, второй 48, третий 49, четвертый 50 элементы ИЖ.

Преобразователь функционирует следующим образом.

Преобразователь предназначен для вьтолнения по двум двоичным кодам - аргументам х ,0 и у , О - операции вычисления функции

f(x,y)/ . p yV;

x, у X i- у.

(1)

5

2429362

операции вычисления кода функции

f (х,у)

Х +

у

и операции вычисления кода третьей функции

f,(,y) pS (3)

где О - разрядная дифра знакового

разряда кода функции fj (х,у) р и q - коды, определяемые выражениями

р в XV В. у; q § X V 9 у.

(М

0 ;

0

5

0

В каждом из режимов цикл вычисления начинается по входу 8 запуска непосредственно устанавливающему в о счетчики 1 и 2, накапливающий с умматор 3 и триггеры 30 и 3 , а после окончания импульса с входа 8 регистр 29 устанавливается в состояние 1000 первого периода вычислений и на входы 1 и 12 поступают число-и мпульс1№1е коды /ЧИК) ЧИКх и ЧИКу.

В процессе работы преобразовате- .ля на входах и выходах его узлов и элементов вырабатьшаются коды, импульсы и логк -геские сигналы, обозначаемые в описании соответственно буквами Ф, И и П, после каждой из которых стоит номер входа или выхода преобразователя или номер выхода соответствующего узла, либо номер соответствующего элемента, на выходе которого формируются сигналы.

В зависимости от значения сигнала П10 функционирует преобразователь в ц,в}гк режимах таким образом, что. в каждом цикле первого режима (П10 0) вычисляется прямой код фнкции (1), а в каждом цикле второго режима вычисляются коды функций (2) и (3) .

Каждым И41 и И47 запрещается по третьим входам работа элементов 34 и 35 соответственно, в связи с чем окончание формирования импульсов И41 отмечается генерацией импульса

И25 (по И25 формируется первый И48, после окончания которого регистр 29 переходит в состояние 0100 второго периода, а окончание формирования 1 1мпульсов И47 отмечается генерацией импульса И35 (по И35 генерируется второй ИЗО, после окончания которого регистр переходит в состояние 0010 третьего периода).

Если аргументы не равны, то по И25 генерируется И43. После окончания И43 триггер 30 переключается в состояние 1 и активизирует работу элементов 44 и 45, при неравных ар- гументах по И25 генерируется И42, устанавливающий триггер 31 в состояние.

В течение первого периода (состоние регистра 29 1000) элемент 49 вырабатывает импульсы И23 ЧЖр, а в момент действия И25 очередной И23 не вырабатывается. Для того, чтобы в течение первых двух периодов И23 было равно ЧИКс, в конце второго периода {состояние.0100) по И43 п неравных аргументах всегда генерируется один импульс.

Таким образом, на выходе 23 в течение первого периода формируются И23 ЧИКр, а в течение первого и второго периодов И23 ЧИКс.

В первом периоде И23 ЧИКр ( по ЧЖр в счетчике 1 формируется код ), а во втором периоде 2 на выходе 22 вырабатьшаются импульсы И22 ЧИК (q-p), после окончания каждого из которых код Ф16 2-Ф15- -1 суммируется накапливающим сумматором 3 - при П21 0. Если в момент действия очередного И22 1119 1 (т.е. переполнен комбинационный сумматор накапливающего сумматора 3), то элемент 7 генерирует И18, увеличивающий содержимое счетчика 2 Поэтому после окончания последнего И22 в счетчике 2 и сумматоре 3 формируется код функции (l).

В третьем периоде элемент 36 генерирует импульс, по которому с преоб- разователя производится съем кода .функции (I) и генерируется И48. Посл окончания И48 регистр 29 устанавливается в состояние 0001 четвертого периода. В четвертом периоде элемент 46 по очередному И9 генерирует импульс, по которому формиру-ч ется четвертый ИЗО. После окончания регистр 29 переходит в состояние 0000. На этом цикл вычисле- НИИ заканчивается, а следующий цикл начинается с поступлением на преобразователь очередного ИВ.

Во второме режиме П10 1, а код функции (2) формируется в процессе линейной развертки аргумента z(t) q +uz(t) до момента t , когда равенство

Z(t)-1

2( - . (2jtl) (5) / Ч

выполняется с допустимой ошибкой, что позволяет принять

f2(x,y) zCt).

Во втором режиме вычисление функций (3) и (2) производится следующим образом.

В этом режиме сигналом П10 1 запрещена работа элементов 36 и 38. Поэтому в первом периоде И23 ЧИКр и счетчиком 1 формируется код р , а счетчиком 2 и сумматором 3 - код р .По И25 код р Ф28 снимается с преобразователя.

Во втором периоде на выходе 23 вы рабатьгеаются импульсы ЧИК(q-p),по которым в счетчике I код Ф15 изменяется от р до q.Поэтому после окончания второго периода в счетчике 1 содержится код Ь15 «., а в счетчике 2 и накапливающем сумматоре 3 - код Ф28 р,

В третьем периоде на входах сумматора 3 устанавливается слагаемо

Ф16 2.Ф15 + 1. (6)

В третьем периоде посл окончания первого И22 (т.е. соответствующего импульсу И9) триггер 32 переключается в состояние 1, по которому на выходе 23 по И9 начинают.вырабатываться импульсы И23 (С) .J .Поэтому сумматор 3 по каждому И22 призводит суммирование без з«аковых разрядов кода Ф20 О с кодом -(2J + 1) а i О, а в момент действия каждого И22 на выходе 19 выра- батьшается сигнал

1,при (Ф20+а ) О, т.е. переполнения нет;(7) О,при (Ф20+а):0, т.е.переполнение отрицательное,

по которому элемент 6 при П19 О генерирует И17, уменьшающий на 1 содержимое счетчика 2. Этот процесс (т.е. вычисление по алгоритму (12), продолжается до момента времени t, в который счетчик 2 на выходе 13 переполнения на вычитание генерирует И13, по которому формируется третий И48 И13.

При этом, если вьтолняется условие

, (8)

Х1х4 , 2,

то в некоторый момент времени 3 счетчик 1 переходит в состояние 1, соответствующем Ф15 2-1, и остается в данном состоянии до поступления на преобразователь очередного И8. Это осуществляется за счет того, что При условии (8 ) после перехода счетчика 1 в l он начинает по каждому И23 вырабатывать им- лульс переполнения на сложения, по , которому в счетчик 1 с его входов фиксированно заносится код (2 - 1), После око}гчания третьего И48 регистр 29 переходит в состояние четвертого периода, в котором по И9 генерируется И46,

По И46 вырабатывается И27 и производится съем с преобразователя кода Ф15 значения квадратного корня, а после окончания И48 регистр 29 переходит в состояние 0000. На этом цикле вычисление фнукций (.2) и (З) заканчивается, а следующий цикл начинается по очередному И8,

Формула изобретения

Цифровой функциональный преобразователь, содержащий первый счетчик, накапливающий сумматор, коммутатор и два элемента И, причем прямые выходы разрядов первого счетчика соединены с информационными входами первой группы коммутатора, выходы которого соединены со сдвигом на один разряд в сторону старших разрядов с информационными входами накапливающего сумматора, от.личающийся тем, что, с целью расширения, класса решаемых задач за счет обеспечения дополнительных возможностей выполнения операции извлечения квадратного корня из суммы квадратов двух аргументов и операции возведения в квадрат одного аргумента, в него введены второй счетчик и блок управления, содержащий регистр, три триггера,, четырнадцать элементов И и четыре элемента ИЛИ, причем входы запуска, управления режимом, первого аргумента, второго аргумента и тактовый вход преобразователя являются одно- 1 менными входами блока управления, тактирующий выход блока управления соединен с первыми входами первого и второго элементов И преобразователя и с синхронизирующим входом на

капливающего cyNfMaTopa, выход управления накоплением аргументов блока управления соединен со счетным входом: первого счетчика, вход сброса которого соединен с входами сброса накапливающего сумматора и второго счетчика и с входом запуска преобразователя, выход управления вторым счетчиком блока управления соединен с вторым входом первого злемен- та И преобразователя, с вторым инверсным входом второго элемента И преобразователя и с управляющим

входом: коммутатора, информационные входы второй группы которого соединены с инверсными выходами первого счетчика, выход Переполнения второго счетчика подключен к входу признака переполнения блока управления, выходы первого и второго элементов И преобразователя соединены с входами вычитания и суммирования второго счетчика соответственно, выход переноса накапливающего сумматора соединен с третьим инверсным входом первого элемента И преобразователя и , третьим входом второго элемента И преобразователя, вход младшего разряда накапливающего сумматора и входы записи первого счетчика соединены с шиной логической единицы преобразователя, выходы первого счетчика являются выходами квадратного корня преобразователя, выходы накапливающего сумматора и второго счетчика являются выходом разности квадратов и выходом квадрата одного аргумента преобразователя соответственно, знаковый выход блока управления является одноименным выходом преобразователя, первый, второй и третий стробирующие выходы блока управления являются выходом выборки значения квадрата одного аргумента, выходом выборки значения разности квадратов и выходом выборки значения квадратного кор:ня преобразователя соответственно, причем вход запуска блока управления соединен с входами сброса первого и второго триггеров и входом записи начального кода регистра, тактовый вход блока управления соединен с синхронизирующим входом третье:го триггера, с первыми входами с первого по пятый и четырнадцатого элементов И блока управления, вход управления режимом блока управления соединен с информационным

входом третьего триггера, первым инверсным входом шестого и первыми входами седьмого и восьмого элементов И, с вторым входом пятого элемента И и вторым инверсным входом четвертого элемента И, вход первого аргумента блока управления соединен с первыми входами девятого элемента И и перяого элемента ИЛИ, вход второго аргумента блока управления соединен с вторыми входами первого элемента ИЛИ и девятого элемента И и с первьм входом десятого элемента И, второй вход которого соединен с первым входом одиннадцатого элемента И и первьм стробирующим выходом блока управления, выходы десятого и одиннадцатого элементов И соединены с входами установки второго триггера и синхронизирующим входом первого триггера соответственно, информационный вход первого триггера соединен с шиной логической единицы преобразователя, выход второго триггера соединен со знаковым выходом блок а управления и является одноименным .выходом преобразователя, выход первого триггера соединен с первыми входами двенадцатого и тринадцатого элементов И, второй вход двенадцатого элемента И соединен с выходом первого элемента ИЛИ, с вторым инверсным входом третьего элемента И и с вторьм входом одиннадцатого элемента. И, второй вход тринадцатого элемента И соединен с выходом третьего элемента И и первым входом второго элемента ИЛИ, входы с второго по пятый которого соединены с выходами четырнадцатого элемента И, входом признака переполнения блока управления, выходом четвертого элемента И и выходом второго элемента И блока управления соответственно, выход

второго элемента ШШ соединен с синхронизирующим входом регистра, выход первого разряда которого соединен 5 с вторыми входами седьмого и второго элементов И блока управления, выход второго разряда регистра соединен с вторым входом шестого элемента И и третьим входом третьего элемента И, 10 выход третьего разряда регистра соединен с третьими входами четвертого и пятого элементов И, с инверсньм входом сброса третьего триггера и выходом управления вторым счетчи- 15 ком блока управления, выход четвертого разряда регистра соединен с вторьи входом четырнадцатого элемента И, выход которого соединен с вторым входом восьмого 0 элемента И, выход восьмого элемента И соединен с третьим стробирующим выходом блока управления, второй и первый стробирующие выходы которого соединены с выходами четвертого

5 и второго элементов И блока управления соответственно, выход управления накоплением аргументов блока управления соединен с выходом третьего элемента ИЛИ, и с третьими входа0 ми шестого и седьмого элементов И, входы с первого по четвертый которого соединены с выходами девятого, первого, двенадцатого и тринадцатого элементов И блока управления соот ветственно второй вход первого элемента И блока управления соединен с выходом третьего триггера, а выходы пятого, шестого и седьмого элементов И соединены с первым, вторым

0 и третьим входами четвертого элемента ИЛИ, выход которого является тактирующим выходом блока управления, выход девятого элемента И подключен к третьему инверсному входу второго элемента И блока управления.

Q}ia-1

ф(Л. I

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой преобразователь координат | 1983 |

|

SU1163322A1 |

| Цифровой преобразователь координат | 1985 |

|

SU1257638A1 |

| Цифровой преобразователь координат | 1979 |

|

SU873239A1 |

| Цифровой преобразователь координат | 1983 |

|

SU1141404A1 |

| Квадратор | 1983 |

|

SU1092501A1 |

| Цифровой преобразователь координат | 1979 |

|

SU842801A1 |

| Цифровой преобразователь координат | 1981 |

|

SU960834A1 |

| Цифровой преобразователь координат | 1985 |

|

SU1290307A1 |

| Генератор напряжений | 1990 |

|

SU1791956A1 |

| Генератор концентрических окружностей для телевизионного индикатора | 1983 |

|

SU1124373A1 |

Изобретение относится к вычислительной технике и позволяет вычислять как значения корня квадратного из суммы квадратов двух аргументов, так и разность квадратов двух аргументов и квадрат одного . Цифровой функциональный преобразователь содержит два счетчика, накапливающий сумматор, коммутатор, два элемента И и бдок управления. В первом режиме преобразователь вычисляет значения корня в каждом цикле вычис-i лений, во втором - значения разности квадратов и квадрат одновременно в каждом цикле вычислений. 2 ил. сл tc tc со 00 ф

| Устройство для вычисления разности квадратов двух чисел | 1978 |

|

SU780006A1 |

| Мельников А.А., Рыжевский А.Г., и Трифонов Е.Ф | |||

| Обработка частотных и временных импульсных сигналов.- М.: Энергия, 1976, с.89, рис.74. | |||

Авторы

Даты

1986-07-07—Публикация

1984-11-19—Подача