31499508

Изобретение относится к технике связи и может быть использовано для контроля качества каналов связи при пассивных и организованных помехах, а также при многолучевом распространении сигналов,

Цель изобретения - повьшение точности контроля.

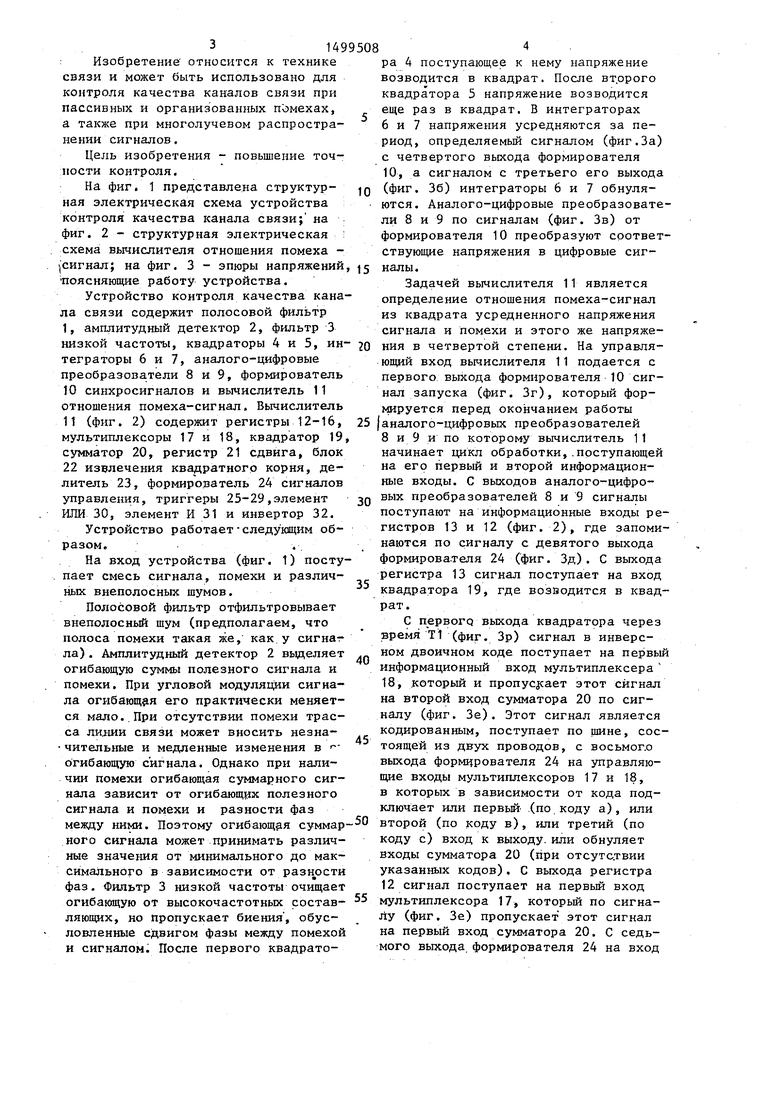

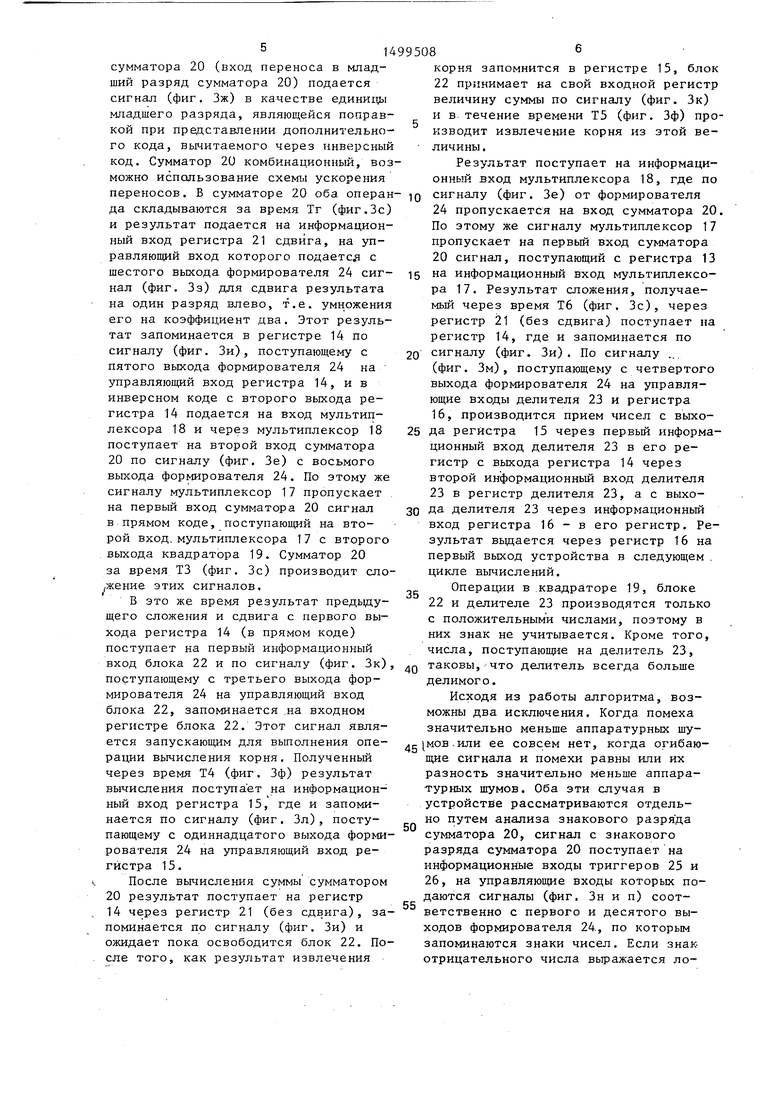

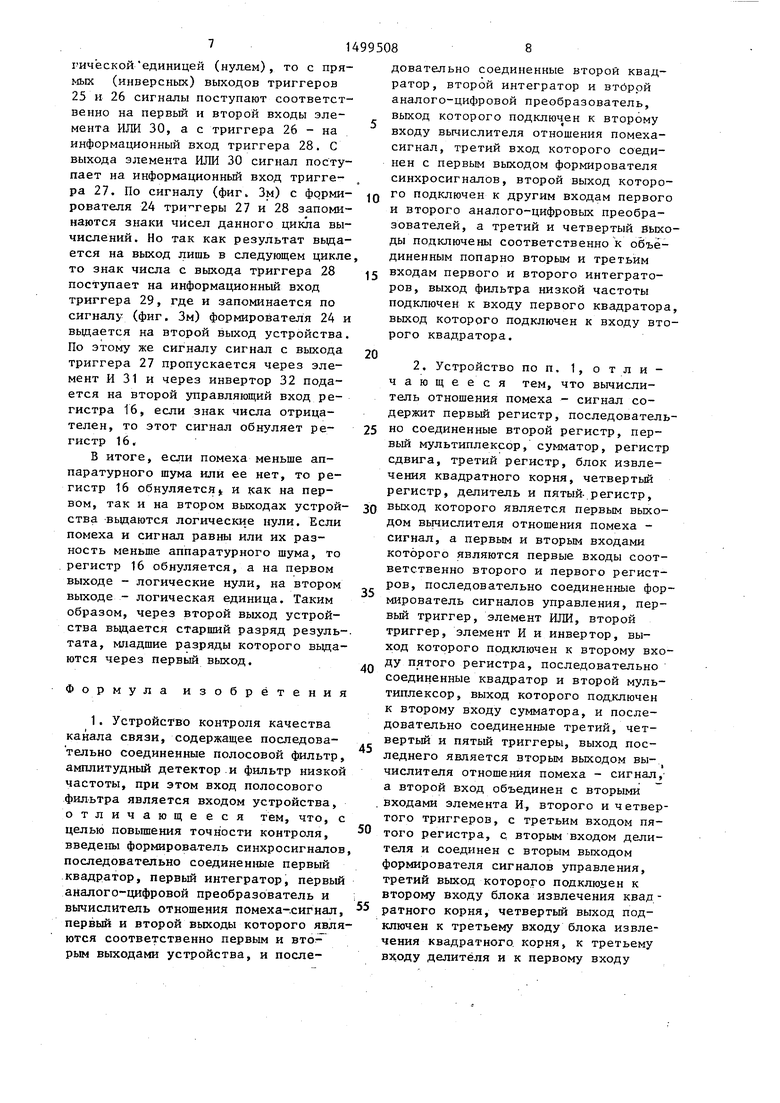

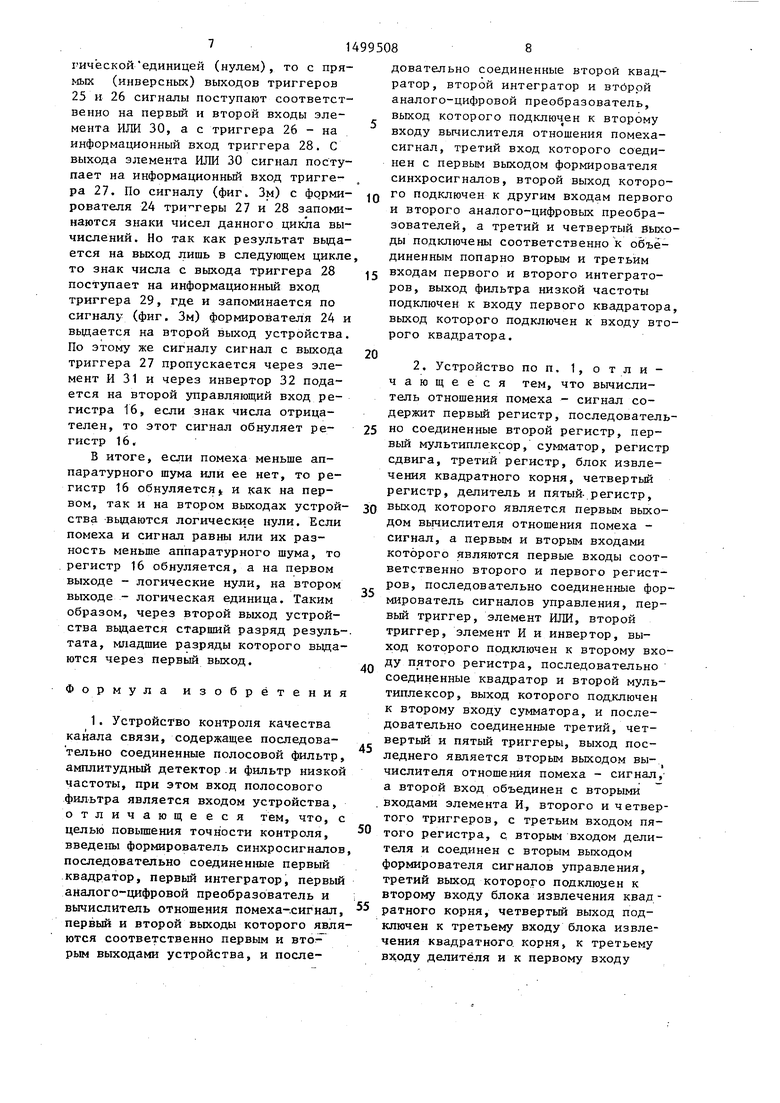

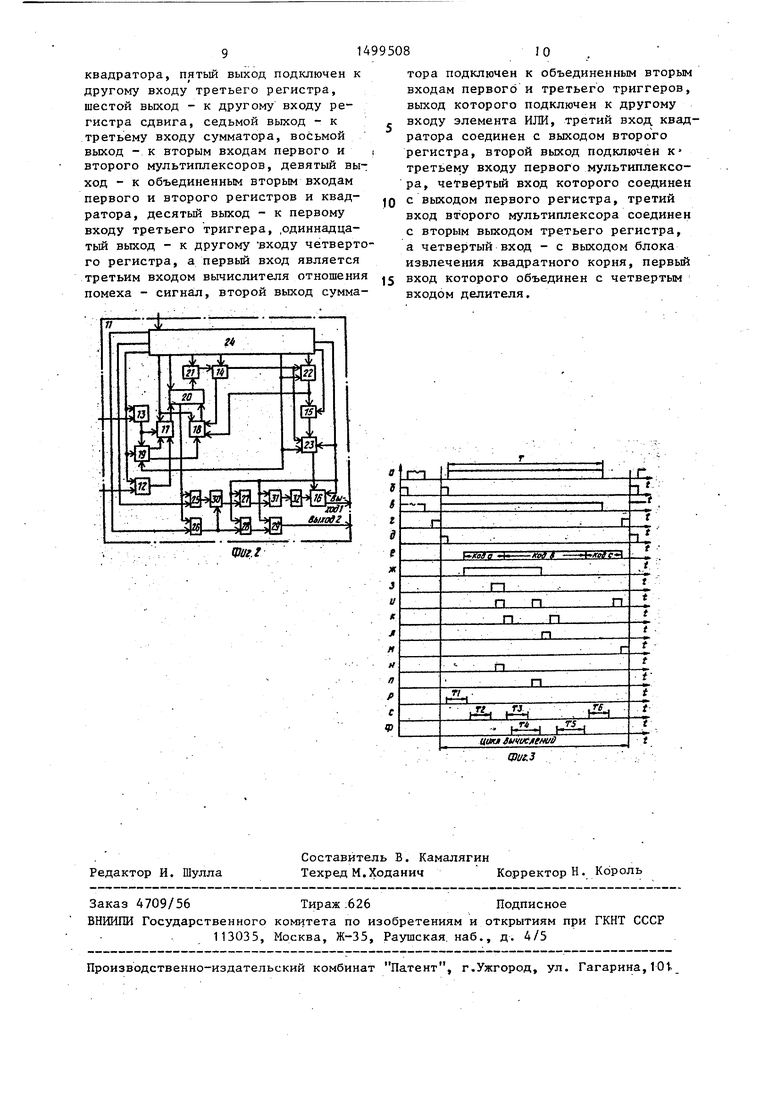

На фиг. 1 представлена структур- Q мая электрическая схема устройства контроля качества канала связи; на фиг. 2 - структурная электрическая : схема вьиислителя отношения помеха - сигнал; на фиг. 3 - эпюры напряжений, j поясняющие работу устройства.

Устройство контроля качества канаа связи содержит полосовой фильтр 1, амплитудный детектор 2, фильтр 3 низкой частоты, квадраторы 4 и 5, ин- jo теграторы 6 и 7, аналого-цифровые преобразователи 8 и 9, формирователь

10синхросигналов и вычислитель 11 отношения помеха-сигнал. Вычислитель

11(фиг. 2) содержит регистры 12-16, 25 j мультиплексоры 17 и 18, квадратор 19, су шатор 20, регистр 21 сдвига, блок

22 извлечения квадратного корня, делитель 23, формирователь 24 сигналов управления, триггеры 25-29,элемент зо ИЛИ 30, элемент И 31 и инвертор 32.

Устройство работает-следующим образом..

На вход устройства (фиг. 1) посту- пает смесь сигнала, помехи и различных внеполосных шумов.

Полосовой фильтр отфильтровывает внеполосньй шум (предполагаем, что полоса помехи такая же, как у сигнала) . Амплитудный детектор 2 выделяет .„ огибающую суммы полезного сигнала и помехи. При угловой модуляции сигнала огибающая его практически меняется мало.. При отсутствии помехи трасса связи может вносить незна- чительиые и медленные изменения в огибающую сигнала. Однако при наличии помехи огибающая суммарного сигнала зависит от огибающих полезного сигнала и помехи и разности фаз между ними. Поэтому огибающая суммар- ного сигнала может принимать различные значения от минимального до максимального в зависимости от paзнJOCти фаз. Фильтр 3 низкой частоты очищает огибающую от высокочастотных состав- ляющих, но пропускает биения , обусловленные сдвигом фазы между помехой и сигналом. После первого квадрато35

Q j

o

5 j

о

„

5

ра 4 поступающее к нему напряжение возводится в квадрат. После вт.орого квадратора 5 напряжение возводится еще раз в квадрат. В интеграторах 6 и 7 напряжения усредняются за период, определяемый сигналом (фиг.За) с четвертого выхода формирователя 10, а сигналом с третьего его выхода (фиг. 36) интеграторы 6 и 7 обнуляются. Аналого-цифровые преобразователи 8 и 9 по сигналам (фиг. Зв) от формирователя 10 преобразуют соответствующие напряжения в цифровые сигналы.

Задачей вычислителя 11 является определение отношения помеха-сигнал из квадрата усредненного напряжения сигнала и помехи и этого же напряжения в четвертой степени. На управляющий вход вычислителя 11 подается с первого выхода формирователя 10 сигнал запуска (фиг. Зг), который фор- ьшруется перед окончанием работы аналого-цифровых преобразователей 8 и 9 и по которому вычислитель 11 начинает цикл обработки,.поступающей на его первый и второй информационные входы. С выходов аналого-цифровых преобразователей 8 и 9 сигналы поступают на информационные входы регистров 13 и 12 (фиг. 2), где запоминаются по сигналу с девятого выхода формирователя 24 (фиг. Зд). С выхода регистра 13 сигнал поступает на вход квадратора 19, где возводится в квадрат.

С первого выхода квадратора через время Т1 (фиг. Зр) сигнал в инверсном двоичном коде поступает на первый информационный вход мультиплексера 18, .который и пропус сает этот сигнал на второй вход сумматора 20 по сигналу (фиг. Зе). Этот сигнал является кодированным, поступает по щине, состоящей из двух проводов, с восьмог.о вькода формирователя 24 на управляющие входы мультиплексоров 17 и 18, в которых в зависимости от кода подключает или первьй .(по коду а), или второй (по коду в), или третий (по коду с) вход к выходу, или обнуляет входы сумматора 20 (при отсутствии указанных кодов). С выхода регистра 12 сигнал поступает на первьй вход мультиплексора 17, которьй по сигналу (фиг. Зе) пропускает этот сигнал на первый вход сумматора 20. С седьмого выхода формирователя 24 на вход

сумматора 20 (вход переноса в младший разряд сумматора 20) подается сигнал (фиг, Зж) в качестве едини1 1 младшего разряда, являющейся поправкой при представлении дополнительного кода, вычитаемого через инверсный код. Сумматор 20 комбинационный, возможно использование схемы ускорения

корня запомнится в регистре 15, блок 22 принимает на свой входной регистр величину суммы по сигналу (фиг. Зк) и в течение времени Т5 (фиг. Зф) производит извлечение корня из этой величины.

Результат поступает на информационный вход мультиплексора 18, где по

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство контроля качества канала связи | 1988 |

|

SU1573543A1 |

| Устройство для контроля качества канала связи с шумоподобными сигналами | 1989 |

|

SU1628210A1 |

| Устройство для контроля отношения шум-сигнал | 1988 |

|

SU1518892A1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1993 |

|

RU2037842C1 |

| Цифровой измеритель задержки | 1980 |

|

SU930219A2 |

| Устройство для измерения фазовых сдвигов | 1984 |

|

SU1226341A1 |

| НАКОПИТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2089043C1 |

| Цифровой одноканальный инфранизкочастотный фазометр | 1987 |

|

SU1472831A1 |

| Генератор периодических колебаний инфразвуковых частот с автоматической калибровкой | 1987 |

|

SU1497722A1 |

| Устройство для приема дискретной информации | 1989 |

|

SU1619326A1 |

Изобретение относится к технике связи. Цель изобретения - повышение точности контроля. Устройство содержит полосовой фильтр 1, амплитудный детектор 2, фильтр 3 низкой частоты, квадраторы 4 и 5, интеграторы 6 и 7, АЦП 8 и 9, формирователь 10 синхросигналов и вычислитель 11 отношения помеха-сигнал. На вход устр-ва поступает смесь сигнала, помехи и различных внеполосных шумов. Фильтр 1 отфильтровывает внеполосный шум, затем детектор 2 выделяет огибающую суммы полезного сигнала и помехи. Фильтр 3 очищает огибающую от высокочастотных составляющих, но пропускает биения, обусловленные сдвигом фазы между помехой и сигналом. Затем напряжения преобразуются квадраторами 4 и 5 и усредн яются за период в интеграторах 6 и 7. Далее АЦП 8 и 9 преобразуют эти напряжения в цифровые сигналы, которые поступают в вычислитель 11, где определяется отношение помеха-сигнал. Если помеха меньше аппаратурного шума или ее нет, то на оба выхода устр-ва выдаются логические нули. Если помеха и сигнал равны или их разность меньше аппаратурного шума, то на первом выходе устр-ва будут логические нули, а на втором выходе - логическая единица. Т.обр. через второй выход устр-ва выдается старший разряд результата, младшие разряды которого выдаются через первый выход. 1 з.п. ф-лы, 3 ил.

переносов. Б сумматоре 20 оба операн- ю сигналу (фиг. За) от формирователя

/

да складываются за время Тг (фиг.3с) и результат подается на информационный вход регистра 21 сдвига, на управляющий вход которого подаете с шестого выхода формирователя 24 сигнал (фиг. За) для сдвига результата на один разряд влево, т.е. умножения его на коэффициент два. Этот результат запоминается в регистре 14 по сигналу (фиг. Зи), поступающему с пятого выхода формирователя 24 на управляющий вход регистра 14, ив инверсном коде с второго выхода регистра 14 подается на вход мультиплексора 18 и через мультиплексор 18 поступает на второй вход сумматора 20 по сигналу (фиг. Зе) с восьмого выхода формирователя 24. По этому же сигналу мультиплексор 17 пропускает на первый вход сумматора 20 сигнал в прямом коде, поступающий на второй вход, мультиплексора 17 с второго выхода квадратора 19. Сумматор 20 за время ТЗ (фиг. 3с) производит сложение этих сигналов.

В это же время результат предыдущего сложения и сдвига с первого выхода регистра 14 (в прямом коде) поступает на первый информационный вход блока 22 и по сигналу (фиг. Зк), поступающему с третьего выхода формирователя 24 на управляющий вход блока 22, запоминается .на входном регистре блока 22. Этот сигнал явля15

20

25

30

35

40

24 пропускается на вход сумматора 2 По этому же сигналу мультиплексор 1 пропускает на первый вход сумматора 20 сигнал, поступающий с регистра 1 на информационный вход мультиплексо ра 17. Результат сложения, получае- мьш через время Т6 (фиг, 3с), через регистр 21 (без сдвига) поступает н регистр 14, где и запоминается по сигналу (фиг. Зи) . По сигналу ... (фиг. 3м), поступающему с четвертог выхода формирователя 24 на управляющие входы делителя 23 и регистра 16, производится прием чисел с выхо да регистра 15 через первый информ ционный вход делителя 23 в его регистр с выхода регистра 14 через второй информационный вход делителя 23 в регистр делителя 23, а с выхода делителя 23 через информационный вход регистра 16 - в его регистр. Р зультат вьщается через регистр 16 н первый выход устройства в следующем цикле вычислений.

Операции в квадраторе 19, блоке 22 и делителе 23 производятся тольк с положительными числами, поэтому в них знак не учитывается. Кроме того числа, пocтyпaюшJie на делитель 23, таковы, что делитель всегда больше делимого.

Исходя из работы алгоритма, возможны два исключения. Когда помеха значительно меньше аппаратурных шузапускающим для выполнения one- мов.или ее совсем нет, когда огибаюется

рации вычисления корня. Полученный через время Т4 (фиг. Зф) результат вычисления поступает на информационный вход регистра 15, где и запоминается по сигналу (фиг, 3л), поступающему с одиннадцатого выхода формирователя 24 на управляющий вход регистра 15.

После вьиисления суммы сумматором 20 результат поступает на регистр 14 через регистр 21 (без сдвига), запоминается по сигналу (фиг. Зи) и ожидает пока освободится блок 22. После того, как результат извлечения

50

55

щие сигнала и помехи равны или их разность значительно меньше аппаратурных шумов. Оба эти случая в устройстве рассматриваются отдельно путем анализа знакового разряда сумматора 20, сигнал с знакового разряда сумматора 20 поступает на информационные входы триггеров 25 и 26, на управляющие входы которых подаются сигналы (фиг, Зн и п) соответственно с первого и десятого выходов формирователя 24., по которым запоминаются знаки чисел. Если знак- отрицательного числа выражается ло5

0

5

0

5

0

24 пропускается на вход сумматора 20. По этому же сигналу мультиплексор 17 пропускает на первый вход сумматора 20 сигнал, поступающий с регистра 13 на информационный вход мультиплексора 17. Результат сложения, получае- мьш через время Т6 (фиг, 3с), через регистр 21 (без сдвига) поступает на регистр 14, где и запоминается по сигналу (фиг. Зи) . По сигналу ... (фиг. 3м), поступающему с четвертого выхода формирователя 24 на управляющие входы делителя 23 и регистра 16, производится прием чисел с выхода регистра 15 через первый информационный вход делителя 23 в его регистр с выхода регистра 14 через второй информационный вход делителя 23 в регистр делителя 23, а с выхода делителя 23 через информационный вход регистра 16 - в его регистр. Результат вьщается через регистр 16 на первый выход устройства в следующем . цикле вычислений.

Операции в квадраторе 19, блоке 22 и делителе 23 производятся только с положительными числами, поэтому в них знак не учитывается. Кроме того, числа, пocтyпaюшJie на делитель 23, таковы, что делитель всегда больше делимого.

Исходя из работы алгоритма, возможны два исключения. Когда помеха значительно меньше аппаратурных шу0

5

щие сигнала и помехи равны или их разность значительно меньше аппаратурных шумов. Оба эти случая в устройстве рассматриваются отдельно путем анализа знакового разряда сумматора 20, сигнал с знакового разряда сумматора 20 поступает на информационные входы триггеров 25 и 26, на управляющие входы которых подаются сигналы (фиг, Зн и п) соответственно с первого и десятого выходов формирователя 24., по которым запоминаются знаки чисел. Если знак- отрицательного числа выражается ло71

1 ической единицей (нулем) , то с прямых (инверсных) выходов триггеров 25 и 26 сигналы поступают соответственно на первый и второй входы элемента ИЛИ 30, а с триггера 26 - на информационный вход триггера 28. С выхода элемента ИЛИ 30 сигнал поступает на информационный вход тригге- ра 27. По сигналу (фиг. 3м) с фррми- рователя 24 триггеры 27 и 28 запоминаются знаки чисел данного цикла вычислений. Но так как результат вьща- ется на выход лишь в следующем цикле то знак числа с выхода триггера 28 поступает на информационный вход триггера 29, где и запоминается по сигналу (фиг. 3м) формирователя 24 и вьщается на второй выход устройства По этому же сигналу сигнал с выхода триггера 27 пропускается через элемент И 31 и через инвертор 32 подается на второй управляющий вход регистра 16, если знак числа отрицателен, то этот сигнал обнуляет ре- гистр 16,

В итоге, если помеха меньше аппаратурного шума или ее нет, то регистр 16 обнуляется), и как на первом, так и на втором выходах устрой- ства вьщаются логические нули. Если помеха и сигнал равны или их разность меньше аппаратурного шума, то регистр 16 обнуляется, а на первом выходе - логические нули, на втором выходе - логическая единица. Таким образом, через второй выход устройства вьщается старший разряд результата, младшие разряды которого вьщаются через первый выход.

Формула изобретения

8

довательно соединенные второй квадратор, второй интегратор и втбррй аналого-цифровой преобразователь, выход которого подключ ен к второму входу вычислителя отношения помеха- сигнал, третий вход которого соединен с первым выходом формирователя синхросигналов, второй выход которого подключен к другим входам первого и второго аналого-цифровых преобразователей, а третий и четвертый выходы подключены соответственно к объединенным попарно вторым и третьим входам первого и второго интеграторов, выход фильтра низкой частоты подключен к входу первого квадратора выход которого подключен к входу второго квадратора.

квадратора, пятый выход подключен к другому входу третьего регистра, шестой выход - к другому входу регистра сдвига, седьмой выход - к третьему входу сумматора, восьмой выход - к вторым входам первого и второго мультиплексоров, девятый выход - к объединенным вторым входам первого и второго регистров и квадратора, десятый выход - к первому входу третьего триггера, .одиннадцатый выход - к другому ВХОДУ четвертого регистра, а первьш вход является третьим входом вьиислителя отношения помеха - сигнал, второй выход сумма

тора подключен к объединенным вторым входам первого и третьего триггеров, выход которого подключен к другому входу элемента ИЛИ, третий вход, квадратора соединен с выходом второго регистра, второй выход подключен К третьему входу первого мультиплексора, четвертый вход которого соединен с выходом первого регистра, третий вход второго мультиплексора соединен с вторым выходом третьего регистра, а четвертый вход - с выходом блока извлечения квадратного корня, первый вход которого объединен с четвертым входом делителя.

| Устройство синхронизации псевдослучайных сигналов | 1981 |

|

SU985961A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1989-08-07—Публикация

1987-05-19—Подача