1

Изобретение относится к области вычислительной техники, в частности к устройствам обмена, и может быть использовано в цифровых вычислительных машинах.

Известно устройство для обмена ij, содержащее коммутатор каналов, счетчик адресов, блок управления, блок приоритетного выбора каналов окончания обмена, блок приоритетного выбора каналов синхросигналов, коммутаторы и регистры связи.

Недостатком устройства является необходимость затрат большого количества оборудования.

Наиболее близким к изобретению по технической сущности и достигаемому положительному результату является устройство для обмена 2J, содержащее регистр данных, вход-выход которого соединен с шиной данных и с кодовым входом блока приоритетного формирования адреса, регистр адреса, выход которого соединен с шиной адреса, блок управления, выход которого соединен с управляющими входами регистров данных и адреса блока приоритетного формирования адреса, операционные блоки, входы-выходы которых соединены с первыми входами-выходс1ми

соответствующих коммутаторов, причем информационный вход устройства соединен с информационным входом регистра данных и первым информационным входом регистра адреса, первый, второй, третий выходы коммутаторов соединены соответственно с первым, вторым, третьим входами блока управления, вторые входы-выходы коммутаторов соединены с шиной данных, выход блока приоритетного формирования адреса соединен со вторым информационным входом регистра адреса, а выход регистра данных соединен с выходом уст5ройства.

Недостатком устройства является отсутствие возможности группового обращения к нескольким функциональным блокам и групповой обработки сигна0лов ответа, передаваемых по одной магистральной шине. В известном устройстве осуществляется лишь последовательное обращение к каждому функциональному блоку при обмене информации.

5 При групповом же обращении к нескольким функциональным блокам на магистральной шине сигналов ответа формируется ответ от наиболее быстродействующего блока. По этому сигналу через

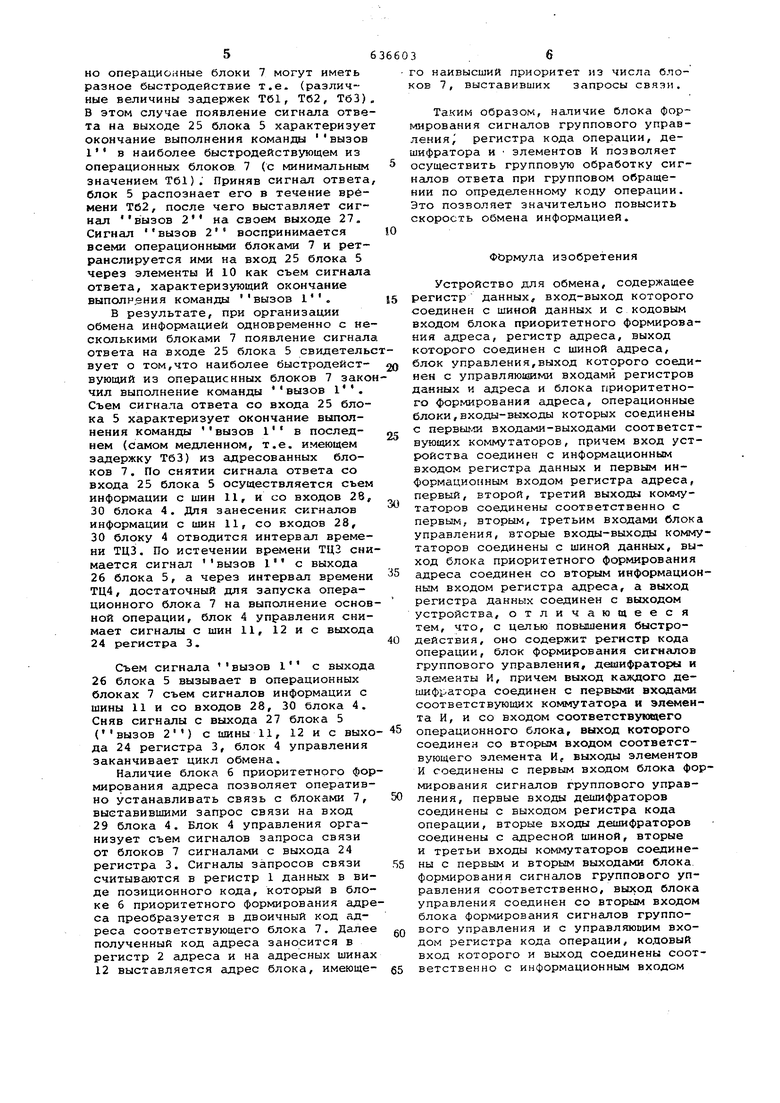

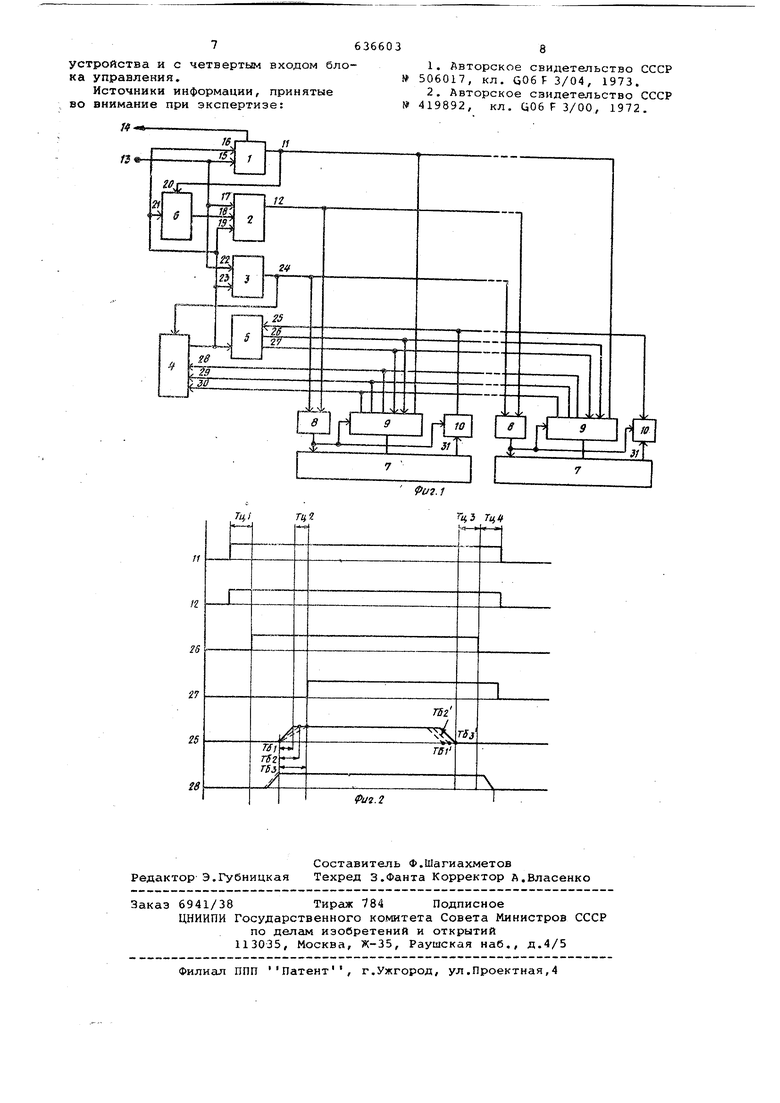

0 постоянную задержку производится за,86 несение (выдача) информации. Величина задержки определяется временным сдвигом ответа о приеме или выдаче информации от самого медленно реагирующего блока.Поэтому подстройка задержки под максимальное быстродействие блоков пр групповом обращении и магистральной шине сигнгипов ответа требует индивидуальной подгонки цепей связи и зависит от длины магистргши. Радиальный способ приема сигналов ответа приводит к увеличению числа шин по количеству функциональных блоков и дополнительным аппаратурным затратам Отсутствие возможности групповой обработки сигналов ответа не позволяет в известных устройствах осуществлять групповое обращение по программным сигналам одновременно к нескольким функциональным блокам, что снижает быстродействие устройства. . Цель изобретения - повышение быстродействия. Поставленная цель достигается тем что устройство содержит регистр кода операции, блок формирования сигналов группового управления, дешифраторы и элементы И, причем выход каждого дешифратора соединен с первыми входами соответствующих коммутатора и элемента И, и со входом соответствующего операционного блока, выход которого соединен со вторым входом соответствующего элемента И, выходы элементов И соединены с первым входом блока формирования сигналов группового управления, первые входы дешифраторов соеди 1ены с выходом регистра кода опе рации, вторые входы дешифраторов сое динены с адресной шиной, вторые и третьи входы коммутаторов соединены с первым и вторым выходами блока формирования сигналов группового управления соответственно, выход блока управления соединен со вторым входом блока формирования сигналов группового управления и с управляющим входом регистра кода операции, кодовый вход которого и выход соединены соответственно с информационным входом устройства и с четвертым входом блока управ ления. На фиг.1 приведена структурная схема .устройства, на фиг.2 - выходные и входные сигналы блоков. Устройство для обмена содержит (фиг. 1): регистр 1 данных, регистр 2 адреса, регистр 3 кода операции, блок 4 управления, блок 5 формирования сигналов группового управления, блок 6 приоритетного формирования адреса, операционные блоки 7, дешифраторы 8, коммутаторы 9, элементы И 10, шину И данных, адресную шину 12, вход 13, выход 14. Позициями 15-31 обозначены соответственно информационный и управ ляющий входы регистра данных, первый второй информационые и управляющий входы регистра адреса, кодовый и упавляющий входы блока приоритетного формирования адреса, информационный управляющий входы и выход регистра кода операции, вход и выходы блока ормирования сигналов группового упавления, входы блока управления, выод операционного блока. Устройство работает следующим образом. В начале цикла обмена блок 4 управления заносит соответственно в регистр 1 данных, регистр 2 адреса и в регистр 3 поступающие на вход 13 информационные, адресные и программные сигналы. Через задержку времени, достаточную для приема информации и регистры 1-3, блок 4 управления устанавливает ёщресные сигналы на шине 12, код операции на выходе 24 регистра 3, информационные - на шине 11. Адресные сигналы на шине 12 осуществляют адресный выбор одного из операционных блоков 7. Сигналы на выходе 24 регистра 3 определяют режим работы операционного блока 7. Через время ТЦ 1 (фиг.2),достаточное для окончания переходного, процесса опознавания блоками 7 присвоенных им адресов, а также подготовки соответствующих цепей, блок 5 устанавливает сигнал вызов 1 на выходе. Операционные блоки 7 принимают вызов 1 через коммута торы г,, в зависимости от кода в регистре 3, выполняют операции занесения информации с шин 11 или выдачи информации на шины 11, либо другие предусмотренные кодом операции, а также посылают соответствующие сигналы на входы 28, 30 блока 4. Занесение информации в операционные блоки 7, выдача информации из них и другие действия, предусмотренные сигналами на выходе 24 регистра 3, должны осуществляться в течение времени, не превышающего величину Тб (фиг.2). Величину Тб определяют для каждого конкретного блока 7 как суммарное время, достаточное для опознавания блоком 7 сигнала вызов 1, занесения информации в операционный блок 7 или выдачи информации блоком 7, а также выполнения других действий, предусмотренных сигналами на выходе 24 регистра 3. По истечении выдержки времени Тб, обеспечивающей завершение всех действий, выполняемых по сигналу вызов 1, блок 7 формирует на своем выходе 31 ответный сигнал, который, пройдя через элементы И 10, поступает на вход 25 блока 5. Наличие дешифраторов 8 позволяет организовать режим одновременной связи со всеми блоками 7. При этом, в зависимости от сигнала на выходе 24 регистра 3, осуществляется занесение информации или управление режимами, либо проверка состояний. Одновремен56но операционные блоки 7 могут иметь разное быстродействие т.е. (различные величины задержек Т61, Т62, ТбЗ). В этом случае появление сигнала ответа на выходе 25 блока 5 характеризует окончание выполнения команды вызов 1 в наиболее быстродействующем из операционных блоков 7 (с минимальным значением Т61). Приняв сигнал ответа, блок 5 распознает его в течение времени Тб2, после чего выставляет сигнал вызов 2 на своем выходе 27. вызов 2 Сигнал воспринимается всеми операционными блоками 7 и ретранслируется ими на вход 25 блока 5 через элементы И 10 как съем сигнала ответа, характеризующий окончание выполн,ения команды вызов 1. В результате, при организации обмена информацией одновременно с не сколькими блоками 7 появление сигнал ответа на входе 25 блока 5 свидетель вует о том,что наиболее быстродействующий из операционных блоков 7 зако чил выполнение команды вызов . Съем сигнала ответа со входа 25 блока 5 характеризует окончание выполнения команды вызов 1 в последнем (Самом медленном, т.е. имеющем задержку ТбЗ) из адресованных блоков 7. По снятии сигнала ответа со входа 25 блока 5 осуществляется съем информации с шин 11, и со входов 28, 30 блока 4. Для занесения сигналов информации с шин 11, со входов 28, 30 блоку 4 отводится интервал времени ТЦЗ. По истечении времени ТЦЗ сни мается сигнал вызов 1 с выхода 26 блока 5, а через интервал времени ТЦ4, достаточный для запуска операционного блока 7 на выполнение основ ной операции, блок 4 управления снимает сигналы с шик 11, 12 и с выхода 24 регистра 3. Съем сигнала вызов 1 с выхода 26 блока 5 вызывает в операционных блоках 7 съем сигнгипов информации с шины 11 и со входов 28, 30 блока 4. Сняв сигналы с выхода 27 блока 5 (вызов 2) с шины 11, 12 и с выхо да 24 регистра 3, блок 4 управления заканчивает цикл обмена. Наличие блока 6 приоритетного фор мирования адреса позволяет оперативно устанавливать связь с блоками 7, выставившими запрос связи на вход 29 блока 4. Блок 4 управления организует съем сигналов запроса связи от блоков 7 сигналами с выхода 24 регистра 3. Сигналы запросов связи считываются в регистр 1 данных в виде позиционного кода, который в блоке 6 приоритетного формирования адре са преобразуется в двоичный код адреса соответствующего блока 7. Далее полученный код адреса заносится в регистр 2 адреса и на адресных шинах 12 выставляется адрес блока, имеюще3го наивысший приоритет из числа блоков 7, выставивших запросы связи. Таким образом, наличие блока формирования сигналов группового управления регистра кода операции, дешифратора и злементов И позволяет осуществить групповую обработку сигналов ответа при групповом обращении по определенному коду операции. Это позволяет значительно повысить скорость обмена информацией. ФЬрмула изобретения Устройство для обмена, содержащее регистр данных, вход-выход которого соединен с шиной данных и с кодовым входом блока приоритетного формирования адреса, регистр адреса, выход которого соединен с шиной адреса, блок управления,выход которого соединен с управляющими входами регистров данных и адреса и блока приоритетного формирования адреса, операционные блоки,входы-выходы которых соединены с первыми входами-выходами соответствующих коммутаторов, причем вход устройства соединен с информационным входом регистра данных и первым информационным входом регистра адреса, первый, второй, третий выходы коммутаторов соединены соответственно с первым, вторым, третьим входами блока управления, вторые входы-выходы коммутаторов соединены с шиной данных, выход блока приоритетного формирования адреса соединен со вторым информационным входом регистра адреса, а выход регистра данных соединен с выходом устройства, отличающееся тем, что, с целью повышения быстродействия, оно содержит регистр кода операции, блок формирования сигналов группового управления, д аифраторы и элементы И, причем выход каждого дешифратора соединен с первыми входами соответствующих коммутатора и элемента И, и со входом соответствуювдего операционного блока, выход которого соединен со вторым входом соответствующего элемента И, выходы элементов И соединены с первым входом блока формирования сигналов группового управления, первые входы дешифраторов соединены с выходом регистра кода операции, вторые входы деишфраторов соединены с адресной шиной, вторые и третьи входы коммутаторов соединены с первым и вторым выходами блока формирования сигналов группового управления соответственно, выход блока управления соединен со вторым входом блока формирования сигналов группового управления и с управляющим входом регистра кода операции, кодовый вход которого и выход соединены соответственно с информационным входом устройства и с четвертьгм входом блока управления. Источники информации, принятые во внимание при экспертизе: 636603 № № 8 1.Авторское свидетельство СССР 506017, кл. G06F3/04, 1973. 2,Авторское свидетельство СССР 419892, кл. Ci06F3/00, 1972.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения системной и локальной магистралей. | 1988 |

|

SU1672460A1 |

| Устройство для обмена двухмашинного вычислительного комплекса | 1981 |

|

SU991403A1 |

| Модульная многоуровневая система коммутации процессоров | 1984 |

|

SU1249524A1 |

| Устройство для обмена информацией | 1979 |

|

SU842773A1 |

| Устройство микропроцессорного управления и обработки информации | 1979 |

|

SU947867A1 |

| Микропрограммный процессор со средствами быстрого прерывания | 1982 |

|

SU1116432A1 |

| Устройство для сопряжения электронно-вычислительной машины с группой внешних устройств | 1989 |

|

SU1734098A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1405063A2 |

| Устройство для управления обменом информацией между ЭВМ и группой периферийных устройств | 1989 |

|

SU1711170A2 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1278867A2 |

(/г. 1

Авторы

Даты

1978-12-05—Публикация

1976-06-28—Подача