ходом триггера, выходом второго элемента И-НЕ и вторым входом первого элемента И-НЕ,

3,Элемент поп.2,отлича ю Щ и и с я тем, что в разрядах распределителя с первого по К -ft выход соединен с установочным входом триггера, а вход сброса для разрядов распределителя с первого nok-Hсоединен с дополнительным входом сброса триггера, в К+1-м разряде распределителя выход соединен с прямым выходом триггера, а в последнем разряде вход сброса соединен

с дополнительным входом установки триггера.

4,Элемент поп.1,отличающ и и с я тем, что блок коммутации содержит три коммутатора, информационные входы которых соединены с информационным входом блока коммутации, входы переноса которого соединены с входами переноса первого и второго коммутаторов и выходом переноса третьего коммутатора, выходы переноса блока коммута11;ии соединены с выходами переноса первого и второго коммутаторов и входом переноса третьего коммутатора, а управляющие тины блока коммутации соединены с вьшодами управления коммутаторов.

5,Элемент по п.4, о т л и ч а ющ и и с я тем, что коммутатор содержит два элемента ЗАПРЕТ, элемент И-НЕ с инверсными входами и элемент И, выход которого соединен с выходом переноса коммутатора, информационный вход которого соединен с прямыми входами элементов ЗАПРЕТ и первым входом элемента И-НЕ с инверсными входами, второй вход и выход которог соединены соответственно с входом переноса коммутатора и первым входом элемента И, второй вход которого соединен с выходом первого элемента ЗАПРЕТ, вход переноса коммутатора соединен с инверсным входом второго элемента ЗАПРЕТ, а выводы управления коммутатора соединены с инверсньЕм входом первого элемента ЗАПРЕТ и выходом второго элемента ЗАПРЕТ.

6. Элемент поп.1,отличатщ и и с я тем, что блок сброса содержит элемент И, элемент ИЛИ и элемент ЗАПРЕТ, причем первый вход блока сброса соединен с первым входом элемента ИЛИ, выход которого соединен с первыми входами элементов И и ЗАПРЕТ, выходы которых соединены соответственно с первым и вторым выходами блока сброса, второй и третий входы которого соединены с вторым входом элемента И и вторым входом элемента ИЛИ, а второй инверсный вход элемента ЗАПРЕТ соеди -иен с ВТОРЫМ входом блока сброса.

| название | год | авторы | номер документа |

|---|---|---|---|

| Пороговый элемент | 1986 |

|

SU1387191A1 |

| Устройство для обнаружения ошибок в параллельном @ -разрядном коде с постоянным весом К | 1982 |

|

SU1149260A1 |

| Пороговый элемент | 1982 |

|

SU1083364A1 |

| Пороговый элемент | 1982 |

|

SU1092727A1 |

| Пороговый элемент | 1985 |

|

SU1297220A1 |

| Пороговый элемент | 1985 |

|

SU1297219A1 |

| Преобразователь кода системы счисления с одним основанием в код системы счисления с другим основанием | 1990 |

|

SU1741269A1 |

| Пороговое устройство | 1986 |

|

SU1368979A1 |

| Устройство для преобразования двоичного кода по модулю К | 1987 |

|

SU1587641A1 |

| Пороговый элемент | 1983 |

|

SU1126924A1 |

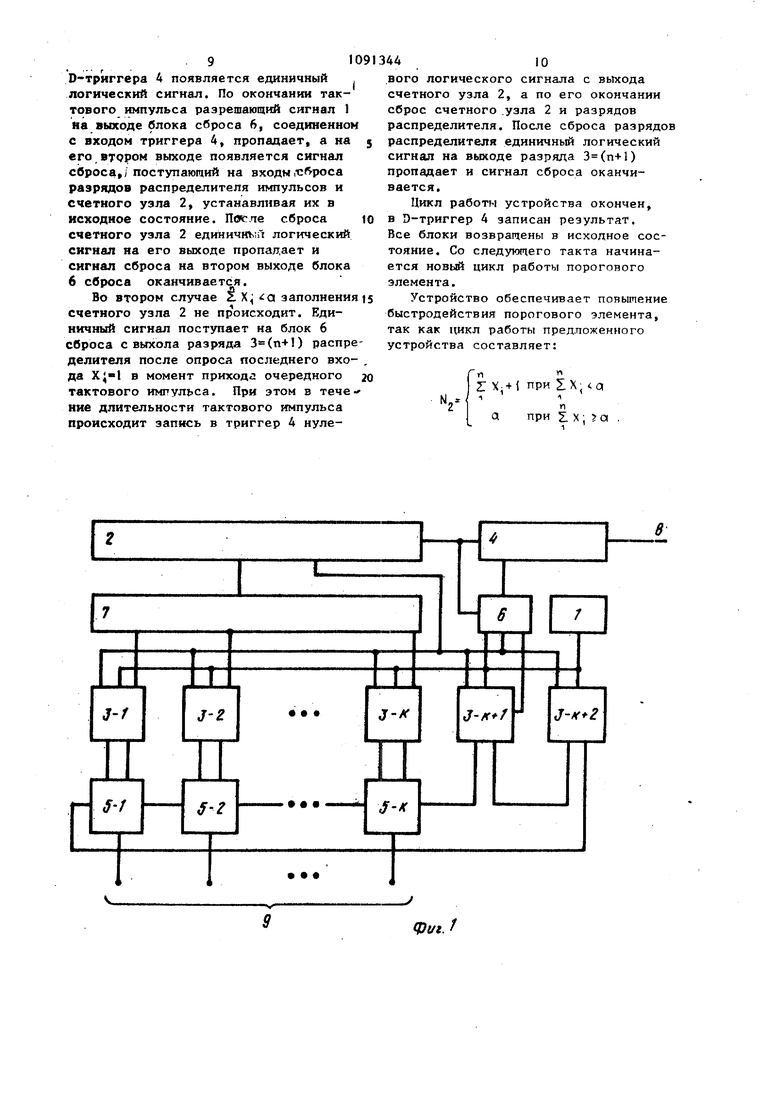

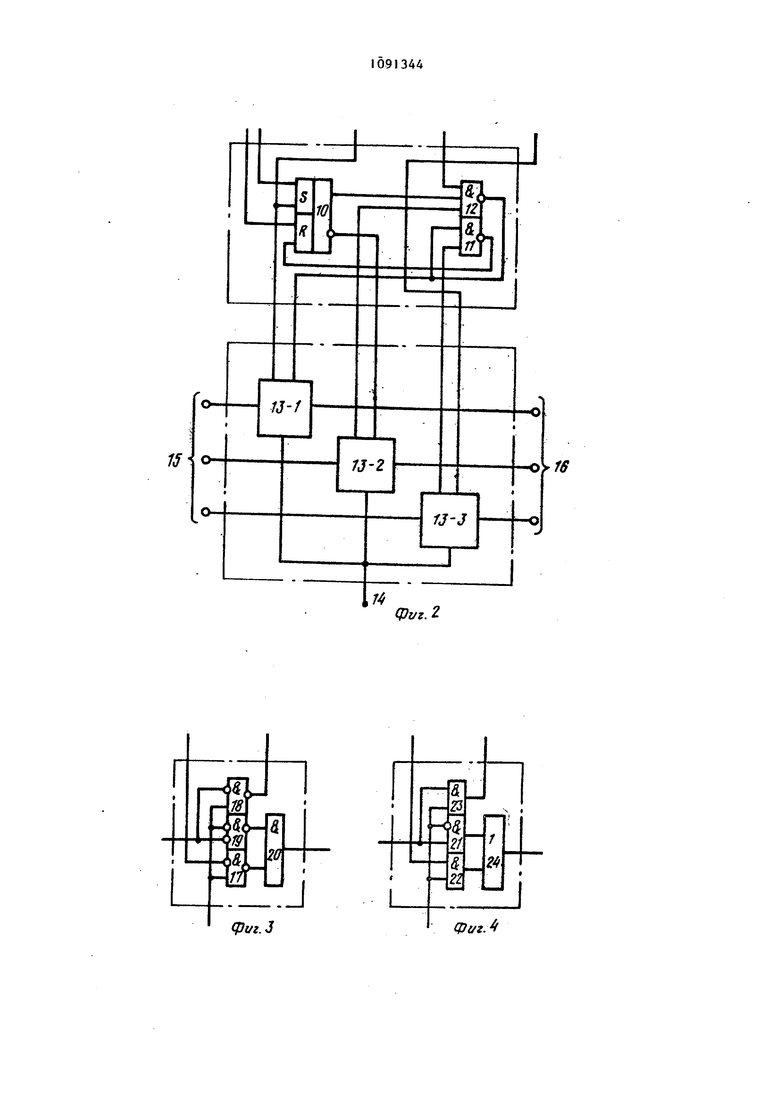

1. ПОРОГОВЬЙ ЭЛЕМЕНТ, содержащий генератор тактовых импульсов, счетный узел, К разрядов распределителя, где К - число входов, D -триггер и элемент ИЛИ, входы которого соединены с выходами разрядов распределителя, тактовые входы которых соединены с выходом генератора тактовых импульсов, а выход счетного узла соединен с D -входом D -триггера, выход которого соединен с выходом порогового элемента, о т личающий.ся тем, что, с. целью повышения быстродействия, в него введень К блоков -коммутаций, К +1-Й и К +2-Й разряды распределителя и блок сброса, первый и второй выходы которого соединены соответ ственно с тактовым входом D-триггера и входом сброса счетного узла,который соединен с входами сброса разрядов распределителя, тактовые входы k+1-го иК+2-го разрядов распределителя соединены с выходом генератора тактовых импульсов,счетный .ратора тактовых импульсов,счетный вход счетного узла соединен с выходом элемента ИЛИ, выход К+1-го разряда распределителя соединен с первым входом блока сброса, второй и третий входы которого соединены соответственно с выходом генератора тактовых импульсов и выходом счетного узла, входы порогового злемента соединены с информационными входами блоков коммутации, управляющие гаииы М-го блока коммутации, где 1, 2...,k , соединены с управляющими выводами М -го разряда распределителя, первые и вторые управляющие выводы К+1-ГО разряда распределителя соединены соответственно с выходами переноса К-го блока коммутации i и с первыми управляющими выводами К+2-ГО разряда распределителя, вто(Л рые управляющие выводы которого соединены с входами переноса первого блока коммутации, выходы переноса каяадого из блоков коммутации, кроме последнего, соединены с входами переноса следующего блока коммутаUD ции. 2, Элемент по п.1, отлича:о ющий с я тем, что разряд распре4:: делителя содержит триггер и два 4 элемента И-НЕ, причем выход первого элемента И-НЕ соединен с входом сброса триггера, прямой выход которого соединен с первым входом второго элемента И-НЕ, второй вход и выход которого соединены соответственно с тактовым входом разряда распределителя и первым входом первого эле мента И-НЕ, управляющие выводы разряда распределителя соединены с входом установки триггера, инверсным выходом триггера, третьим входом второго элемента И-НЕ, прямым вы

1

Изобретение относится к автоматике и вычислительной технике и может быть использовано для построения различных устройств обработки дискретной информации.

Известен пороговый элемент, содержащий генератор тактовых импульсов, сканирующий мультиплексор, состоящий из регистра сдвига, соединенного выходами с входами группы элементов И, вторые входы которых являются входами порогового элемента, а выходы соединены с входами элемента ИЛИ, выходы мультиплексора соединены с входом накопителя, состоящего из регистра сдвига или счетчика с детектором, и выходного триггера, информационньй вход которого соединен с выходом накопителя ij .

Недостатком этого порогового элемента является относительно низкое быстродействие,

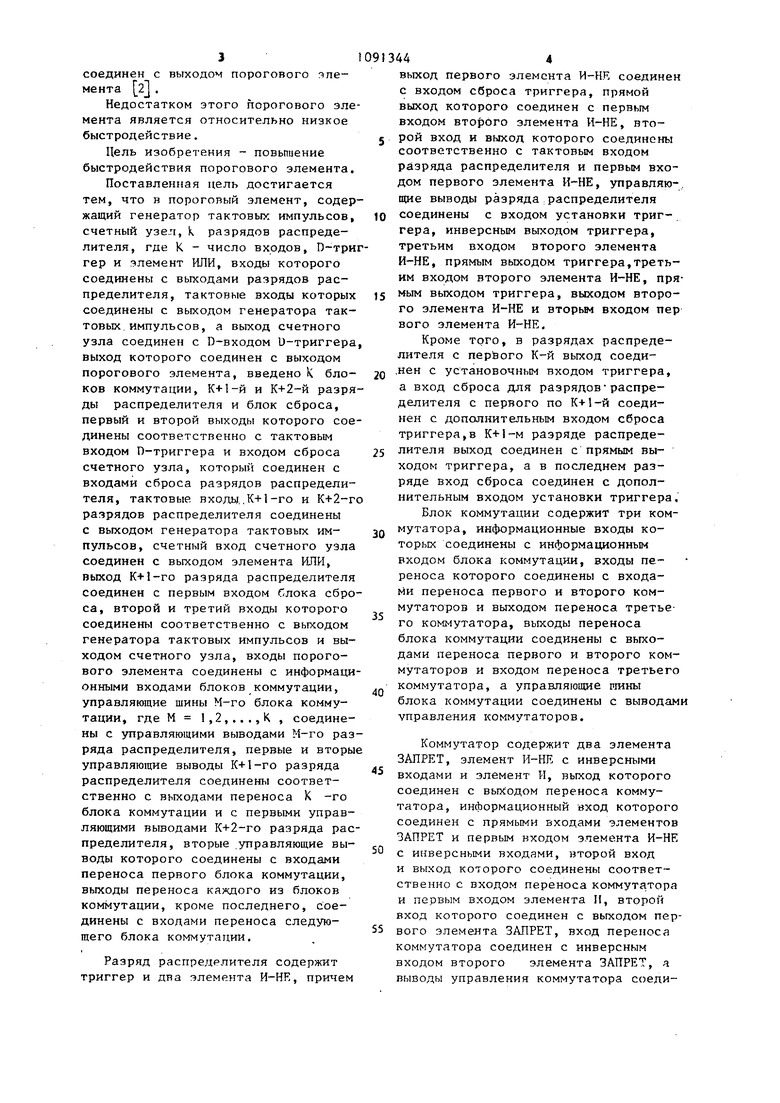

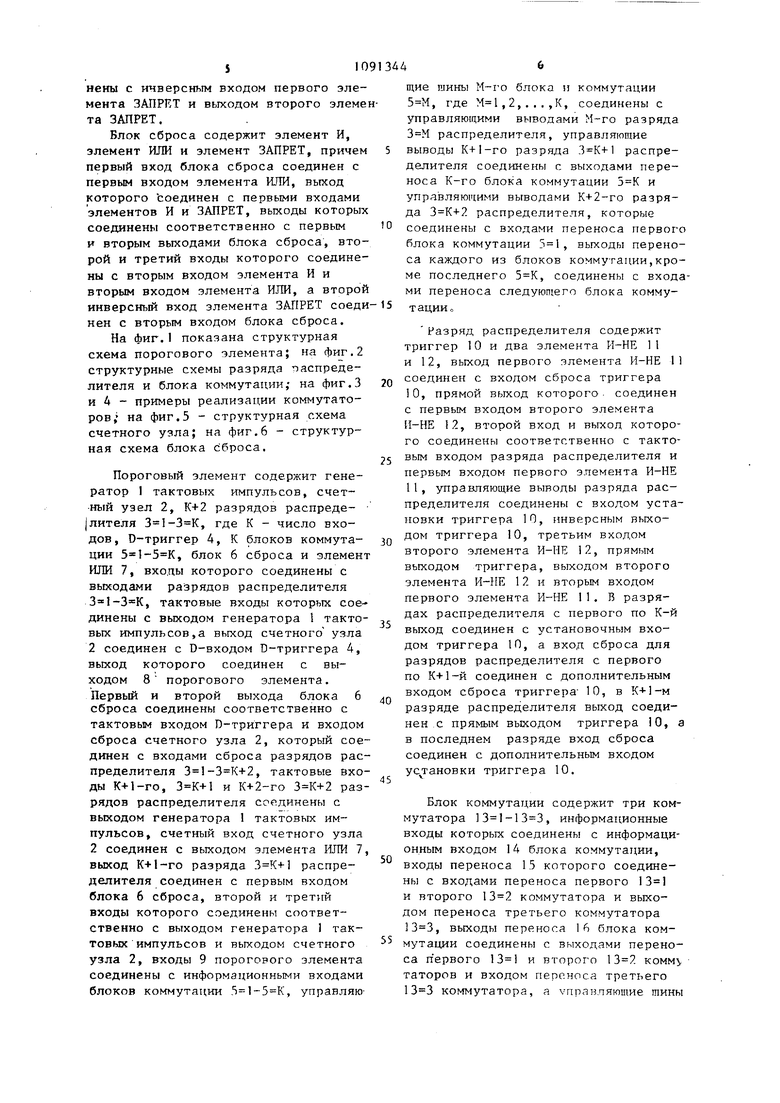

Наиболее близким техническим решением к предложенному является пороговый элемент, содержащий генератор тактовых импульсов, счетный узел, К разрядов распределителя, где К число входов, D-триггер и элемент ИЛИ, входы которого соединены с выходами разрядов распределителя,тактовые входы которых соединены с выходом генератора тактовых импульсов, а выход счетного узла соединен с D-входом D-триггсра, выход которого 3 соединен с выходом порогового элемента zj. Недостатком этого порогового эле мента является относительно низкое быстродействие. Цель изобретения - повьпиение быстродействия порогового элемента. Поставленная цель достигается тем, что в пороговый элемент, содер жащий генератор тактовых импульсов, счетный узел, k разрядов распределителя, где k - число входов, D-три гер и .элемент ИЛИ, входы которого соединены с выходами разрядов распределителя, тактовые входы которых соединены с выходом генератора тактовых, импульсов, а выход счетного узла соединен с D-входом U-триггера выход которого соединен с выходом порогового элемента, введено К блоков коммутации, К+1-й и К+2-й разря ды распределителя и блок сброса, первый и второй выходы которого сое динены соответственно с тактовым входом П-триггера и входом сброса счетного узла, который соединен с входами сброса разрядов распределителя, тактовые входы..К+1-го и К+2-г разрядов распределителя соединены с выходом генератора тактовых импульсов, счетный вход счетного узла соединен с выходом элемента ИЛР1, выход К+1-ГО разряда распределителя соединен с первым входом блока сбро са, второй и третий входы которого соединены соответственно с выходом генератора тактовых импульсов и выходом счетного узла, входы порогового элемента соединены с информаци онными входами блоков коммутации, управляющие шины М-го блока коммутации, где М ,2,...,К , соединены с управляющими выводами М-го раз ряда распределителя, первые и вторы управляющие выводы К+1-го разряда распределителя соединены соответственно с вьгходами переноса К -го блока коммутации и с первыми управляющими выводами К+2-ГО разряда рас пределителя, вторые управляющие выводы которого соединены с входами переноса первого блока коммутации, выходы переноса каждого из блоков коммутации, кроме последнего, соединены с входами переноса следующего блока коммутации. Разряд распределителя содержит триггер и два элемента И-НЕ, причем 44 выход первого элемента И-HR соединен с входом сброса триггера, прямой выход которого соединен с первым входом вто|зого элемента И-НЕ, второй вход и выход которого соединены соответственно с тактовым входом разряда распределителя и первым входом первого элемента , управляю-, щие выводы разряда : распределителя соединены с входом установки триггера, инверсным выходом триггера, третьим входом второго элемента Й-НЕ, прямым выходом триггера,третьим входом второго элемента И-НЕ, прямым выходом триггера, выходом второго элемента И-НЕ и вторьм входом пер вого элемента И-НЕ. Кроме того, в разрядах распределителя с перйого К-й выход соеди,нен с установочным входом триггера, а вход сброса для разрядовраспределителя с первого по К+5-Й соединен с дополнительным входом сброса триггера,в К+1-м разряде распределителя выход соединен с прямым выходом триггера, а в последнем разряде вход сброса соединен с дополнительным входом установки триггера, Блок коммутации содержит три коммутатора, информационные входы которых соединены с информационным входом блока коммутации, входы переноса которого соединены с входами переноса первого и второго коммутаторов и выходом переноса третьего коммутатора, выходы переноса блока коммутации соединены с вьгходами переноса первого и второго коммутаторов и входом переноса третьего коммутатора, а управляющие гаины блока коммутации соединены с выводами управления коммутаторов. Коммутатор содержит два элемента ЗАПРЕТ, элемент И-НЕ с инверсными входами и элемент И, выход которого соединен с выходом переноса коммутатора, информационный вход которого соединен с прямыми входами элементов ЗАПРЕТ и первым входом э.пемента И-НЕ с инверсными входами, второй вход и выход которого соединены соответственно с входом переноса коммутатора и первым входом элемента И, второй вход которого соединен с выходом первого элемента ЗАПРЕТ, вход переноса коммутатора соединен с инверсным входом второго элемента ЗАПРЕТ, а выводы управления коммутатора соедийены с инверсным входом первого элемента ЗАПРЕТ и выходом второго элеме та ЗАПРЕТ. Блок сброса содержит элемент И, элемент ИЛИ и элемент ЗАПРЕТ, причем первый вход блока сброса соединен с первым входом элемента ИЛИ, выход которого соединен с первыми входами элементов И и ЗАПРЕТ, выходы которых соединены соответственно с первым и вторым выходами блока сброса, второй и третий входы которого соединены с вторым входом элемента И и вторым входом элемента ИЛИ, а второй инверсный вход элемента ЗАПРЕТ соеди нен с вторым входом блока сброса. На фиг.1 показана структурная схема порогового элемента; на фиг.2 структурные схемы разряда паспределителя и блока коммутации,- на фиг.З и А - примеры реализации коммутаторов, на фиг.5 - структурная схема счетного узла; на фиг.6 - структурная схема блока сброса. Пороговый элемент содержит генератор 1 тактовых импульсов, счетный узел 2, К+2 разрядов распреде|лителя , где К - число входов, D-триггер 4, К блоков коммутации , блок 6 сброса и элемен ИЛИ 7, входы которого соединены с выходами разрядов распределителя , тактовые входы которых соединены с выходом генератора t тактовых импульсов,а выход счетного узла 2 соединен с D-входом D-триггера 4, выход которого соединен с выходом 8 порогового элемента. Первый и второй выхода блока 6 сброса соединены соответственно с тактовым входом D-триггера и входом сброса счетного узла 2, который сое динен с входами сброса разрядов рас пределителя , тактовые вхо ды K+l-ro, и К+2-ГО раз рядов распределителя соединены с выходом генератора 1 тактовых импульсов, счетный вход счетного узла 2 соединен с выходом элемента ИЛИ 7 выход К+1-ГО разряда распределителя соединен с первым входом блока 6 сброса, второй и третий входы которого соединены соответственно с выходом генератора I тактовых импульсов и выходом счетного узла 2, входы 9 порогового элемента соединены с информационными входами блоков коммутации , управляющие шины М-го блока и коммутации , где ,2,...,К, соединены с управляющими выводами М-го разряда распределителя, управляющие выводы К+1-ГО разряда распределителя соединены с выходами переноса К-го блока коммутации и управляющими выводами К+2-го разряда распределителя, которые соединены с входами переноса первого блока коммутации , выходы переноса каждого из блоков коммутации,кроме последнего , соединены с входами переноса следующего блока коммут ации о Разряд распределителя содержит триггер 10 и два элемента И-НЕ 11 и 12, выход первого элемента И-НЕ соединен с входом сброса триггера 10,прямой выход которого, соединен с первь м входом второго элемента И-НЕ 12, второй вход и выход которого соединены соответственно с тактовым входом разряда распределителя и первым входом первого элемента И-НЕ 11,управляющие выводы разряда распределителя соединены с входом установки триггера 10, инверсным выходом триггера 10, третьим входом второго элемента И-НЕ 12, прямым выходом триггера, выходом второго элемента И-НЕ 12 и вторым входом первого элемента И-НЕ II. В разрядах распределителя с первого по К-й выход соединен с установочным входом триггера 10, а вход сброса для разрядов распределителя с первого по К+1-Й соединен с дополнительным входом сброса триггера 10, в разряде распределителя выход соединен ,с прямым выходом триггера 10, а в последнем разряде вход сброса соединен с дополнительным входом установки триггера 10. Блок коммутации содержит три коммутатора , информационные входы которых соединены с информационным входом 14 блока коммутации, входы переноса 15 которого соединены с входами переноса первого и второго коммутатора и выходом переноса третьего коммутатора , выходы переноса 16 блока коммутации соединены с выходами переноса первого и второго 13 2 комм таторов и входом переноса третьего коммутатора, а управляющие гаины

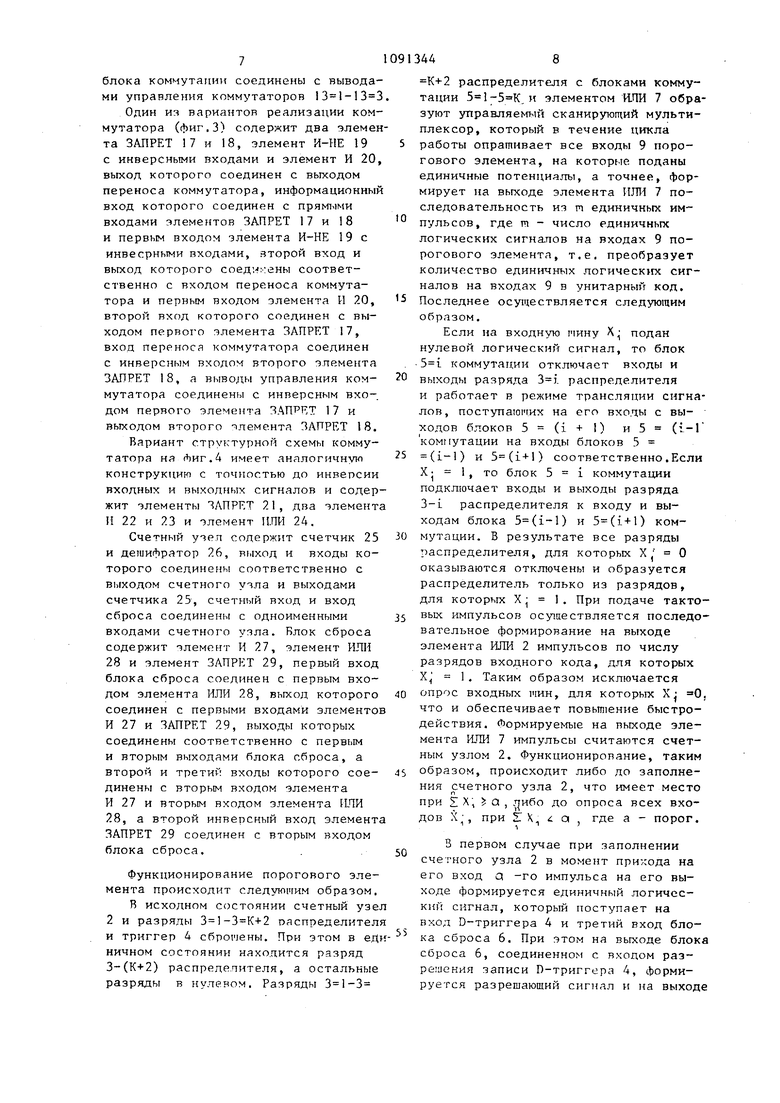

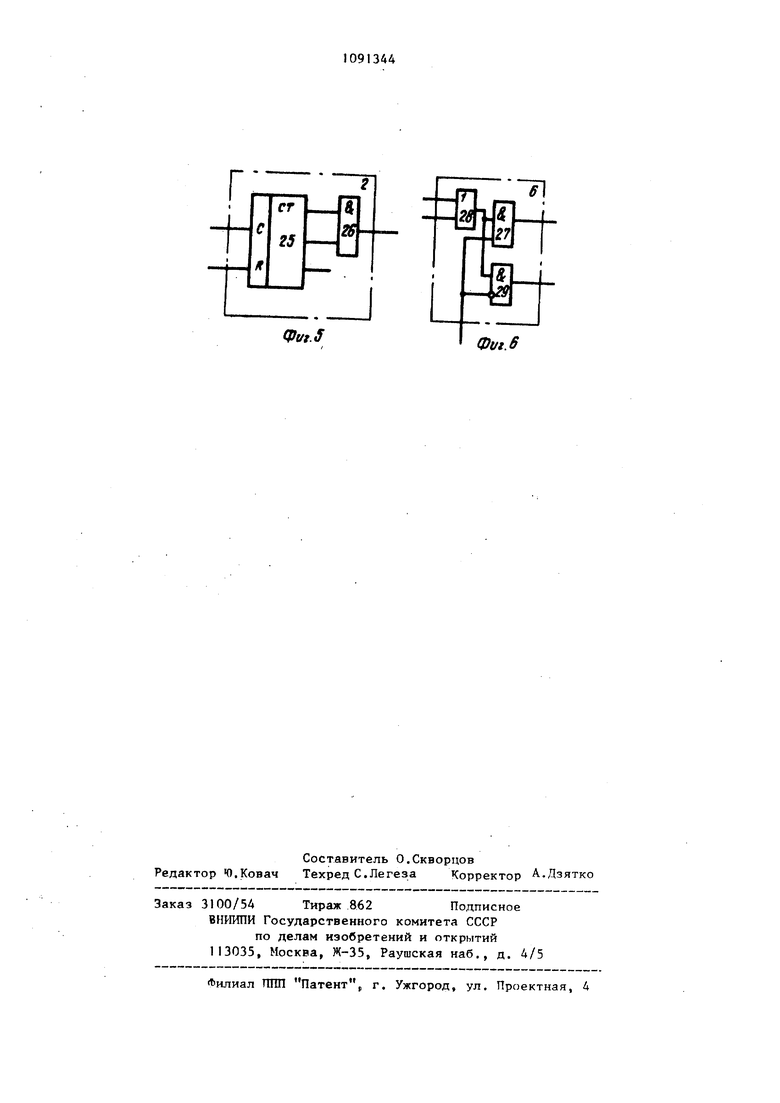

блока коммутации соединены с выводами управления коммутаторов Один из вариантов реализации коммутатора (фиг.З) содержит два элемента ЗАПРЕТ 17 и 18, элемент И-ИЕ 19 с инверсными входами и элемент И 20, выход которого соединен с выходом переноса коммутатора, информационный вход которого соединен с пряммми входами элементов ЗАПРЕТ 17 и 18 и первым входом элемента И-НЕ 19 с инвесрными входами, второй вход и выход которого соед;- ;-:ены соответственно с входом переноса коммутатора и первым входом элемента И 20, второй вход которого соединен с выходом первого элемента ЗАПРЕТ 17, вход переноса коммутатора соединен с инверсным входом второго элемента ЗАПРЕТ 18, а выводы управления коммутатора соединены с инверсным входом первого элемента ЗЛПТЕТ 17 и выходом второго элемента ЗАПРЕТ 18. Вариант структурной схемы коммутатора на Лиг.4 имеет аналогичную конструкцию с точностью до инверсии входных и выходных сигналов и содержит элементы ЗАПРЕТ 21, два элемента II 22 и 23 и элемент ИЛИ 24.

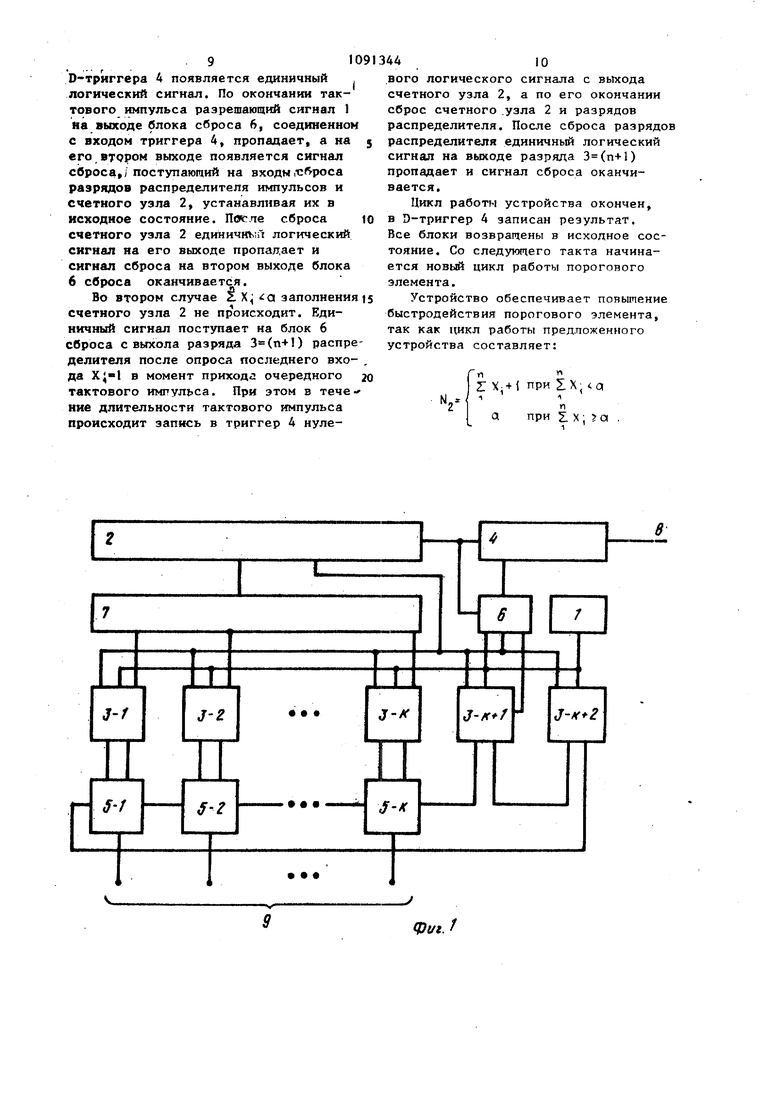

Счетный уэел содержит счетчик 25 и дешифратор 26, выход и входы которого соединены соответственно с В1)1ходом счетного уэла и выходами счетчика 25, счетный вход и вход сброса соединены с одноименными входами счетного узла. Блок сброса содержит элемент И 27, элемент ИЛИ 28 и элемент ЗАПРЕТ 29, первый вход блока сброса соединен с первым входом элемента ИЛИ 28, выход которого соединен с первыми входами элементов И 27 к ЗАПРЕТ 29, выходы которых соединены соответственно с первым и вторым выходами блока сброса, а второй и третий входы которого соединены с вторым входом элемента И 27 и вторым входом элемента ИЛИ 28, а второй инверсный вход элемента ЗАПРЕТ 29 соединен с вторым входом блока сброса..

Функционирование порогового элемента происходит следующим образом,

В исходном состоянии счетный узел 2 и разряды распределителя и триггер 4 сбропены. При этом в единичном состоянии находится разряд 3-(К+2) распределителя, а остальные разряды в нулевом. Разряды

К+2 распределителя с блоками коммутации , и элементом И.ПИ 7 образуют управляемый сканирутогдий мультиплексор, который в течение цикла работы опрашивает все входы 9 порогового элемента, на которые поданы единичные потенциалы, а точнее, формирует на выходе элемента ИЛТ1 7 последовательность из п единичньгх импульсов, где га - число единичных логических сигнапов на входах 9 порогового элемента, т.е. преобразует количество единичных логических сигналов на входах 9 в унитарный код. Последнее осуществляется следующим образом.

Если на входную пину подан нулевой логический сигнал, то блок . коммутации отключает входы и выходы разряда распределителя и работает в режиме трансляции сигналов, постуттагаигих на его входы с выходов блоков 5(i+I) и5 (i-l коммутации на входы блоков 5 (1-1) и 5() соответственно.Если Х- 1, то блок коммутации подключает входы и выходы разряда 3-L распределителя к входу и выходам блока 5(i-l) и 5(i-i-l) коммутации. В результате все разряды распределителя, для которых X j О оказываются отключены и образуется распределитель только из разрядов, для которых X 1. При подаче тактовых импульсов осуществляется последовательное формирование на выходе элемента ИЛИ 2 импульсов по числу разрядов входного кода, для которых 1 . Таким образом исключается опрос входных 1ЧИН, для которых Х 0 что и обеспечивает повьт1ение быстродействия. Нормируемые на выходе элемента ИЛИ 7 импульсы считаются счетным узлом 2. Функционирование, таким образом, происходит либо до заполнения счетного узла 2, что имеет место при X, Q , ттибо до опроса всех входов , при S Х i а , где а - порог.

3 первом случае при заполнении счетного узла 2 в момент при/сода на его вход а -го импульса на его выходе формируется единичный логический сигнал, который поступает на вход D-триггера 4 и третий вход блока сброса 6. При этом на выходе блок сброса 6, соединенном с входом разрешения записи П-триггера 4, формируется разрешающий сигнал и на выход

9091

D-rpiirrepa 4 появляется единичный , логический сигнал. По окончании тактового импульса разрешающий сигнал 1 иа выходе блока сброса 6, соединенном с входом триггера 4, пропадает, а на 5 его втором выходе появляется сигнал сброса,/поступающий иа входы,-сброса разрядов распределителя импульсов и счетного узла 2, устанавливая их в исходное состояние. По«сле сброса ю счетного узла 2 единичт.; логический сигнал на его выходе пропадает и сигнал сброса на втором выходе блока 6 сброса оканчивается.

Во втором случае Х а заполнения is счетного узла 2 не происходит. Единичный сигнал поступает на блок 6 сброса свыхола разряда 3(п+) распределителя после опроса последнего вхо- , да в момент прихода очередного 20 тактового импульса. При этом в тече мне длительности тактового импульса происходит запись в триггер 4 нулеи

J-f

j-г

5-1

п

S-Z

4410

вого логического сигнала с вьтода счетного узла 2, а по его окончании сброс счетного .узла 2 и разрядов распределителя. После сброса разрядов распределителя единичный логический сигнал на выходе разряда 3(п+1) пропадает и сигнал сброса оканчивается.

Цикл работы устройства окончен, в D-триггер 4 записан результат. Все блоки возвращены в исходное состояние. Со следующего такта начинается новый цикл работы порогового элемента.

Устройство обеспечивает повышение быстродействия порогового элемента, так как цикл работы предложенного устройства составляет:

Г X.+ i при IX, 0

N, п

а при 51 X; га .

j-/f

5К

ф«/г. 1

15

IS

фуг. 2

и

-vJ

- /

Ё -.

2Z

фиг.

J

Фог.5

71

Фи1.6

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Hurst S.L.nigital-sutranation threshdd logic pates: a new eircuit element | |||

| - Procuoling of IEEE, 1973, vol.120, N 1,November, p | |||

| Способ и устройство для непрерывного беления целлюлозы, бумажной полумассы и т.п. материалов | 1925 |

|

SU13011A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| иатент CPIA № 4027175, КЛ | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1984-05-07—Публикация

1982-06-23—Подача