w

Ё

Изобретение относится к вычислительной технике и может быть использовано в системах обработки дискретной информации Цель изобретения - повышение быстродействия. Преобразователь кодов содержит группу блоков 1 преобразования

2

ю

Os

ю

параллельного кода в последовательности импульсов, группу блоков 2 подсчета единиц в выходном коде, группу блоков 3 формирования переноса и элемент И 4. Функционирование происходит следующим образом. Каждый из блоков 1 преобра- зования преобразует часть разрядов входного параллельного кода в последовательности импульсов, поступающие на счет- ные входы соответствующего блока 2 подсчета, который-осуществляет их подсчет. При возникновении переноса в блоке 2 подсчета он сигналом переноса инициирует соИзобретение относится к вычислительной технике и может быть использовано в системах обработки дискретной информации.

Цель изобретения - повышение быстродействия.

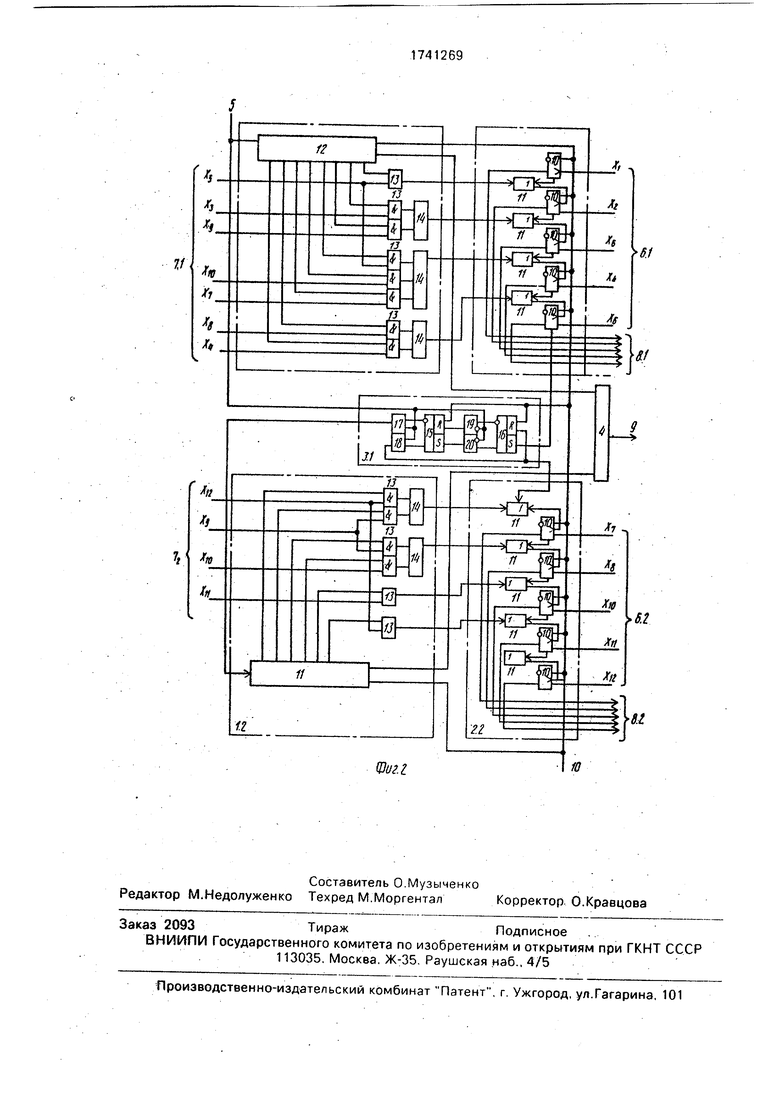

На фиг. 1 представлена структурная схема преобразователя кода системы счисления с одним основанием в код системы счисления с другим основанием; на фиг. 2 - схема преобразователя 12-разрядного двоично-десятичного кода в двоичный

Преобразователь (фиг. 1) содержит группу 1 блоков 1.1-t.p преобразования параллельного кода в последовательности импульсов, группу 2 боков 2.1-2.р подсчета единиц в выходном коде, группу 3 блоков 3.1-3.р-1 формирования.переноса, элемент И 4, тактовый вход 5, информационные входы 6.I второй группы, информационные входы 7.) первой группы, информационные выходы 8.1, выход окончания работы 9, вход 10 сброса.

Тактовый вход 5 преобразователя соединен с тактовым входом блока 1.1 преобразования параллельного кода в последовательности импульсов и тактовыми входами блоков 3.1-3.р-1 формирования переноса, вход сброса 10 соединен с входа-, ми сброса блоков 1.1-1.р преобразования параллельного кода в последовательности импульсов, блоков 2.1-2-р подсчета единиц в выходном коде, блоков 3.1-3.р-1 формирования переноса, блок 1.1 (I 1р) преобразования параллельного кода в последовательности импульсов соединен информационными входами с информационными входами 7.I первой группы преобразователя, выходами разрядов - с соответствующими счетными входами группы блока 2.I подсчета единиц в выходном коде, а выходом оконответствующий блок 3 формирования переноса, который на следующем такте блокирует подачу тактового импульса на тактовый вход следующего блока 1 преобразования и пропускает его на вход переноса следующего блока 2 подсчета. Работа продолжается в описанном порядке до преобразования всего входного кода, при этом на выходах останова блоков 1 преобразования появляются единичные сигналы, что вызывает единичный сигнал на выходе элемента И 4, свидетельствующий об окончании цикла работы 1 з.п. ф-лы, 2 ил.

чания работы - с входом элемента И 4, выход которого соединен с выходом 9 окончания работы устройства, блок 2.I подсчета единиц в выходном коде (i 1.2... ,р) соединен информационными входами с информационными входами 6.1 второй группы преобразователя, выходами разрядов результата - с информационными выходами 8.1 группы преобразователя, а выходом переполнения - с информационным входом блока 3.I формирования переноса, соединенного первым выходом с входом переноса блока 2.(i + 1) подсчета единиц в выходном коде, а вторым выходом - с тактовым входом блока 1.(i+1) преобразования параллельного кода в последовательности импульсов.

Блок 1.1 преобразования параллельного кода в последовательности импульсов

(фиг.2) содержит распределитель импульсов 12, соединенный тактовым входом и входом сброса с соответствующими входами блока, выходом останова - с выходом окончания работы блока, а выходами разрядов - с первыми входами элементов И группы 13. соединенных вторыми входами с информационными входами блока, выходы элементов И 13 каждой группы соединены с входами элемента ИЛИ 14, выход которого соединен

с выходом соответствующего разряда блока.

Блок 2.i подсчета единиц в выходном коде (фиг.2) содержит счетные триггеры 10 и элементы ИЛИ 11, входы сброса и установки

в единичное состояние счетных триггеров 10 соединены с входом сброса и информационным входом блока, i-й элемент ИЛИ 11 соединен выходом с счетным входом i-ro триггера 10, первым входом - с выходом

переноса (И)-го триггера 10, а вторым входом - с соответствующим счетным входом

блока, первый вход первого элемента ИЛИ является входом переноса блока.

Блок 3.1 формирования переноса (фиг.2) содержит R-S-триггеры 15, 16, элементы И 17, 18, элементы 19 запрета. 20, первые входы инверсных плеч триггеров 15, 16 соединены с входом сброса блока, первые входы элементов И 17.18 и управляющие входы элементов 19. 20 запрета соединены с тактовым входом блока, выходы инверсного и прямого плеч триггера 16 соединены с информационными входами элементов 19 и 20 запрета соответственно, соединенных вы- ходами с входом инверсного и прямого плеч триггера 15, выходы инверсного и прямого плеч которого соединены с вторыми входами элементов И 17 и 18 соответственно, выход элемента И 17 соединен с вторым выходом блока, а выход элемента И 18 - с входом инверсного плечэ триггера 16 и первым выходом блока.

Каждый из разрядов входного кода подается на информационные входы первой 7 и второй 6 групп с весами, сумма которых равна весу данного разряда входного кода.

Преобразователь работает следующим образом.

Входной код подается на информацией- ные входы 6.i второй и 7 i первой группы (i - 1,2р). При этом со входом 6 i второй группы он записывается в блок 2 i подсчета единиц в выходном коде группы после чего на тактовый вход5 подаются тлкювые импуль- сы. которые проходят на тактовый вход блока 1.1 преобразования параллельного кода в последовательности импульсов и через блоки 3.1 формирования переноса - на тактовые входы блоков 1 2-1 рпреобразования параллельного кода в последовательности импульсов. При этом каждый блок 1.1 преобразования параллельного кода в последова- тельности импульсов преобразует единичные сигналы на своих входах в после- довательности импульсов на соответствующих выходах разрядов, которые поступают на информационные входы блока 2.i подсчета единиц в выходном коде который их подсчитывает. Если в процессе работы блока 2.i подсчета единиц в выходном коде возникает его переполнение, то сигнал с его выхода переполнения, поступает на информационный вход блока 3.1 формирования переноса, при этом по поступлении очередного такто- вого импульса блок 3.1 блокирует его подачу на тактовый вход блока 1 .(и-1) преобразования параллельного кода в последовательности импульсов и пропускает его на вход переноса блока 2.(i+1) подсчета единиц в выходном коде, чем обеспечивается передача сигнала переноса. Работа продолжается таким образом до окончания преобразования входного кода блоком 1.1, после чего он самоблокируется (перестает формировать импульсы на выходах) и формирует единичный сигнал на выходе окончания работы, который поступает на вход элемента И 4. По окончании работы всех блоков 1 преобразования параллельного кода в последовательности импульсов на всех входах элемента И 4 оказываются единичные сигналы, что вызывает единичный сигнал на его выходе, являющемся выходом 9 окончания работы преобразователя. Результат снимается с информационных выходов 8.I блоков подсчета единиц в выходном коде 2.i.

Таким образом, предложенное устройство обеспечивает повышение быстродействия.

Формула изобретения 1. Преобразователь кода системы счисления с одним основанием в код системы счисления с другим основанием, содержащий группу блоков преобразования параллельного кода в последовательности импульсов, группу блоков подсчета единиц в выходном коде и элемент И, причем выходы окончания работы блоков преобразования параллельного кода в последовательности импульсов группы соединены с соответствующими входами элемента И, вход начальной установки преобразователя соединен с входами сброса блоков преобразования параллельного кода в последовательности импульсов группы и с входами сброса блоков подсчета единиц в выходном коде группы, тактовый вход преобразователя соединен с тактовым входом первого блока преобразования параллельного кода в последовательности импульсов группы, информационные входы блоков преобразования параллельного кода в последовательности импульсов группы соединены с соответствующими информационными входами первой группы преобразователя, выход окончания работы которого соединен с выходом элемента И. отличающийся тем. что, с целью повышения быстродействия, он содержит группу блоков формирования переноса, причем выходы разрядов k-ro (k 1-р. р - количество параллельно преобразуемых групп разрядов входного кода) блока преобразования параллельного кода в последовательности импульсов группы соединены с соответствующими счетными входами группы k-ro блока подсчета единиц в выходном коде группы, выходы разрядов результата блоков подсчета единиц в выходном коде группы соединены соответственно с информационными выходами группы преобразователя, тактовый вход и вход начальной установки которого соединены соответственно с тактовыми входами и с входами сброса блоков формирования переноса «руппы, информационные входы второй группы преобразо- вателя соединены с информационными входами соответствующих блоков подсчета в выходном коде группы, выход переполнения j-ro | 1-{р-1) блока подсчета единиц в выходном коде группы соединен с информа- ционным входом j-ro блока формирования переноса группы, первый и второй выходы которого соединены соответственно с входом переноса (j+1)-ro блока подсчета единиц в выходном коде группы и с тактовым входом Q+1)-ro блока преобразования параллельного кода в последовательности импульсов группы

блока формирования переноса соединены соответственно с входом установки в 1 второго триггера с первым входом установки в О второго триггера и с первым входом первого элемента И, выход которого и выход второго элемента И являются соответственно вторым и первым выходами блока формирования переноса, первый вход первого элемента И соединен с первым входом второго элемен га И и с управляющими входами первого и второго элементов запрета, выход второго элемента И соединен с вторым входом установки в О второго триггера, прямой и инверсный выходы которого соединены с информационными входами соответственно второго и первого элементов запрета, выходы которых соединены соответственно с входами установки в 1 и с первым входом установки в О первого триггера, прямой и инверсный выходы которого соединены соответственно с вторыми входами второго и первого элементов И, второй вход установки в О первого триггера соединен с первым входом установки в О второго триггера.

7,

Щи11

| Преобразователь кодов | 1987 |

|

SU1462487A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для преобразования двоичного кода в код по модулю К | 1987 |

|

SU1492479A1 |

| кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-06-15—Публикация

1990-01-02—Подача