Изобретение относится к микроэлектронике, а именно к структурам интегральных схем с комбинированной изоляцией элементов.

Известна структура интегральной схемы с комбинированной изоляцией, содержащая сформированные в кремниевой подложке области с эпитаксиальным и скрытым слоями, боковая изоляция которых выполнена в виде слоев диэлектрика, пересекающих эпитаксиальный слой и касающихся скрытого слоя, а изоляция данных участков скрытого слоя с подложкой обеспечивается р-n-переходом.

Недостатками данной структуры интегральной схемы являются:

малая плотность компоновки элементов интегральной схемы, ввиду существенного ухудшения электрических свойств изоляции при сближении элементов;

повышенная емкость перехода между коллекторной и базовой областями и увеличенная длина коммутирующих шин, что уменьшает быстродействие интегральных схем.

Наиболее близким техническим решением к данному изобретению является структура интегральной схемы с комбинированной изоляцией элементов, содержащая сформированные в кремниевой подложке области с эпитаксиальным и скрытым слоями, боковая изоляция которых выполнена в виде слоев диэлектрика, пересекающих эпитаксиальный и скрытый слои и часть подложки, а изоляция данных участков скрытого слоя с подложкой в виде р-n-перехода.

Недостатком данной структуры интегральной схемы является неопределенность глубины погружения слоев диэлектрика в подложку. В случае недостаточной глубины погружения невозможно повысить плотность компоновки элементов интегральной схемы из-за ухудшения электрических свойств изоляции при малом расстоянии между изолированными элементами схемы. Невозможность сближения элементов схемы не позволяет уменьшить длину коммутирующих шин, которая является одним из факторов, уменьшающих быстродействие интегральных схем. При излишней глубине погружения слоев диэлектрика в подложку существенно возрастает трудоемкость или становится невозможным формирование узких и глубоких канавок.

Целью изобретения является повышение плотности компоновки элементов и увеличение быстродействия интегральных схем.

Поставленная цель достигается тем, что в структуре интегральной схемы с комбинированной изоляцией элементов, содержащей сформированные в кремниевой подложке области с эпитаксиальным и скрытым слоями, боковая изоляция которых выполнена в виде слоев диэлектрика, пересекающих эпитаксиальный и скрытый слои и часть подложки, а изоляция донных участков скрытого слоя с подложкой обеспечивается p-n-переходом, слои диэлектрика погружены в подложку в подложку на глубину не менее ширины области с обедненным зарядом донной части р-n-перехода между скрытым слоем и подложкой.

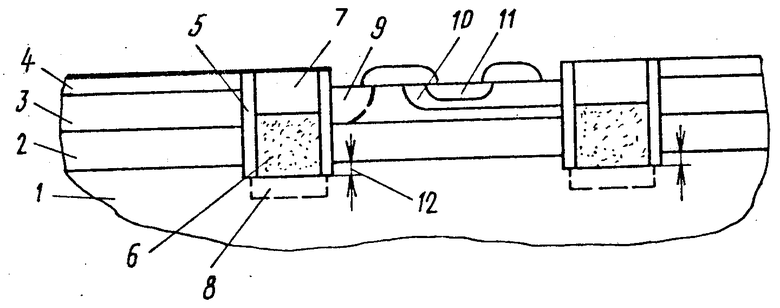

На чертеже показана структура интегральной схемы, содержащей монокристаллическую кремниевую подложку 1; скрытый n+-слой 2; эпитаксиальный слой n-типа проводимости 3; пленку нитрида кремния 4 на поверхности эпитаксиального слоя; пленку нитрида кремния 5 на боковых сторонах канавки, слой поликристаллического кремния 6; слой окисленного поликристаллического кремния 7; противоканальную р+-область 8; контакты к коллекторной области 9; область базы 10; область эмиттера 11.

П р и м е р. Структура интегральной схемы с комбинированной изоляцией содержит транзисторные области, боковые части скрытых слоев которых изолированы диэлектриком, погруженным в кремниевую подложку на глубину не менее ширины области с обедненным зарядом донной части р-n-перехода между скрытым слоем и подложкой. Транзисторные области имеют сплошной скрытый слой n-типа проводимости толщиной 3 мкм, сформированный в кремниевой подложке р-типа проводимости, эпитаксиальный слой n-типа проводимости толщиной 3 мкм, который располагается над скрытым слоем. Канавка шириной 1,5 мкм прорезает эпитаксиальный и скрытый слои и углубляется в подложку на 1 мкм. Вертикальные участки эпитаксиального и скрытого слоев, а также подложки в канавках изолированы пленкой нитрида кремния. Пространство между стенками в канавках заполнено поликристаллическим кремнием и двуокисью кремния до получения планарности структуры.

В табл. 1 представлены данные о площадях транзисторной структуры, изготовленной по процессу "Изопланар-2п" (образцы N 1,2,3), которая выбрана в качестве базового объекта для сравнения со структурой, выполненной в соответствии с данным изобретением (образцы N 4,5,6) при различной ширине разделительных канавок со следующими геометрическими параметрами: ширина окна 2 мкм; ширина металлизации 3 мкм, расстояние между дорожками металлизации 2 мкм, топологическая ширина мезаобластей 10 мкм.

Из анализа табл. 1 следует, что площадь, занимаемая изоляцией транзистора, выполненной в соответствии с данным изобретением (образцы N 4,5,6), уменьшается в 9-17 раз, что увеличивает плотность компоновки элементов интегральной схемы в 2,5-3 раза. При этом непланарность структуры составляет 0,15-0,2 мкм, когда как в структуре, изготовленной по процессу "Изопланар-2п", величина непланарности составляет 0,6-0,8 мкм.

При подаче напряжения на схему изоляции транзисторных областей от подложки осуществляется областью с обедненным зарядом донной части p-n-перехода между скрытым слоем и подложкой.

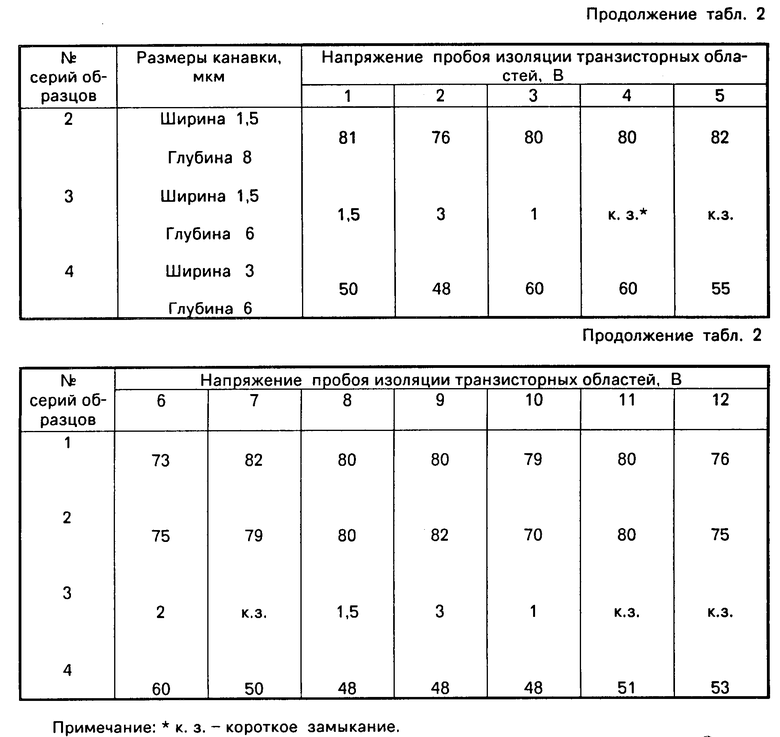

В табл. 2 представлены электрические характеристики изоляции транзисторных областей, выполненных в соответствии с данным изобретением.

Из анализа данных табл. 2 следует, что травление канавки на глубину, превышающую суммарную толщину скрытого и эпитаксиального слоев на 1 мкм (серия образцов N 1) и более 1 мкм (серия образцов N 2), обеспечивает напряжение пробоя 73-82 В. При этом величины токов через изоляцию составляют (1,5-2,5) ·10-9 А. Травление канавки на глубину, равную суммарной толщине скрытого и эпитаксиального слоев без учета ширины области с обедненным зарядом (серия образцов N 3), не обеспечивает изоляции транзисторных областей. Увеличение ширины канавки при той же глубине травления (серия образцов N 4) обеспечивает напряжение пробоя изоляции 48-60В при величине токов через изоляцию (25-50) ·10-9 А, но при существенном уменьшении плотности компоновки элементов интегральных схем.

Емкость р-n-перехода между скрытым слоем и подложкой транзисторных областей с изоляцией, выполненной по данному изобретению, уменьшается до 0,08-0,1 пкФ, в то время как в структурах, изготовленных по базовому процессу "Изопланар-2п", эта емкость составляет 0,5-0,6 пкФ.

Увеличение плотности компоновки элементов интегральных схем сопровождается уменьшением длины коммутирующих шин, что увеличивает быстродействие логических элементов интегральных схем в 1,3-1,5 раза.

Таким образом, реализация данного изобретения позволяет повысить плотность компоновки элементов интегральных схем в 2,5-3 раза;увеличить быстродействие логических элементов интегральных схем в 1,3-1,5 раза; улучшить электрические характеристики изоляции элементов интегральных схем.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ИЗГОТОВЛЕНИЯ ИНТЕГРАЛЬНЫХ ТРАНЗИСТОРОВ | 1985 |

|

SU1371445A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ИЗОЛЯЦИИ ЭЛЕМЕНТОВ ИНТЕГРАЛЬНЫХ СХЕМ | 1982 |

|

SU1111634A1 |

| КОНСТРУКЦИЯ ИНТЕГРАЛЬНЫХ СХЕМ С КОМБИНИРОВАННОЙ ИЗОЛЯЦИЕЙ И СПОСОБ ИХ ИЗГОТОВЛЕНИЯ | 1980 |

|

SU824824A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ САМОСОВМЕЩЕННОГО ВЫСОКОВОЛЬТНОГО ИНТЕГРАЛЬНОГО ТРАНЗИСТОРА | 2012 |

|

RU2492546C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ИС НА БИПОЛЯРНЫХ ТРАНЗИСТОРАХ | 1988 |

|

SU1538830A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ДИЭЛЕКТРИЧЕСКОЙ ИЗОЛЯЦИИ ЭЛЕМЕНТОВ ИНТЕГРАЛЬНЫХ СХЕМ | 1982 |

|

SU1840163A1 |

| СПОСОБ САМОСОВМЕЩЕННОГО ФОРМИРОВАНИЯ ИЗОЛЯЦИИ ЭЛЕМЕНТОВ ИНТЕГРАЛЬНЫХ МИКРОСХЕМ И ПОЛИКРЕМНИЕВЫХ КОНТАКТОВ К ПОДЛОЖКЕ И СКРЫТОМУ СЛОЮ | 2007 |

|

RU2356127C2 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ИНТЕГРАЛЬНЫХ СХЕМ С БОКОВОЙ ДИЭЛЕКТРИЧЕСКОЙ ИЗОЛЯЦИЕЙ | 1982 |

|

SU1060066A1 |

| СПОСОБ СОЗДАНИЯ ВЕРТИКАЛЬНОГО PNP ТРАНЗИСТОРА В СОСТАВЕ ИС | 1995 |

|

RU2106037C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ВЫСОКОВОЛЬТНЫХ ИНТЕГРАЛЬНЫХ СХЕМ С ДИЭЛЕКТРИЧЕСКОЙ ИЗОЛЯЦИЕЙ | 1990 |

|

SU1739805A1 |

СТРУКТУРА ИНТЕГРАЛЬНОЙ СХЕМЫ С КОМБИНИРОВАННОЙ ИЗОЛЯЦИЕЙ ЭЛЕМЕНТОВ, содержащая сформированные в кремниевой подложке области с эпитаксиальным и скрытым слоями, боковая изоляция которых выполнена в виде слоев диэлектрика, пересекающих эпитаксиальный и скрытый слои и часть подложки, а изоляция донных участков скрытого слоя с подложкой - в виде p - n-перехода, отличающаяся тем, что, с целью повышения плотности компоновки элементов и увеличения быстродействия интегральных схем, слои диэлектрика погружены в подложку на глубину не менее ширины области с объединенным зарядом донной части p - n-перехода между скрытым слоем и подложкой.

СТРУКТУРА ИНТЕГРАЛЬНОЙ СХЕМЫ С КОМБИНИРОВАННОЙ ИЗОЛЯЦИЕЙ ЭЛЕМЕНТОВ, содержащая сформированные в кремниевой подложке области с эпитаксиальным и скрытым слоями, боковая изоляция которых выполнена в виде слоев диэлектрика, пересекающих эпитаксиальный и скрытый слои и часть подложки, а изоляция донных участков скрытого слоя с подложкой в виде p n-перехода, отличающаяся тем, что, с целью повышения плотности компоновки элементов и увеличения быстродействия интегральных схем, слои диэлектрика погружены в подложку на глубину не менее ширины области с объединенным зарядом донной части p - n-перехода между скрытым слоем и подложкой.

| КОНСТРУКЦИЯ ИНТЕГРАЛЬНЫХ СХЕМ С КОМБИНИРОВАННОЙ ИЗОЛЯЦИЕЙ И СПОСОБ ИХ ИЗГОТОВЛЕНИЯ | 1980 |

|

SU824824A1 |

| T.Joichi, K Tokio et al U - groove isolation technology for high cleusity bipolar LST's proc of the 13th Conference on Solid State Devices Tokyo, 1981 | |||

| Jap | |||

| J | |||

| Appl Phys | |||

| Устройство для видения на расстоянии | 1915 |

|

SU1982A1 |

| Выбрасывающий ячеистый аппарат для рядовых сеялок | 1922 |

|

SU21A1 |

Авторы

Даты

1996-04-27—Публикация

1982-01-08—Подача