рольшоё количество вариантов реализа- 25 чения из его схемы первого транзис- |ии, что не является принципиальным

|;ля достижения поставленной цели, Выполнение этого блока на основе Мультиплексора логических сигналов

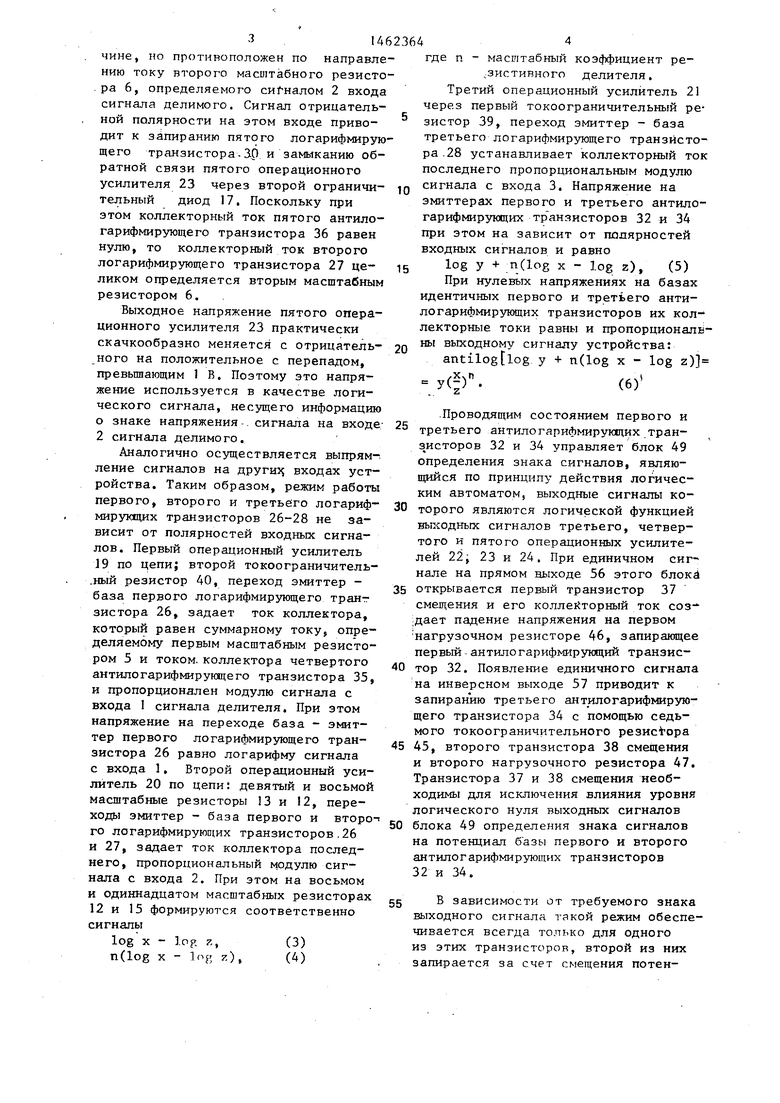

тора 37 смещения и шестого токоогра- ничительного резистора 44. При этом первый антилогарифмирующий транзистор 32 будет работать при обоих по- позволяет легко назначить и реапизо- зо лярностях, а третий антилогарифмирую- вать любую требуемую зависимость щий транзистор 34 - только при отри- Между знаками выходного и входных цательных значениях выходного сигна- сигналов устройства. Так, естествен- ла устройства, двухполярность кото|1ая. зависимость, характерная для вос- Ьроизведения множительно-делительных Операций I(), ..реализуется, как показано на фиг.2, подключением четырех информационных входов мульти- . (тлексора к иине нулевого потенциала, а на четыре других входа 62 должен. быть подан сигнал логической единицы, что соответствует четырем сочетаниям Знаков входных сигналов из восьми возможных, как для положительного, так и для отрицательного значения выходного сигнала. Использование стро бирующего входа V мультиплексора 58 позволяет по желанию пользователя исключить зависимость знака выходного сигнала от знаков входньгх сиг- Налов, т.е. получать модуль выходного сигнала устройства. Согласование уровней выходных сигналов четвертого, пятого и шестого операционных усилителей и уровней входных логических сигналов мультиплексора осуществляют преобразователи 39 - 61 уровня.

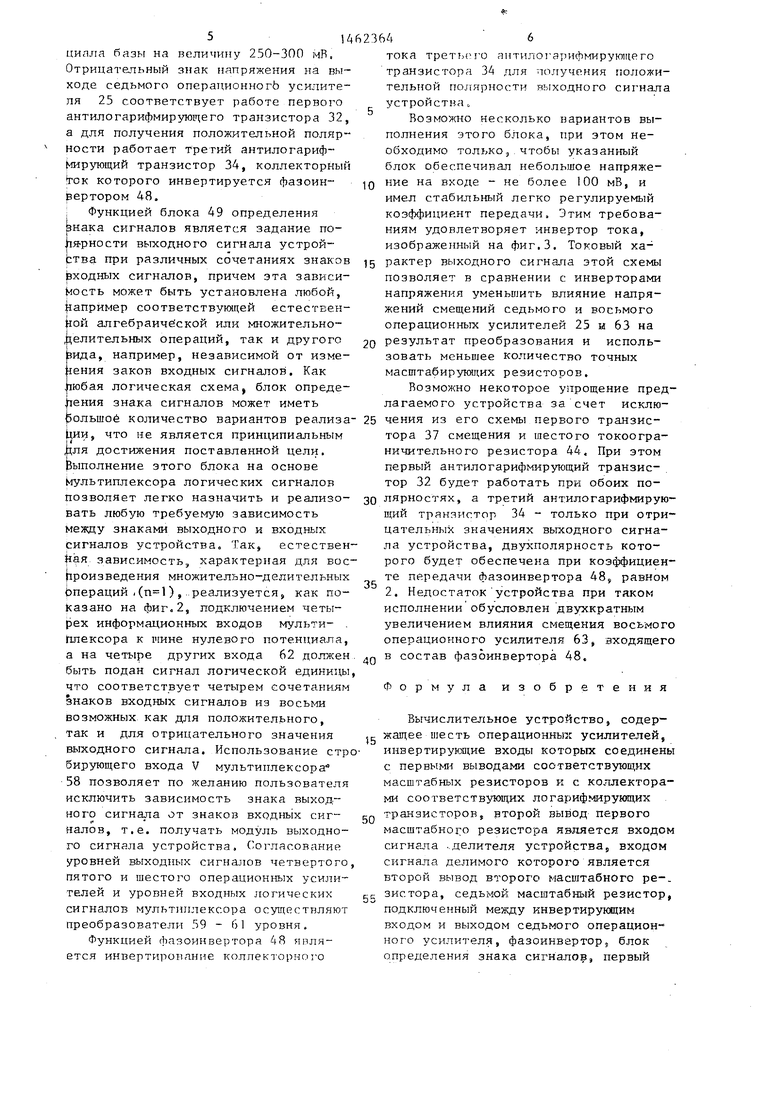

Функцией фазоинвертора 48 является инвертиропанне коллекторного

рого будет обеспечена при коэффициенте передачи фазоинвертора 48, равном 2. Недостаток устройства при таком исполнении обусловлен двухкратным увеличением влияния смещения восьмого операционного усилителя 63, входящего в состав фазоинвертора 48.

40

Формула изобретения

Вычислительное устройство, содер- jg жащее шесть операционньп : усилителей, инвертируюпше входы которых соединены с первыми выводами соответствующих масштабных резисторов к с коллекторами соответствующих логарифмирующих . 5-„ транзисторов, второй вывод первого масштабного резистора является входом сигнала ..делителя устройства, входом сигнала делимого которого является второй вывод второго масштабного ре-.

рг- зистора, седьмой масштабный резистор, J

подключенный между инвертирующим входом и выходом седьмого операционного усилителя, фазоинвертор, блок определения знака сигналов, первый

рого будет обеспечена при коэффициенте передачи фазоинвертора 48, равном 2. Недостаток устройства при таком исполнении обусловлен двухкратным увеличением влияния смещения восьмого операционного усилителя 63, входящего в состав фазоинвертора 48.

Формула изобретения

Вычислительное устройство, содер- жащее шесть операционньп : усилителей, инвертируюпше входы которых соединены с первыми выводами соответствующих масштабных резисторов к с коллекторами соответствующих логарифмирующих . транзисторов, второй вывод первого масштабного резистора является входом сигнала ..делителя устройства, входом сигнала делимого которого является второй вывод второго масштабного ре-.

зистора, седьмой масштабный резистор,

подключенный между инвертирующим входом и выходом седьмого операционного усилителя, фазоинвертор, блок определения знака сигналов, первый

и второй антилогарнфмирукяцие транзисторы, к инвертирующему входу седьмого операционного усилителя подключен коллектор первого антилогарифми- рующего транзистора, эмиттер которого соединен с эмиттером третьего логарифмирующего транзистора и через первый то коограничительный резистор соединен с выходом третьего операционного усилителя, эмиттеры первого и второго логарифмирующих транзисторов через второй токоограничительный резистор соединены с выходом пер вого операционного усилителя, эмиттер шестого логарифмирукщего и второго антилогарифмируклцего транзисторов через третий токоограничительный резистор подключены к выходу шестого операционного усилителя, эмиттер четвертого логарифмирукяцего транзистор через четвертый токоограничительный резистор соединен с выходом.четвертого операционного усилителя, первый, второй и третий ограничительные, диоды, катод каждого из которых динен с инвертирующим входом, ,а анод соединен с выходом соответственно четвертого, пятого.и шестого операционных усилителей, пятый токограни-. чительный резистор, восьмой, девятый, десятый и одиннадцатый масштабные резисторы,-первые выводы восьмого и девятого масштабных резисторов соединены с базой первого логарифмирукщего транзистора, второй вывод девятого и первый вывод десятого масштабных резисторов соединены с выходом второго операционного усилителя.

45

второй вывод восьмого и первый вывод 40 логарифмирукяцего транзистора и с пер- одиннадцатого масштабных резисторов соединены с базами второго логарифмирующего и второго антилогарифмирующего транзисторов и подключены к шине нулевого потенциала, о т.л и - чающееся .тем, -что, с целью повьш1ения точности, в него введены третий, четвертый и пятый антилога- рифмирующие транзисторы, первый и второй транзисторы смещения, шестой и седьмой токоограничительные резисторы, первый и второй нагрузочные резисторы, причем эмиттер первого антилогарифмирующего транзистора соединен с эммитером третьего анти- gg

50

вым выводом первого нагрузочного резистора, коллектор второго транзистора смещения соединен с базой третьего антилогарифмирующего транзистора и с первым выводом isTOporo нагрузочного резистора, базы первого и второго транзисторов смещения, вторые выводы первого и второго нагрузочных резисторов, базы второго, четвертого и пятого:антилогарифни- рующих транзисторов, базы четвертого, пятого и шестого логарифмирующих транзисторов подключены к шине нулевого потенциала.

0

логарифмирующего транзистора, коллектор которого подключен к входу фазоинвертора, выход кoтopo o соединен с инвертирующим входом седьмого операционного усилителя, выход которого является выходом устройства, выход пятого операционного усилителя через пятый токоограничительный резистор соединен с эмиттером пятого логарифмирующего и пятого антилога- рифмирующего транзисторов, эмиттер четвертого антилогарифмирующего транзистора соединен с эмиттером четвер- 5 того логарифмирующего.транзистора, коллекторы четвертого, пятого и второго антилогарифмирунщих транзисторов подключены к инвертирующим вхог дам соответственно первого, второго, и третьего операционных усилителей, вторые выводы десятого и одиннадцатого масштабных резисторов подключены к базе третьего логарифмирующего транзистора, вторые выводы пятого и шестого масштабных резисторов соединены с вторыми вьшодами соответствен- Ht второго и третьего масштабных резисторов выходы четвертого, пятого и шестого операционных усилителей подключены соответственно к первому, второму и третьему входам блока определения знака сигналов, прямой и инверсный выходы которого соответственно через шестой и седьмой токо- огранйчительные резисторы подключены к эмиттерам соответственно первого и второго транзисторов смещения, коллектор первого транзистора смеще- ния соединен с базой первого анти0

5

0

5

логарифмирукяцего транзистора и с пер-

вым выводом первого нагрузочного резистора, коллектор второго транзистора смещения соединен с базой третьего антилогарифмирующего транзистора и с первым выводом isTOporo нагрузочного резистора, базы первого и второго транзисторов смещения, вторые выводы первого и второго нагрузочных резисторов, базы второго, четвертого и пятого:антилогарифни- рующих транзисторов, базы четвертого, пятого и шестого логарифмирующих транзисторов подключены к шине нулевого потенциала.

Фиг. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство | 1985 |

|

SU1282163A1 |

| Четырехквадратное множительно-делительное устройство | 1987 |

|

SU1474686A1 |

| Множительно-делительное устройство | 1987 |

|

SU1543426A1 |

| Вычислительное устройство | 1987 |

|

SU1539798A1 |

| Логарифмическое вычислительное устройство | 1987 |

|

SU1543425A1 |

| Устройство с регулируемым усилением | 1988 |

|

SU1741257A1 |

| Множительное устройство | 1982 |

|

SU1119037A1 |

| Перемножающее устройство | 1983 |

|

SU1168971A1 |

| Устройство усиления | 1985 |

|

SU1338001A1 |

| Перемножающее устройство | 1987 |

|

SU1465896A1 |

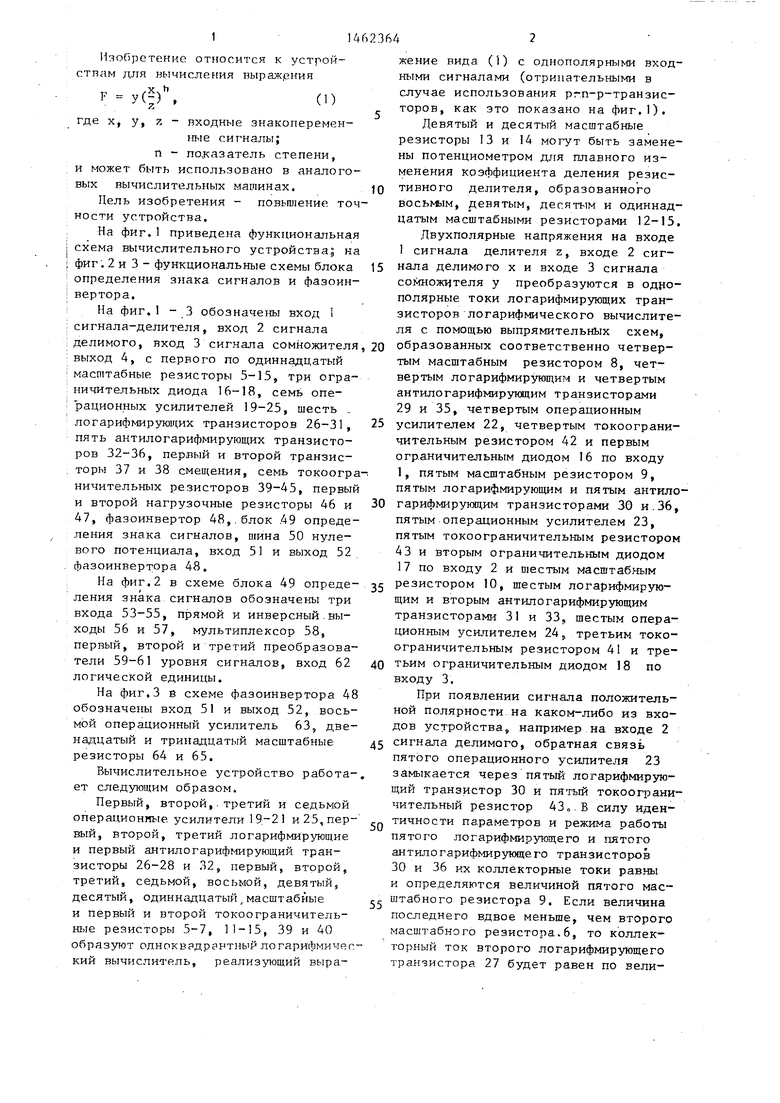

Изобретение относится к устройствам для вычисления выражения вида (x/z), где X, у, г - входные знакопеременные сигналы; п - показатель степени. Изобретение может быть использовано в аналоговых вычислительных машинах. Целью изобретения является повышение точности. Вычислительное устройство содержит входы сигнала делителя I, сигнала Делимого 2, сигнала сомножителя 3, с первого по одиннадцатый масштабные (резисторы 5-15, первый, второй и третий ограничительные диоды 16, 17 и 18, семь операционных усилителей 19-25, шесть хГогарифмирзтощих транзисторов 26-31, пять антилогарифмирукщих транзисторов 32-36, первый и второй транзисторы смещения 37 и 38, семь токоогра- ничительных резисторов 39-45, первый и второй нагрузочйые резисторы 46 и 47, фазоинвертор 48, блок 49 определения знака сигналов, шину 50 нулевого потенциала. Работа устройства основана на реализации логарифмического алгоритма. 3 ил. с (Л

фиг, 3

| Патент ..США № 3940603, кл | |||

| Упругая металлическая шина для велосипедных колес | 1921 |

|

SU235A1 |

| Планшайба для точной расточки лекал и выработок | 1922 |

|

SU1976A1 |

| Вычислительное устройство | 1985 |

|

SU1282163A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-02-28—Публикация

1987-07-28—Подача