Изобретение относится к электросвязи и может использоваться для передачи двух асинхронных потоков по одному каналу связи, оборудованному регенераторами пятиуровневого сигнала.

Цель изобретения - повьшение помехозащищенности и упрощение системы.

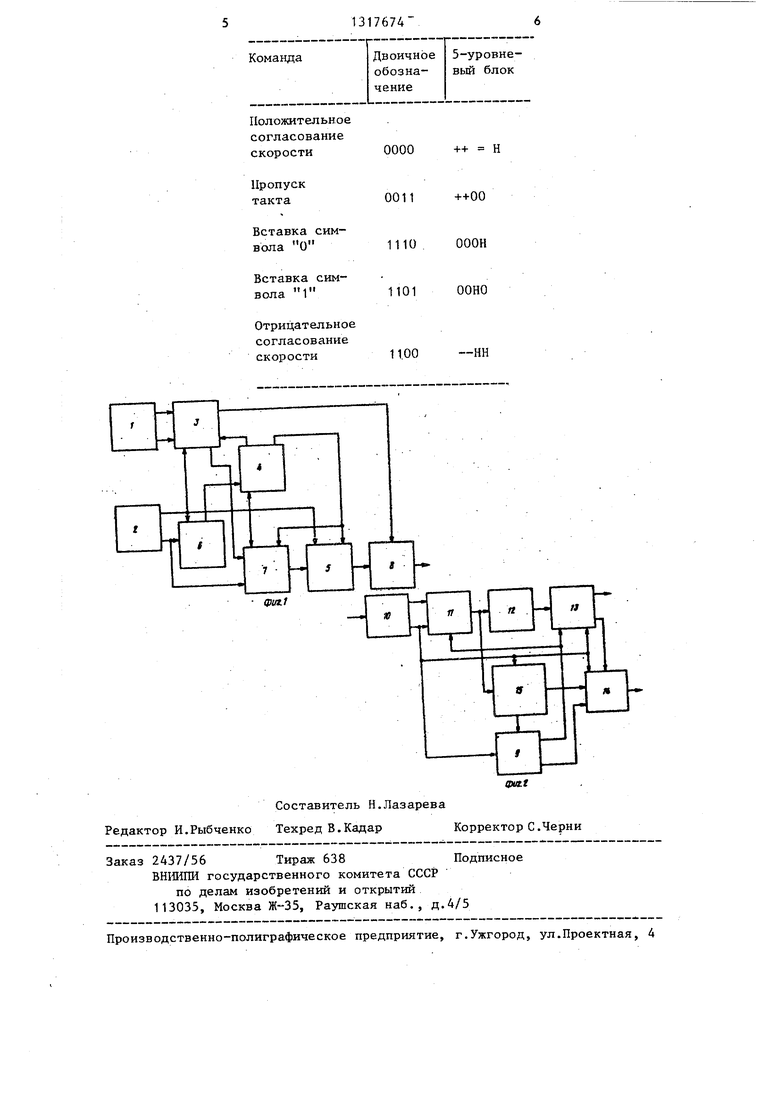

На фиг.1 изображена структурная электрическая схема передающей стороны системы; на фиг.2 - схема приемной стороны предложенной системы.

Система передачи и приема асинхронных цифровых сигналов содержит на передающей стороне источники 1 и 2 цифровых сигналов, блок 3 асинхронного сопряжения, делитель 4 час- тоты преобразователь 5 кода, приемник 6.циклового синхросигнала, регистр 7 памяти и корректор 8 символов, на приемной стороне - делитель 9 частоты, регенератор 10 сигнала, регистр 11 записи5 декодер 12, регистр 13 считывания, блок 14 асинхронного сопряжения., приемник 15

команд согласования. I

Система передачи и приема асинхронных цифровых потоков работает следующим образом.

Источник 1 генерирует тактовый и информационный сигналы. Последний записывается в блоке 3 асинхронного сопряжения со скоростью следования символов тактового сигнала, а считывается со скоростью сигнала, формируемого на,тактовом выходе источника 2, на информационном выходе которого вырабатывается сигнал, который содержит, согласно рекомендации-МККТТ G 751, в структуре цикла длиной 2928 бит синхросигнал ви,ца 111110100000. Приемник б циклового синхросигнала осуществляет поиск последнего сигнала

W

15

20

2,8 кГц.Таким образом, е следования символов в пе потоке ниже, чем во втор считывании в блоке 3 аси сопряжения в информацион необходимо делать вставк ных тактов, а при больше избыточную информацию не редавать параллельно осн налу.

В блоке 3 асинхронног происходит посимвольное информации первого цифро кроме 7-й тактовой позиц рой измывается символ а последующие символы сч такт раньше, затем в рег ти преобраз уются в парал таким образом, что на вх зователя 5 кода поочеред го цифрового потока пост состоящие из 8 символов, которых затянут на 4 так сигнала. Преобразователь мирует пятиуровневый сиг кода 8B4Q1 с численным з амплитуд символов: , 8B4Q1 алгоритмом кодопре

запрещены комбинации, ко быть использованы для пе полнительной информации следования циклов, напри вых 8 позициях циклового

35 нала во втором цифровом что равнозначно, на 1... вых позициях выходного с образователя 5 кода. Все команды по согласованию передачи избыточной инфо вого цифрового потока св таблицу, где им придано щее обозначение из числа

25

40

ных блоков кода.8В401. во втором цифровом потоке и формирует |

сигнал установки делителя 4 частоты,, в котором из тактового сигнала путем деления на 8 формируется сигнал, который для регистра 7 памяти является сигналом частоты считывания, а при делении на 2928 - сигнал огибающей команд согласования для блока 3 асинхронного сопр51жения в котором происходит преобразование скорости слеПри одинаковых скорос потоков в блоке 3 асинхр ряжения один раз в цикл команда, по .которой в ко Q символов на 1 .... А-й та зициях комбинация символ заменяется через цикл на При разных скоростях циф ков передаче дополнитель

дования символов первого цифрового ее мации непосредственно предшествует потока. Согласно рекомендации МККТТ G. передача в течение двух циклов под- 751 тактовые частоты цифровых потоков от четверичных систем передачи могут

ряд команды одного знака. Так, с , блока 3 асинхронного сопряжения в корректоре 8 символов сформирована

отличаться на 2 х 139264.10 кГц

5

0

2,8 кГц.Таким образом, если скорость следования символов в первом цифровом потоке ниже, чем во втором, то при считывании в блоке 3 асинхронного сопряжения в информационном сигнале необходимо делать вставки дополнительных тактов, а при большей скорости избыточную информацию необходимо передавать параллельно основному сигналу.

В блоке 3 асинхронного сопряжения происходит посимвольное считывание информации первого цифрового потока, кроме 7-й тактовой позиции, из которой измывается символ О (или 1) а последующие символы считываются на такт раньше, затем в регистре 7 памяти преобраз уются в параллельный код таким образом, что на вход преобразователя 5 кода поочередно от каждого цифрового потока поступают слова, состоящие из 8 символов, каждый из которых затянут на 4 такта тактового сигнала. Преобразователь 5 кода формирует пятиуровневый сигнал в виде кода 8B4Q1 с численным значением амплитуд символов: , , , . В коде 8B4Q1 алгоритмом кодопреобразования

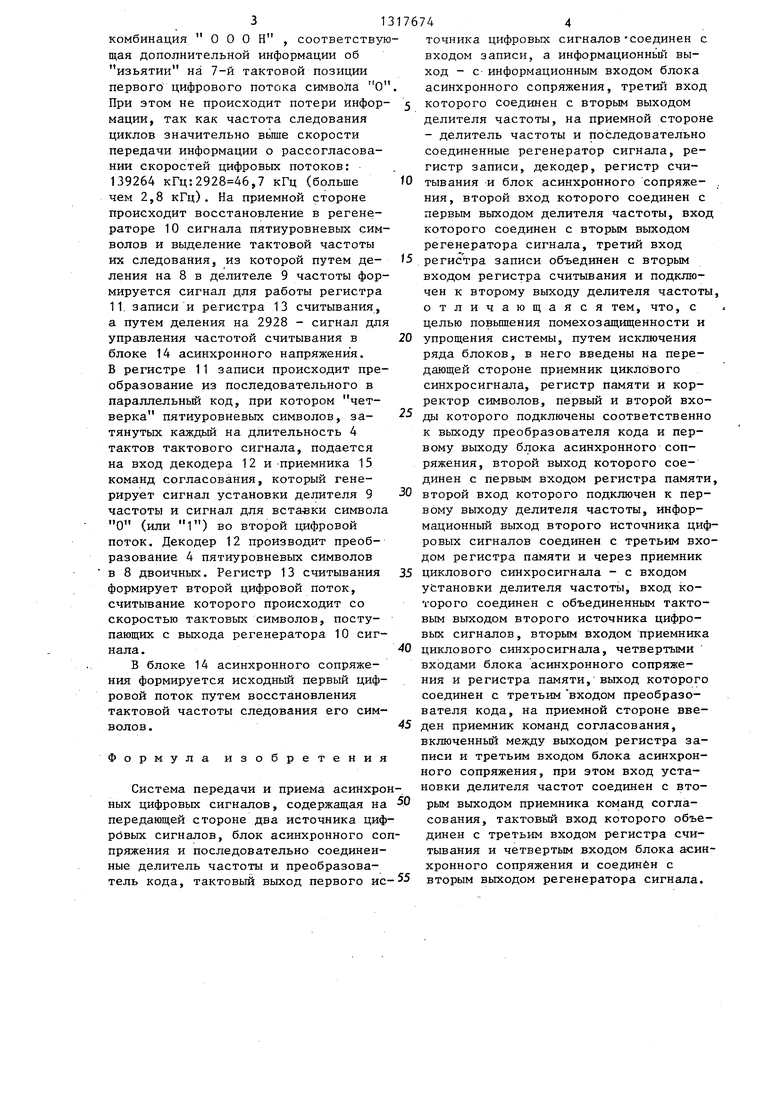

запрещены комбинации, которые могут быть использованы для передачи дополнительной информации со скоростью следования циклов, например, на первых 8 позициях циклового синхросиг5 нала во втором цифровом потоке или, что равнозначно, на 1... 4-й тактовых позициях выходного сигнала преобразователя 5 кода. Все требуемые команды по согласованию скорости и передачи избыточной информации первого цифрового потока сведены в таблицу, где им придано соответствующее обозначение из числа запрещен5

0

При одинаковых скоростях цифровых потоков в блоке 3 асинхронного сопряжения один раз в цикл формируется команда, по .которой в корректоре 8 Q символов на 1 .... А-й тактовой позициях комбинация символов заменяется через цикл на -Н. При разных скоростях цифровых потоков передаче дополнительной информации непосредственно предшествует передача в течение двух циклов под-

ряд команды одного знака. Так, с , блока 3 асинхронного сопряжения в корректоре 8 символов сформирована

комбинация О О О Н , соответствующая дополнительной информации об изъятии на 7-й тактовой позиции первого цифрового потока символа О При этом не происходит потери инфор- мадии, так как частота следования циклов значительно вьше скорости передачи информации о рассогласовании скоростей цифровых потоков: 139264 кГц:2928 46,7 кГц (больше чем 2,8 кГц). На приемной стороне происходит восстановление в регенераторе 10 сигнала пятиуровневых символов и выделение тактовой частоты их следования, из которой путем де- ления на 8 в делителе 9 частоты формируется сигнал для работы регистра 11. записи и регистра 13 считывания, а путем деления на 2928 - сигнал для управления частотой считывания в блоке 14 асинхронного напряжения. В регистре 11 записи происходит преобразование из последовательного в параллельньй код, при котором четверка пятиуровневых символов, за- тянутых каждьш на длительность 4 тактов тактового сигнала, подается на вход декодера 12 и приемника 15 команд согласования, который генерирует сигнал установки делителя 9 частоты и сигнал для вставки символа О (или 1) во второй цифровой поток. Декодер 12 производит преобразование 4 пятиуровневых символов в 8 двоичных. Регистр 13 считывания формирует второй цифровой поток, считывание которого происходит со скоростью тактовых символов, поступающих с выхода регенератора 10 сигнала .

В блоке 14 асинхронного сопряжения формируется исходный первый цифровой поток путем восстановления тактовой частоты следования его символов .

Формула изобретения

Система передачи и приема асинхроных цифровых сигналов, содержащая на передающей стороне два источника циф рбвых сигналов, блок асинхронного со пряжения и последовательно соединенные делитель частоты и преобразователь Кода, тактовый выход первого ис

точника цифровых сигналов «соединен с входом записи, а информационнь1й выход - с- информационным входом блока асинхронного сопряжения, третий вход которого соединен с вторым выходом делителя частоты, на приемной стороне - делитель частоты и последовательно соединенные регенератор сигнала, регистр записи, декодер, регистр считывания и блок асинхронного сопряже- ния, второй вход которого соединен с первым выходом делителя частоты, вход которого соединен с вторым выходом регенератора сигнала, третий вход регистра записи объединен с вторым входом регистра считывания и подключен к второму выходу делителя частоты отличающаяся тем, что, с целью повьпления помехозащищенности и упрощения системы, путем исключения ряда блоков, в него введены на передающей стороне приемник циклового синхросигнала, регистр памяти и корректор символов, первый и второй входы которого подключены соответственно к выходу преобразователя кода и первому выходу блока асинхронного сопряжения, второй выход которого соединен с первым входом регистра памяти второй вход которого подключен к первому выходу делителя частоты, информационный выход второго источника цифровых сигналов соединен с третьим входом регистра памяти и через приемник циклового синхросигнала - с входом установки делителя частоты, вход которого соединен с объединенным тактовым выходом второго источника цифровых сигналов, вторым входом приемника циклового синхросигнала, четвертыми входами блока асинхронного сопряжения и регистра памяти, выход которого соединен с третьим входом преобразователя кода, на приемной стороне введен приемник команд согласования, включенный между выходом регистра записи и третьим входом блока асинхронного сопряжения, при этом вход установки делителя частот соединен с вторым вьпсодом приемника команд согласования, тактовый вход которого объединен с третьим входом регистра считывания и четвертым входом блока асинхронного сопряжения и соединён с вторым выходом регенератора сигнала.

0000 ++ н

0011 ++00

1110 ОООН

1101 ООНО

1100 -НН

tpott

Составитель Н.Лазарева

-.:. корректор с.черни

вш™ т;;;;; б38

йНШИШ государственного комитета СССР

по делам изобретений и открытий 113035, Москва Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предпр тйёГгУужгородГул пр ёктнаяГГ

tpott

| название | год | авторы | номер документа |

|---|---|---|---|

| Система передачи и приема цифровой информации | 1985 |

|

SU1288923A1 |

| ЦИФРОВАЯ СИСТЕМА ПЕРЕДАЧИ С ДВУСТОРОННИМ СОГЛАСОВАНИЕМ СКОРОСТИ | 1991 |

|

RU2022476C1 |

| УСТРОЙСТВО ВРЕМЕННОГО ГРУППООБРАЗОВАНИЯ | 2006 |

|

RU2306674C1 |

| Устройство для многократного ответвления цифровых сигналов | 1986 |

|

SU1394445A1 |

| СИСТЕМА СИНХРОННОГО ВРЕМЕННОГО ГРУППООБРАЗОВАНИЯ | 1995 |

|

RU2096916C1 |

| Система для асинхронного сопряжения импульсных потоков | 1986 |

|

SU1420670A1 |

| Устройство передачи и приема команд согласования скоростей | 1989 |

|

SU1793553A1 |

| Преобразователь двоичного сигнала в балансный пятиуровневый сигнал | 1983 |

|

SU1095397A1 |

| СИНХРОННЫЙ АДАПТИВНЫЙ МУЛЬТИПЛЕКСОР | 1993 |

|

RU2078401C1 |

| МНОГОКАНАЛЬНОЕ ПРИЕМОПЕРЕДАЮЩЕЕ УСТРОЙСТВО С ВРЕМЕННЫМ РАЗДЕЛЕНИЕМ ЦИФРОВЫХ АСИНХРОННЫХ КАНАЛОВ | 1989 |

|

RU2033695C1 |

Изобретение относится к электросвязи и обеспечивает повышение помехозащищенности и упрощения системы путем исключения ряда блоков. Устройство содержит на передающей стороне источники цифровык сигналов, блок асинхронного сопряжения, делитель частоты, преобразователь кода, приемник циклового синхросигнала-, регистр памяти и корректор символов; на приемной стороне - делитель частоты, регенератор сигнала, регистр записи, декодер, регистр считывания, блок асинхронного сопряжения, приемник команд согласования, включенный между выходом регистра записи и третьим входом блока асинхронного сопряжения. 1 табл., 2 ил. 00 О) 4

| Патент Великобритании №1524797, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1987-06-15—Публикация

1986-01-06—Подача