с входом второго элемента ИЛИ 15. Появление единичного сигнала на выходе хотя бы одного из дешифраторов 2, 12 или одного из регистров 3, 13 фиксируется первым элементом ИЛИ 5, выход которого является выходом 10 конца

1

Изобретение относится к автоматике и вычислительной технике, может использоваться для построения различных устройств передачи и переработки дискретной информации и является усовершенствованием устройства по авт. св. 1096651.

Цель изобретения - повышение быстродействия.

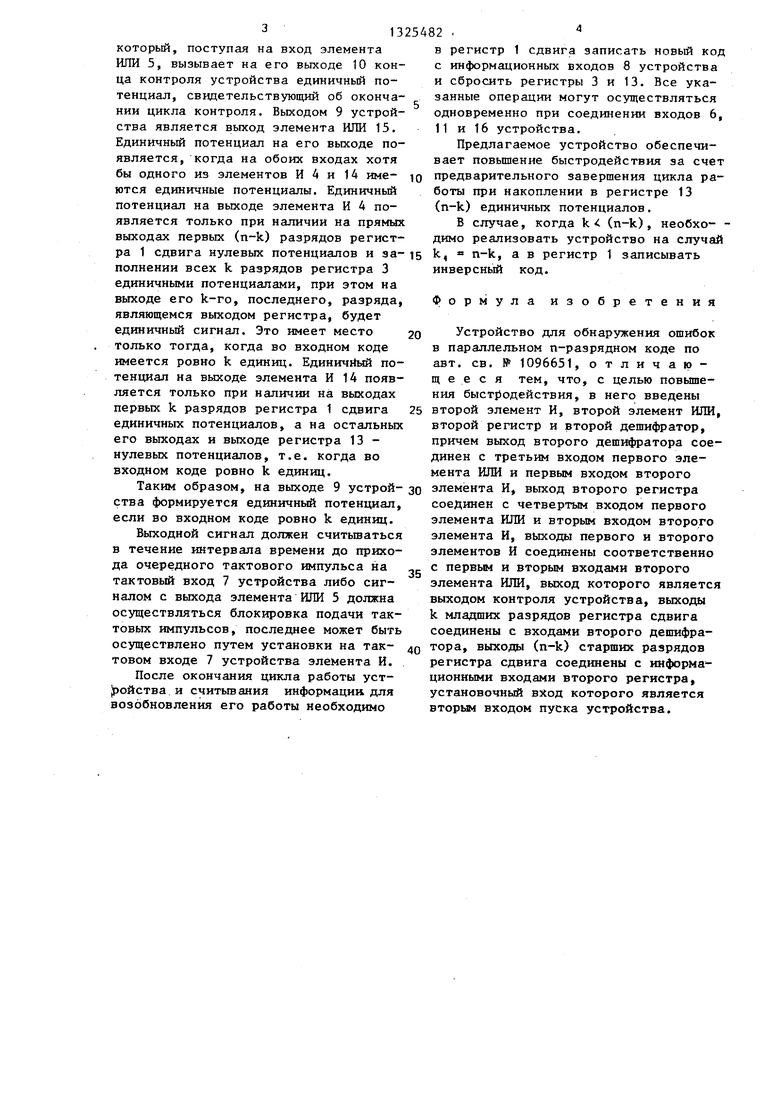

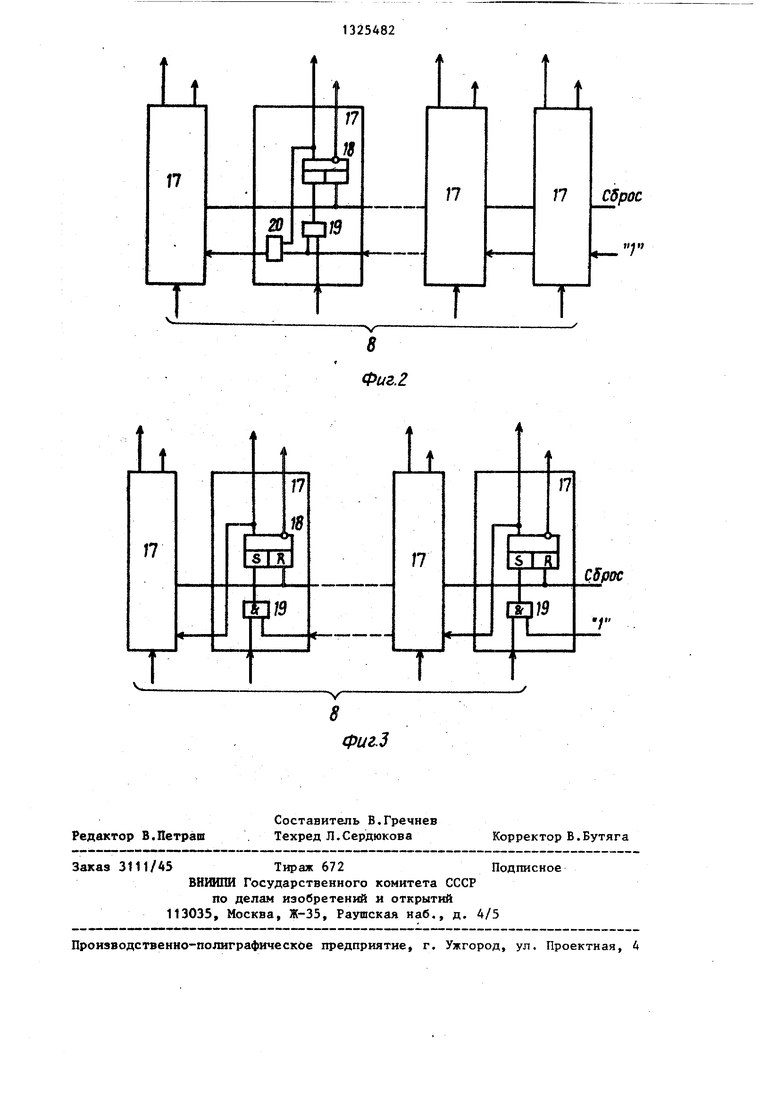

На фиг.1 приведена функциональная схема устройства; на фиг.2 и 3 - схема регистров, варианты выполнения.

Устройство для обнаружения ошибок в параллельном п-разрядном коде содержит регистр 1 сдвига, первый дешифратор 2, первый регистр 3, первый элемент И 4, первый элемент ИЛИ 5,« вход 6 разрешения записи устройства, тактовый вход 7 устройства, информационный вход 8 устройства, выход 9 контроля и выход 10 конца контроля устройства, первый вход 11 пуска устройства, второй дешифратор 12, второй регистр 13, второй элемент И 14, второй элемент ИЛИ-15, второй вход 16 пуска устройства.

Регистр 3 (13) содержит группу 17 разрядов, в состав которых входит триггер 18 и элементы И 19 и 20.

Дешифратор 2 (12) может быть выполнен в виде элемента И, соединенного входами с инверсными (прямыми) выходами младших n-k (k) разрядов регистра 1 сдвига (первым является крайний левый разряд), либо в виде элемента И с инверсными входами, соединенного с прямыми (инверсными) выхо- дами младших n-k (k) разрядов регистра 1 сдвига.

Регистр 3 (13) может быть выпол- нен, ка в известном устройстве (фиг.2) в виде последовательно соединенных разрядов, каждый из которых содержит RS-триггер и два элемента И, либо

контроля устройства. Одновременное появление единичных сигналов на выходах 9, 10 устройства говорит о правильном приеме кода. Наличие единичного кода только на выходе 10 устройства говорит об ошибке в приеме. 3 ил.

5

0

5

0

5

0

(фиг.З) в виде последовательно соединенных разрядов, каждый из которых содержит элемент И и RS-триггер.

Устройство работает следующим образом.

В исходном состоянии регистр 1 сдвига, регистры 3 и 13 сброшены. На вход 6 разрешения записи устройства и регистра 1 сдвига подается сигнал разрешения записи, при этом в регистр

Iсдвига записьшается код с информа- ЦИОННО1ЭД входа 8 устройства. На входы

IIи 16 регистров 3 и 13 подаются сигналы сброса (можно одновременно с сигналом на вход 6 устройства). По окончании сигнала разрешения записи на тактовый вход 7 устройства, являющийся входом сдвига регистра 1.сдвига, подаются тактовые импульсы. При подаче тактового импульса код в регистре 1 сдвига сдвигается на один разряд вправо. При появлении единичного потенциала на выходе п-го разряда регистра 1 сдвига (нулевого потенциала на выходе п-го разряда) в первый разряд регистра 3 (13) записывается единичный потенциал. При появлении единичного (нулевого) потенциала на выходе (n-l)-ro разряда регистра 1 сдвига единичный потенциал записывается во второй разряд регистра 3 (13), при этом разрешается запись в его очередной разряд и т.д. Если единичный (нулевой) потенциал появляется сразу на нескольких очередных выходах регистра 1 сдвига, то он записьшает сразу во все следующие разряды регистра 3 (13) единичный потенциал, при этом разрешается запись в его очередной разряд.

Функционирование происходит таким образом до появления единичного потенциала на выходе дешифратора 2 или 12 ипи на выходе регистра 3 или 13,

который, поступая на вход элемента ИЛИ 5, вызывает на его выходе 10 конца контроля устройства единичный потенциал, свидетельствующий об окончании цикла контроля. Выходом 9 устройства является выход элемента ИЛИ 15. Единичный потенциал на его выходе появляется, когда на обоих входах хотя бы одного из элементов И 4 и 14 имеются единичные потенциалы. Единичный потенциал на выходе элемента И 4 появляется только при наличии на прямых выходах первых (n-k) разрядов регистра 1 сдвига нулевых потенциалов и за- полнении всех k разрядов регистра 3 единичными потенциалами, при этом на выходе его k-ro, последнего, разряда, являющемся выходом регистра, будет единичный сигнал. Это имеет место только тогда, когда во входном коде имеется ровно k единиц. Единичйый потенциал на выходе элемента И 14 появляется только при наличии на выходах первых k разрядов регистра 1 сдвига единичных потенциалов, а на остальных его выходах и выходе регистра 13 - нулевых потенциалов, т.е. когда во входном коде ровно k единиц.

Таким образом, на выходе 9 устрой- зо элемента И, выход второго регистра

ства формируется единичный потенциал, если во входном коде ровно k единиц.

Выходной сигнал должен считьшаться в течение интервала времени до прихода очередного тактового импульса на тактовый вход 7 устройства либо сигналом с выхода элемента ШШ 5 должна осуществляться блокировка подачи тактовых импульсов, последнее может быть осуществлено путем установки на тактовом входе 7 устройства элемента И.

После окончания цикла работы уст- ройства. и считьшания информации для возобновления его работы необходимо

в регистр 1 сдвига записать новый код с информационных входов 8 устройства и сбросить регистры 3 и 13. Все указанные операции могут осуществляться одновременно при соединении входов 6, 11 и 16 устройства.

Предлагаемое устройство обеспечивает повышение быстродействия за счет предварительного завершения цикла работы при накоплении в регистре 13 (n-k) единичных потенциалов.

В случае, когда k (n-k), необхо- - димо реализовать устройство на случай k, n-k, а в регистр 1 записывать инверсный код.

Формула изобретения

Устройство для обнаружения ошибок в параллельном п-разрядном коде по авт. св. № 1096651, отличающееся тем, что, с целью повышения быстродействия, в него введены второй элемент И, второй элемент ИЛИ, второй регистр и второй дешифратор, причем выход второго дешифратора соединен с третьим входом первого элемента ИЛИ и первым входом второго

5

0

соединен с четвертым входом первого элемента ШШ и вторым входом второго элемента И, выходы первого и второго элементов И соединены соответственно с первым и вторым входами второго элемента ИЛИ, выход которого является выходом контроля устройства, выходы k младших разрядов регистра сдвига соединены с входами второго дешифратора, выходы (n-k) старших разрядов регистра сдвига соединены с информационными входами второго регистра, установочный вход которого является вторым входом пуска устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения ошибок в параллельном @ -разрядном коде | 1982 |

|

SU1096651A1 |

| Устройство для сопряжения к абонентов с М вычислительными машинами | 1987 |

|

SU1411758A1 |

| Цифровой интегратор | 1975 |

|

SU661572A1 |

| Устройство для обнаружения ошибок в параллельном @ -разрядном коде | 1984 |

|

SU1168948A1 |

| Программируемое устройство управления | 1988 |

|

SU1659983A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Устройство для коммутации информационных каналов | 1981 |

|

SU1003123A1 |

| Устройство для сопряжения ЦВМ с абонентами | 1989 |

|

SU1679495A1 |

| Преобразователь кодов | 1988 |

|

SU1552380A1 |

| Устройство для распределения заданий процессорам | 1984 |

|

SU1196866A1 |

Изобретение относится к автоматике и вычислительной технике и может использоваться для построения различных устройств передачи и переработки дискретной информации. Цель изобретения - повьшение быстродействия. Сигнал, поступающий на вход 6 разрешения записи устройства, записьюает на регистр 1 сдвига информацию с информационного входа 8 устройства. Сигналы, поступающие на входы пуска 11, 16 устройства, устанавливают в нулевое состояние регистры 3, 13. Импульсы с тактового входа 7 устройства начинают сдвигать информацию на ре6. 7. гистре 1 сдвига. Единичный сигнал на выходе первого дешифратора 2 формируется, когда (n-k) младших разрядов регистра 1 сдвига находятся в нулевом состоянии. Единичный сигнал на выхог де первого регистра 3 формируется, когда k старших разрядов регистра 1 сдвига находятся в единичном состоянии. Отсутствие ошибки в принятом коде означает, что на выходах первого дешифратора 2 и первого регистра 3 единичные сигналы появятся одновременно. При этом сработает первый элемент И 4 и на выходе 9 контроля устройства будет единичный сигнал. Второй дешифратор 12 и второй регистр 13 фиксируют моменты возникновения единичных сигналов на выходах всех k младших разрядов и нулевых сигналов на выходах всех (n-k) старших разрядов регистра 1 сдвига соответственно. Одновременное появление единичных сигналов на выходах дешифратора 12 и регистра 13 фиксируется вторым элементом И 14, выход которого соединен i о S (Л с: «/

Авторы

Даты

1987-07-23—Публикация

1986-03-06—Подача