торого соединен с прямым выходом триггера, входами разрешения записи реверсивного счетчика результата и реверсивного счетчика аргумента и первым входом второго элемента ИЛИ второй вход и выход которого соответственно соединены с выходом пер- зого элемента задерлйси и управляющим входом буферного регистра, выход знака блока вычитания аргумента соединен с первым входом сумматора по МОДУЛЮ; два и через формирователь

О импульсов с входом установки в триггера, инверсный выход которого соединен с первым входом третьего элемента И и через второй элемент задержки с третьим входом первого элемента И, выход второго элемента И соединен с первым входом третьего

6344

элемента ИЛИ, выход и второй вход которого соединены соответственно со счётным вхйдом реверсивного счетчика адреса и выходом третьего элемента И, второй вход которого соединен с выходом обнуления блока вычитания ординат, выход знака которого соединен с вторым входом сумматора по модулю два, выход которого соединен с управляющим входом управления реверсом реверсивного счетчика результата, информационный вход которого соединен с выходом блока памяти ординат, информационный вход реверсивного счетчика аргумента соединен с выходом блока, памяти абсцисс, выход обнуления блока вычитания аргумента соединен с управляющим входом входного регистра.

| название | год | авторы | номер документа |

|---|---|---|---|

| Функциональный преобразователь | 1984 |

|

SU1211756A1 |

| Функциональный преобразователь | 1985 |

|

SU1249547A1 |

| Функциональный преобразователь | 1982 |

|

SU1037272A1 |

| Устройство для цифрового функционального преобразования | 1981 |

|

SU993271A1 |

| Цифровой функциональный преобразователь | 1983 |

|

SU1098006A1 |

| Функциональный преобразователь двух переменных | 1984 |

|

SU1168964A1 |

| Функциональный преобразователь | 1983 |

|

SU1115069A1 |

| Устройство для цифрового функционального преобразования | 1981 |

|

SU985792A1 |

| Функциональный преобразователь | 1981 |

|

SU960836A1 |

| Устройство для функционального преобразования цифровых сигналов | 1979 |

|

SU864293A1 |

ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ, содержащий генератор импульсов, первый элемент И, два управляемых делителя частоты, буферный регистр, блок деления, блок вычитания абсцисс, блок вычитания ординат, блок вычитания аргумента, реверсивный счетчик аргумента, реверсивный счетчик адреса, реверсивный счетчик результата, входной регистр, первый элемент ИЛИ, первый элемент задержки, блок памяти абсцисс и блок памяти ординат, причем выход генератора импуль-сов соединен с первым входом первого элемента И, выход которого соединен со счетными входами первого и второго управляемых делителей частоты, выходы которых соединены со счетными входами реверсивных счетчиков соответственно аргумента и результата, выходы которых соединены с входами вычитаемого блоков вычитания соответственно аргумента и ординат , входы уменьшаемого которых соединены с выходами соответственно входного регистра и блока памяти ординат, адресный вход которого соединен с выходом реверсивного счетчика адреса, вход управления реверсом которого соединен с выходом знака вычитания аргумента и управляющим входом реверсивного счетчика аргумента, выход реверсивного счетчика адреса соединен с адресным входом блока памяти абсциссы, выход которого соединен с входом уменьшаемого бЛока вы-, читания абсцисс и информационным входом буферного регистра, выход которого соединен со входом вычитаемого блока вычитания абсцисс, выход кото-, рого соединен с управляющим входом первого управляемого делителя частоты и входом делителя блока деления, выход и вход делимого которого соединены соответственно с управляющим входом второго управляемого делителя частоты и кодовым выходом блока вычитания ординат, выход об(Л нуления которого соединен с управляющим входом блока деления, входом разрешения записи первого управляемого делителя частоты, входом первого элемента задержки и первым входом первого элемента ИЛИ, второй вход и выход которого соединены со ответственно с выходом обнуления о блока вычитания аргумента и со входом первого элемента И, выход 4 реверсивного счетчика результата соединен с выходом преобразователя, вход которого соединен с информаци онным входом регистра, отличающийся тем, что, с целью повьщгения быстродействия, в него введены второй и третий элементы И, сумматор по модулю два, второй и третий элементы ИЛИ, формирователь импульсов, второй элемент задержки и триггер, причем вьосод генератора импульсов соединен с первым входом второго элемента И, второй вход ко

Изобретение относится к автоматике и вычислительной технике, в частности к устройствам кусочно-линейной аппроксимации и может быть использовано в сост|1ве аналого-цифровых вычислительных систем.

Цель изобретения - повышение быст родействия.

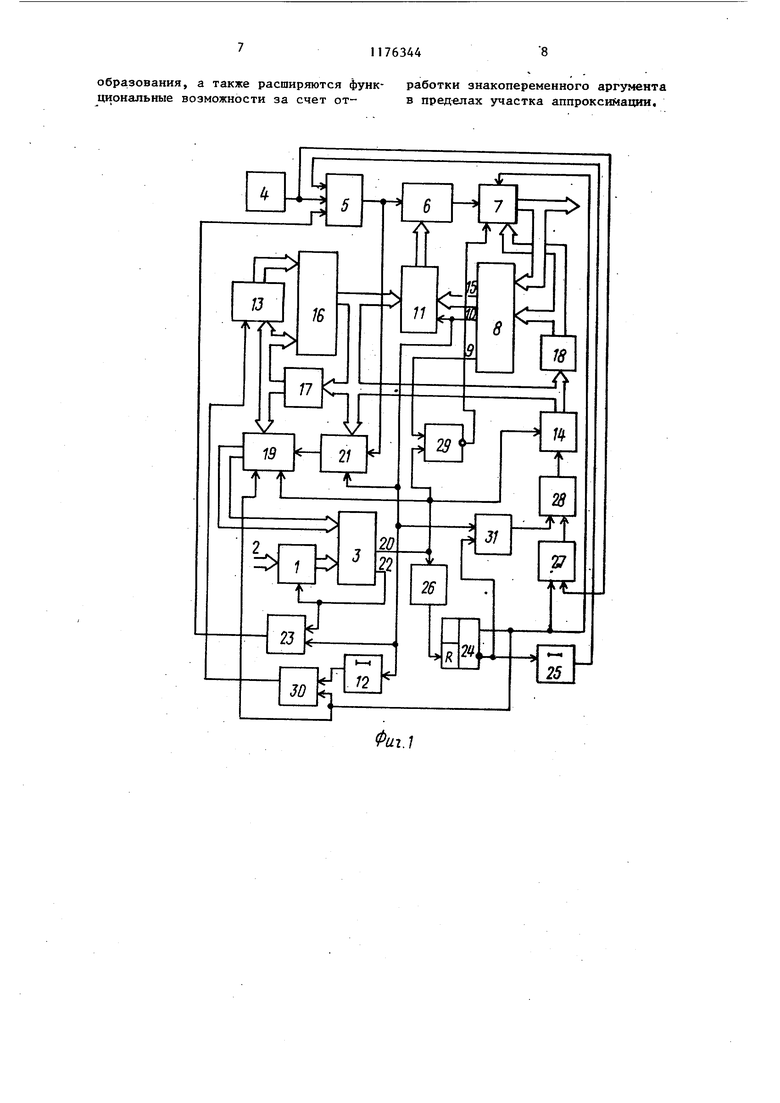

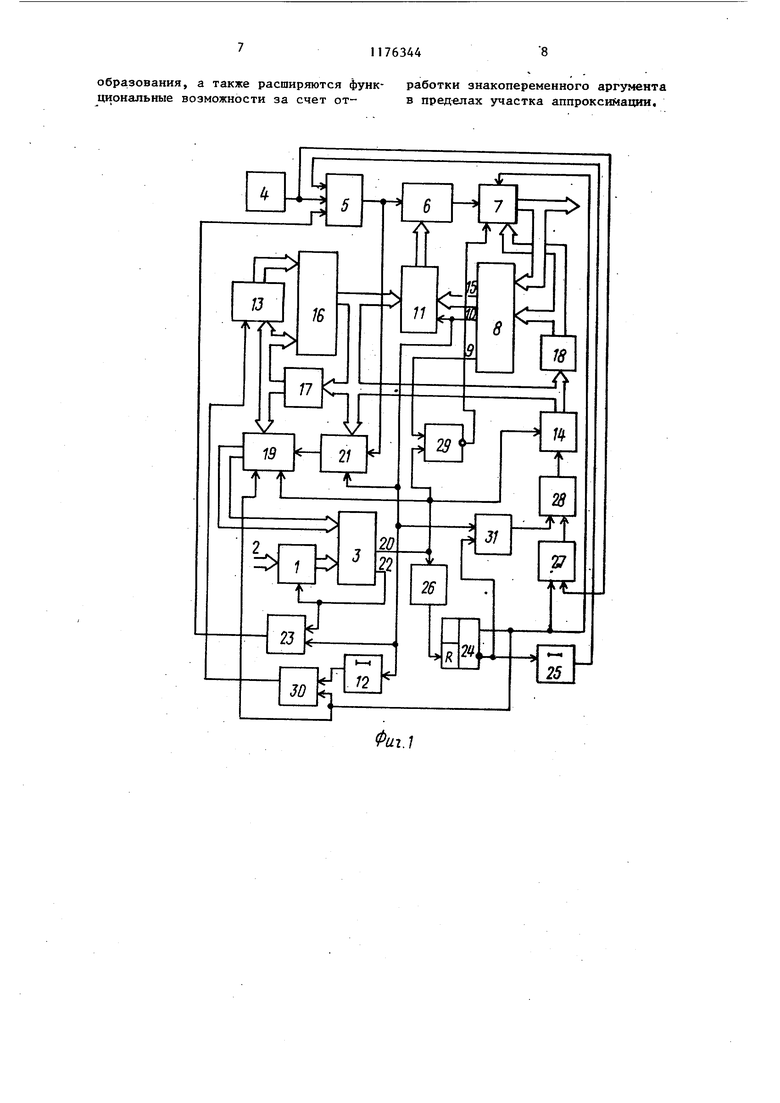

На .фиг. 1 представлена блок-схема функционального преобразователя; на фиг. 2 - несколько участков функции с произвольным заданием интервалов аппроксимахщи.

Преобразователь содержит регистр 1 аргумента, вход 2 преобразователя, блок 3 вычитания аргумента, генератор 4 импульсов, элемент И 5, управляемый делитель 6 частоты, реверсивный счетчик 7 результата, блок 8 вычитания ординат, выход 9 знака разности блока 8, выход 10 обнуления блока 8, блок 11 деления, элемент 12 задержки, буферный регистр 13, реверсивный счетчик 14 адреса, выход 15 кода разности блока 8, блок 16 вычитания абсцисс, блоки 17 и 58 памяти абсцисс и ординат соответственно, реверсивный счетчик 19 аргумента, выход 20 знака разности блока 3, укрепленный делитель 21 частоты, выход 22 обнуления блока 3, элемент ИЛИ 23, триггер

24, элемент 25 задержки, формирователь 26 импульсов, элемент И 27, элемент ИЛИ 28, элемент 29 задержки, элемент ИЛИ 30, элемент И 31.

Преобразователь работает следующим образом.

В блок 18 памяти ординат заносятся коды ординат узловых точек функции преобразования f(x,). В блок 17 памяти абсцисс заносятся коды абсцисс узловых точек функции преобразования, причем в первую ячейку блоков 17 и 18 памяти заносится нулевой код. По выходному коду реверсивного счетчика 14, разрядность которого определяется количеством участков аппроксимации, находятся коды ординаты и абсциссы соответствующего значения функции пре образования. Блоки 8 и 16 вычитания определяют разность кодог между поступившим и предыдущим значениями ординат,и абсцисс соответственно.

С помощью блока 11 деления и управ ляемого делителя 6 частоты автоматически устанавливается коэффициент наклона интерполирующих отрезков, причем коэффициент передачи делителя 6 частоты на каждом интервале аппроксимации пропорционален отношению:

Y,--Y;-,

, 3 где Y., и Y; - предыдущее и поступ шее значения ординат; X., и X; - предыдущее и поступивщее из блока 17 памяти значения абсцисс. С помощью блока 3 вычитания опре деляется момент остановки воспроизведения функции по совпадению кода поступившего аргумента с выхсУда регистра 1 и кода с выхода реверсивного счетчика 19 аргумента, При этом управляемый делитель 21 частоты управляет частотой импульсов, поступающих на счетный вход счетчика 19, в соответствии с разностью кодов между поступившей X|j и предыдущей ., абсциссами. Реверс счетчика 7, в зависимости от знаков разности с выходов 9 и 20 блоков 8 и 3 соответственно, опреде ляется состоянием сумматора 29 по модулю два. При этом нулевой код на выходе сумматора 29 соответствует режиму суммирования счетчика 7, а единичный код - режиму вычитания. Устройство работает следующим образом. В исходном состоянии реверсивные счетчики 7, 14 и 19., регистр 1 аргумента и буферный регистр I3 установлены в нуль, а триггер 24 - в ед ницу, Нулевой код с инверсного выхода триггера 24 закрывает элемент И 31, запрещая поступление сигнала сравнения с выхода 10 блока 8 на счетный вход счетчика 14 адреса, и элемент И 5, запрещая прохождение импульсов с генератора 4 импульсов на счетные входы счетчиков 7 и 19. Таким,образом, по нулевому коду. счетчика 14 из первых ячеек блоков 17 и 18 памяти извлекаются нулевые коды и на выходе 22 блока 3 вычитания аргумента формируется передни фронт сигнала сравнения. Передний фронт сигнала сравнения с выхода 22 блока 3 поступает на стробирующлй вход регистра 1, разрешая прием код первого значения аргумента X . При поступлении в блок 3 кода аргумента X ц на выходе 22 формируется задний фронт сигнала сравнения. По единичному коду с прямого выхода триггера 24 через элемент И 27 импульсы с выхода генератора 4 поступают на счетный вход счетчика 14 адресов блоков 17 и 18 памяти и по разрешающему сигналу с прямого вьпсода 444 триггера 24 код узловых точек .абсциссы и ординаты соответственно записываются в счетчики 19 и 7. По достижении счетчиком 14 адреса кода, соответствующего узловой точке с координатами Хф У, на выходе 2Q блока 3 изменится знак {по разности кодов „, , в резуль тате чего сработает формирователь 26 импульсов и триггер 24 обнулится. По заднему фронту с прямого выхода триггера 24 код аргумента. X , запишется в буферный регистр 13. При этом закроется элемент 27, и снимается разрешение устаовки кодов в счетчиках 7 и 19. На ыходе 10 блока 8 сформируется пеедний фронт сигнала сравнения коа X с выходов счетчика 7 и блока 18 памяти. Задержанный элементом 25 адержки, на время, необходимое ля формирования переднего фронта игнала сравнения с выхода 10 блоа 8, единичный код с инверсного ыхода триггера 24 поступает на ход элемента И 5, подготавливая реобразователь к интерполяции функий. Передний фронт сигнала сравнения с выхода 10 блока 8 поступает через. элемент ИЛИ 23 на вход элемент И 5, закрывая его на время установки коэффициента деленияделителей 6 и 21 Частоты, на вход стробирования блока 11 деления, разрешая вычисление коэффициента передачи делителя 6 частоты, на вход стробирования управляемого делителя 21 частоты, разрешая прием разности кодов абсцисс из блока 16 вычитания. По переднему фронту сигнала сравнения в соответствии со знаком разности кодов из кода счетчика 14 вычитается единица. Таким образом, по коду счетчика 14 из блог ков 17 и 18 памяти извлекаются коды абсциссы X 1, и ординаты Ущ- участка аппроксимации. При этом блоком 8 вычисляется разность кодов Ут между значением блока 18 памяти и счетчиком 7, а блоком 16 разность кодов Х.Х(п между значением блока 17 памяти и буферного регистра 13, Блок 11 деления вычисляет код Ут-.-Ул управлякмций коэффициентом передачи делителя 6 частоты на участке аппроксимации.

После поступления в блок 8 кода ординаты Уr. на выходе 10 блока 8 вырабатывается задний фронт сигнала сравнения, з-адержанный на время, необходимое для устанэвки коэффициента передачи в делителе 6 частоты.

По заднему фронту сигнала сравнекия в делителе 21 частоты устанавливается коэффициент передачи в соответствии с разностью кодов из блока 16, открывается элемент И 5 и импульсы с выхода генератора 4 импульсов поступают на счетный вход реверсивного счетчика 7, который в соответствии с состоянием сумматора 29 по модулю два будет находиться в режиме суммирования. Начинается ступенчато-линейная интерполяция функции на т-м интервале аппроксимации, причем частота импульсов с выхода генератора 4, поступающая на счетчик 7 ре- зультата определяется коэффициентом деления делителя 6 частоты, а на счетчик 19 аргумента - коэффициентом деления делителя 21 частоты. По заднему фронту задержанного сигнала сра нения код абсциссы Х, переписьшае ся в буферный регистр 13.

По совпадеЬию кода счетчика 19 и кода аргумента Х на выходе 22 обнуления блока 3 формируется импульсный сигнал, по переднему фронту которого элемент И 5 закрывается и разрешается прием следующего значения кода аргумента X щ., в регистр 1. При зтом на выходе 20 блока 3 формируется знак разности кодов Хц,-Хц, изменяющий реверс счетчика 19 и через сумматор 29 реверс счетчика 7. По заднему фронту сигнала сравнения с выхода 22 блока 3, задержанному на время установки знака реверса счетчиков 19 и 7, открвается элемент И 5 и начинается отработка аргумента Х|, . Коэффициент деления делителей 6 и 21 частоты останется прежним, так как не сформировался сигнал сравнения с выхода 10 блока 8. По достижении счетчиком 19 кода Х, на выходе 22 блока 3 сформируется очередной импульсный сигнал сравнения,.по переднему фронту которого элемент И 5 закроется и на вход стробирования регистра 1 поступит разрешение на прием кода следующего значения аргумента .

При поступлении в блок 3 кода аргумента X . выходе 20 блока 3 сформируется знак разности.кодов управляющий реверсом счетчиков 19 и 14 и через сумматор 29 реверсом счетчика 7, а на выходе 22 обнуления блока 3 - задний фронт сигнала сравнения, открывающий элемент И 5. Таким образом, начинается отработка поступившего аргумента X .2. 2 соответствии с коэффициентом передачи делителя 6 частоты данного, участка аппроксимации.

По достижении счетчиком 7 кода узловой точки ординаты Ущ- счетчик 19 достигнет кода абсциссы .пм выходе 10 блока 8 сформируется импульсный сигнал сравнения, по переднему фронту которого элемен И 5 закрывается, счетчик 14 переводится в следующее состояние в соответствии со знаком разности кодов X j(4z m- блоков 17 и 18 па1мяти извлекаются коды абсциссы Х,2 и ординаты Уп1-г (ш-1)-го участка аппроксимации. Блок 11 деления вычисляет код, управляющий коэффициентом .передачи делителя 6 частоты на данном участке аппроксимации. По заднему фронту сигнала сравнения, задержанному на время установки коэффициентов передачи делителей 6 и 21 частоты, открывается элемент И 5 и начинается воспроизведение данного участка функции. По заднему фронту задержанного сигнала сравнения код абсциссы узловой точки Х.- переписывается в буферный регистр 13. Таким образом, происходит ступенчато-линейная интерполяция функций в зависимости от кода поступивщего аргумент

На последующих участках аппроксимации преобразователь работает аналогично. Выходной код счетчика при необходимости может быть преобразован в анапоговьй сигнал.

Таким образом, в предложенном функциональном преобразователе по сравнению с известньм повьшается быстродействие, в частности при воспроизведении функций, имеющих больМую крутизну в начальный момент преобразования, а также расширяются функциональные возможности за счет отработки знакопеременного аргумента в предепах участка аппроксимации.

I

( tn-2

«2.2

| Устройство для цифрового функционального преобразования | 1981 |

|

SU993271A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Функциональный преобразователь | 1982 |

|

SU1037272A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-08-30—Публикация

1984-03-26—Подача