4i.

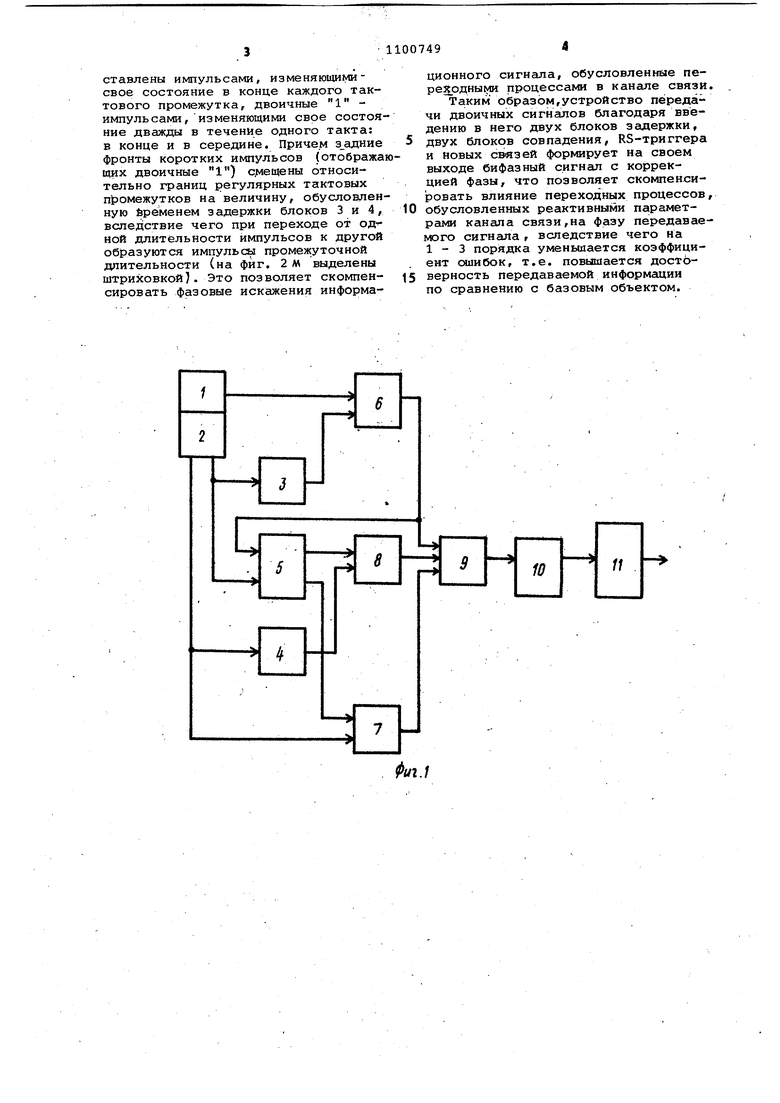

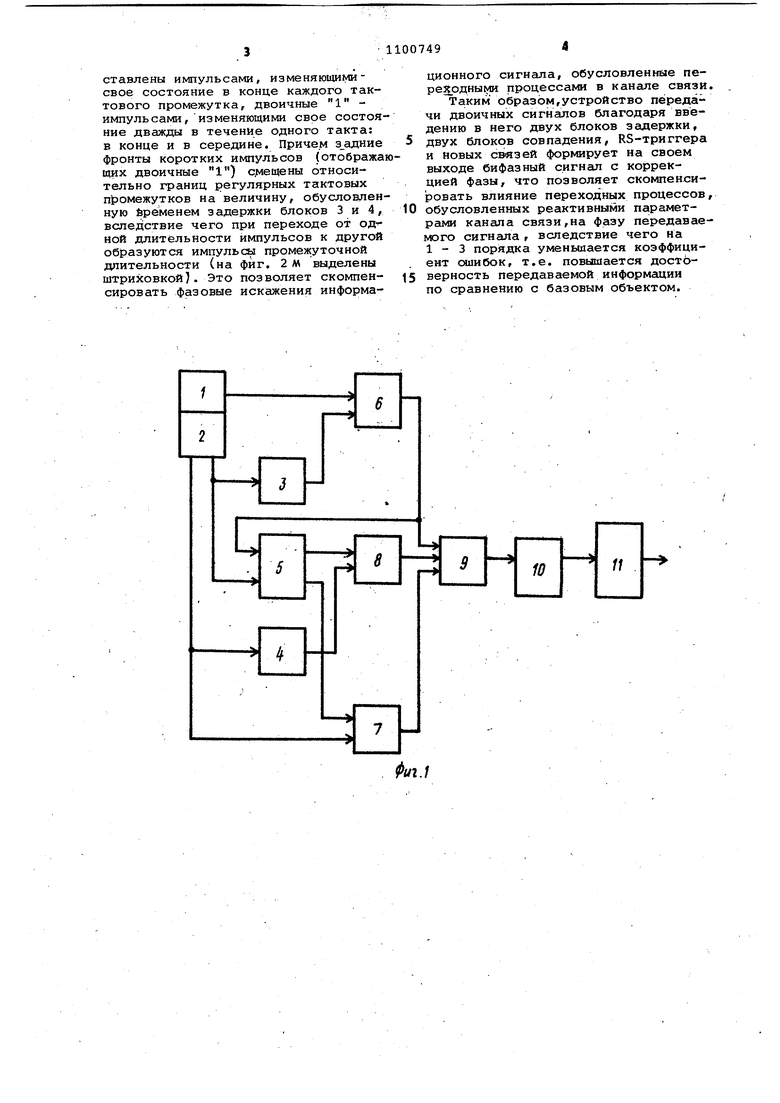

СО Изобретение относится к радиотехнике и может.быть использовано в, системах передачи дискретной ИНфОрМсЩИИ. Известно устройство передачи двоичных сигналов, содержащее источник цифрового сигнала, блок формирования бинмпульсного сигнала согласующий блок, генератор синхроимпульсов и амплитудный преобразователь, управляемой детектором длительности импульсов {Y}« однако известное устройство громоздко. Нёшболее близким к предлагаемому является устройство передачи двоичных сигналов,. содержащее источник цифрового сигнала с источником синхросигнала, .выход источника цифрового сигнала соединен с одним входом первого блока совпадения, выход KOTojJoro соединен с первым входом блока логического сложения, выход которогочерез счетный триггер соединен с согласующим блоком 2 . Однако в данном устройстве недос ,татрчная достоверность передачи. Цель изобретения - повышение достоверности передачи. Поставленная цель достигается тем. Что в устройство передачи двоичных сигналов, содержащее источ ник цифрового сигнала с источником синхросигнала, выход источника цифрового сигнала соединен с одним вхо дом первого блока совпадения, выход которого соединен с первым входом блока логического сложения, выход которого через счетный триггер соединен с согласующим блоком, введен AI два блока задержки, RS-триггер, второй и третий блоки совпадения, причем,один выход источника синхросигнала через первый блок задержки соединен с другим входом первого блока совпадения и с .первым входом RS-TpHprepa, второй вход которого соединен с выходом первого блока совпадения, другой выход источника синхросигнала соединен с одним входом второго блока совпадения .и через второй блок задержки - с одним входом тре,тьего блока совпадени другие, входы второго и третьего бло ков совпадения соединены с выходами RS-триггера, выходы второго и треть е.го блоков совпадения соединены с вторым и третьим входами блока логического сложения. На фиг.1 изображена структурная электрическая схема предлагаемого устройства на фиг. 2 - временные д аграмма, поясняющие работу устройст ва. Устройство передачи двоичных сигналов содержит источник 1 циФрозого сигнайЗг источник 2 синхросигнала, блоки 3 и 4 задержки, RS-триггер 5, блоки 6, 7 и 8 совпадения, блок 9 логического сложения, счетный триггер 10, согласующий блок 11. Устройство работает следующим образом. Цифровой двоичный сигнал (фиг.2а) источника 1 поступает на первый вход блока6 совпадения. Синхроимпульсы первой серии (фиг.2б) с первого, выхода источника 2 подают на R-вход RS-триггера 5, переводя его О на прямом выходе и в состояние 1 на инверсном выходе в состояние (фиг. 2,). Эти же синхроимпульсы через блок 3 подают на второй вход блока б-совпадения (фиг. 2Ь). Логическая 1 на первом входе блока б совпадения разрешает прохождение задержанных синхроимпульсов первой серии (фиг. 2 fe) с выхода блока б совпадения на первый вход блока 9 логического сложения и на S-вход RS-триггера 5 (фиг.26 ). При этом RS-триггер 5 устанавливается в состояние 1 на прямом выходе и в состояние О на инверсном выходе (фиг. 2 , ). С второго выхода,источника 2 синхроимпульсы второй серии (фиг. 2) , смещенные на полтакта относительно синхроимпульсов первой серии / (фиг,2 ), подают на первый вход блока 7 совпадения и через блок 4 задержки - на первый вход блока 8 совпадения. Логическая 1 на инверсном выходе RS-триггера 5 (фиг.2 J. ) разрешает прохождение синхроимпульсов второй серии (фиг. 22) через блок 7 совпадения на второй вход блока 9 логического сложения (фиг. 2 и) . Логическая 1 на прямом выходе RS-триггера 5 (фиг. 2) разрешает прохождение задержанных синхроймпул ьсов второй серии (фиг.2 g ) через блок 8 совпадения натретий вход блока 9 логического сложения (фиг. 2 S ) . « Импульсы, проходящие на входы блока 9 логического сложения, по.ступают с его выхода (фиг.2А) на вход счетного триггера 10, изменяя всякий разего состояние .(фиг.2.м). Так формируется бифазный сигнал с коррекцией (смешением) фазы, который через согласующий блок 11 подают в линию связи. Времена задержки блоков 3 и 4 равны, и их величину устанавливают в зависимости от реактивнЫх характеристик тракта и скорости передачи данных в пределах О - -|- Т, где Т - длительность такта, равная периоду следования двоичных символов. Как видно из ФИГ.2М , двоичные О в сформированном сигнале представлены импульсами, изменяющимисвое состояние в конце каждого тактового промежутка, двоичные 1 импульсами,изменяющими свое состояние дважды в течение одного такта: в конце и в середине. Причем з адние фронты коротких импульсов (отображащих двоичные 1) с.мещены относительно границ регулярных тактовых промежутков на величину, обусловленную бременем задержки блоков 3 и 4, вследствие чего при переходе от оД ной длительности импульсов к другой об разуются импульсы промежуточной длительности (на фиг. 2 м выделены штриховкой. Это позволяет скомпенсировать фазовые искажения информационного сигнала, обусловленные переходными процессами в канале связи.

Таким образом,устройство передачи двоичных сигналов благодаря введению в него двух блоков задержки,

двух блоков совпадения, RS-триггера и новых связей формирует на своем выходе бифазный сигнал с коррекцией фазы, что позволяет скомпенсировать влияние переходных процессов,

обусловленных реактивными параметрами канала связи,на фазу передаваемэго сигнала , вследствие чего на 1-3 порядка уменьшается коэффициент сяйибок, т.е. повышается достоверность передаваемой информации по сравнению с базовым объектом.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство передачи и приема двоичныхСигНАлОВ | 1979 |

|

SU824460A1 |

| Устройство для контроля блоков синхронизации | 1983 |

|

SU1134940A1 |

| Устройство для контроля функционирования логических блоков | 1986 |

|

SU1327107A1 |

| Адаптивный формирователь опережающего синхросигнала | 1988 |

|

SU1554110A1 |

| Устройство для передачи и приема цифровых сигналов | 1988 |

|

SU1566499A1 |

| Многоканальное устройство тестового контроля логических узлов | 1988 |

|

SU1564623A1 |

| Устройство передачи двоичных сигналов | 1987 |

|

SU1467782A1 |

| Приемник биполярных импульсов | 1991 |

|

SU1810991A1 |

| Устройство для передачи информации шумоподобными сигналами | 1984 |

|

SU1256239A1 |

| Устройство цикловой синхронизации | 1989 |

|

SU1626431A1 |

УСТРОЙСТВО ПЕРЕДАЧИ ДВОИЧНЫХ СИГНАЛОВ, содержащее источник цифрового сигнала с источником синхросигнала, выход источника цифрово го сигнала соединен с одним входом первого блока совпадения, выход которого соединен с первым входом блока логического сложения, выход которого через счетный триггер соединен с согласующим блоком, отличающееся тем, что, с целью повышения достоверности передачи, введены два блока задержки, RS-триггер, второй и третий блоки совпадения, причем один выход источника синхросигнала через первый блок за-, держки соединен с другим входом первого блока совпадения и с первым входом RS-триггера, второй вход которого соединен с выходом первого блока совпадения, другой выход источника синхросигнала соединен с одним входом второго блока совпадения и через второй блок задержки - с одним входом третьего блока совпадения, другие входы второго и третьего блоков совпадения соединены с выходами RS-триггера, выходы второго и третьего блоков совпадения соединены с вторым и третьим входами блока логического сложения.

С

5

11

10

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США 4170715, КЛ | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1984-06-30—Публикация

1983-03-21—Подача