Фиг/

Изобретение относится к электро- , связи и может быть использовано для передачи данных.

Цель изобретения - повышение помехоустойчивости .

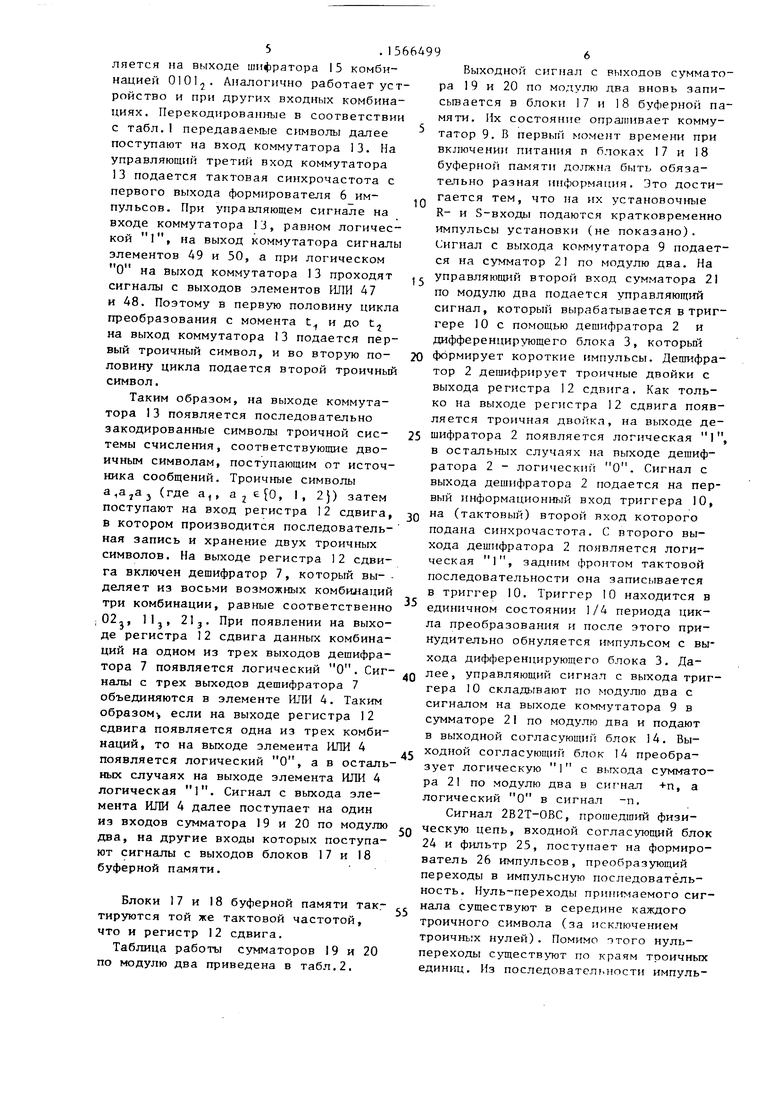

На фиг.1 изображена структурная электрическая схема предложенного устройства; на фиг.2 - структурная электрическая схема шифратора; на фиг.З - структурная электрическая схема декодера.

Устройство для передачи и приема цифровых сигналов содержит на передающей стороне источник 1 цифрового сигнала, первый дешифратор 2, дифференцирующий блок 3, элемент ИЛИ 4, формирователь 5 тактового сигнала, формирователь 6 импульсов, второй дешифратор 7, формирователь 8 синхроимпульсов, первый коммутатор 9, триггер 10, первый II и второй 12 регистры сдвига, второй коммутатор 13, выходной согласующий блок 14, шифратор 15, первый 16, второй 17 и третий 18 блоки буферной памяти, первый 19, второй 20 и третий 21 сумматоры по модулю два, а на приемной стороне - получатель 22 цифрового сигнала, блок 23 выделения синхросигнала, входной согласующий блок 24, фильтр 25, формирователь 26 импульсов, первый 27, второй 28 и третий 29 элементы И, первый 30, второй 31 и третий 32 триггеры,первый 33,второй 34 и третий 35 одновибраторы, резонансный блок 36, инвертор 37, первый 38 и второй 39 ференцирующие блоки, счетный триггер 40, регистр 41 сдвига, блок 42 буферной памяти, декодер 43, элемент ИЛИ-НЕ 44 и приемник 45 тактового сигнала.

Шифратор содержит дешифратор 46 и первый 47, второй 48, третий 49 и четвертый 50 элементы ИЛИ.

Декодер содержит дешифратор 51, первый 52, второй 53 и третий 54 элементы ИЛИ.

Устройство работает следующим образом.

Поток логических О и 1 с выхода источника 1 цифрового сигнала поступает на вход регистра 1I сдвига, состоящего из трех последовательно включенных триггеров (не показаны). При записи информации с выхода источ-г ника 1 цифрового сигнала в первый триггер информация с выхода первого триггера переписывается во второй

0

5

0

5

0

5

0

5

триггер, из второго - в третий. Запись двоичных нулей и единиц в регистр II сдвига производится задним фронтом тактовой последовательности, подаваемой с первого выхода формирователя 6 импульсов. Таким образом, информация с выхода источника 1 цифрового сигнала оказывается последовательно записанной на трех тактовых интервалах в регистре II сдвига. С приходом положительного фронта с третьего выхода формирователя 6 импульсов сигнал с выхода регистра I1 сдвига переписывается в блок 16 буферной памяти. В блоке 16 буферной памяти передаваемый сигнал на трех тактовых интервалах хранится в параллельном виде в виде трехразрядного числа. Хранение подобных трехразрядных чисел производится в течение одного цикла преобразования. Далее - трехразрядные числа передаваемого сигнала поступают на вход шифратора 15.

Порядок работы шифратора 15 приведен в табл.1 .

При появлении двоичной трехразрядной комбинации на входе дешифратора 46 на одном из восьми его выходов появляется сигнал логической 1. Например, если входная трехразрядная комбинация равна 000, то логическая 1 появляется на выходе О дешифратора 46. При появлении комбинации 1112 выходной сигнал логической 1 появляется на выходе 7 дешифратора 46.

Пользуясь табл.1, можно увидеть, что двоичная комбинация 000з должна превратиться в сигнал 023(подстроч- ные индексы означают систему счисления ). Так как на практике используются устройства с двумя устойчивыми состояниями, то сигналу 023 в троичной системе счисления соответствует сигнал 0010- в двоичной системе счисления.

Шифратор 15 в динамике работает следующим образом. В момент t в блоке 16 буферной памяти записывается комбинация 1002 которая в соответствии с табл.1 должна превратиться в сигнал llj или 01017- Так как входная двоичная комбинация на входе дешифра- . тора 46 равна 1004, то на четвертом выходе последнего появляется логическая 1. Данный сигнал логической I, пройдя через элементы ИЛИ 48-50 появ5.15

ляется на выходе шифратора 15 комби- 2

нацией 01012. Аналогично работает устройство и при других входных комбинациях. Перекодированные в соответствии с табл.1 передаваемые символы далее поступают на вход коммутатора 13. На управляющий третий вход коммутатора 13 подается тактовая синхрочастота с первого выхода формирователя 6 импульсов. При управляющем сигнале на входе коммутатора 1J, равном логической 1, на выход коммутатора сигналы элементов 49 и 50, а при логическом О на выход коммутатора 13 проходят сигналы с выходов элементов ИЛИ 47 и 48. Поэтому в первую половину цикла преобразования с момента t и до t на выход коммутатора 13 подается первый троичный символ, и во вторую половину цикла подается второй троичный символ.

Таким образом, на выходе коммутатора 13 появляется последовательно закодированные символы троичной системы счисления, соответствующие двоичным символам, поступающим от источника сообщений. Троичные символы aia7a3

(где

t

а г , 1 , 2}) затем

поступают на вход регистра 12 сдвига, в котором производится последовательная запись и хранение двух троичных символов. На выходе регистра 12 сдвига включен дешифратор 7, который вы- - деляет из восьми возможных комбинаций три комбинации, равные соответственно 02,, IK . При появлении на выходе регистра 12 сдвига данных комбинаций на одном из трех выходов дешифратора 7 появляется логический О. Сигналы с трех выходов дешифратора 7 объединяются в элементе ИЛИ 4. Таким образом если на выходе регистра 12 сдвига появляется одна из трех комбинаций, то на выходе элемента ИЛИ 4 появляется логический О, а в остальных случаях на выходе элемента ИЛИ 4 логическая 1. Сигнал с выхода элемента ИЛИ 4 далее поступает на один из входов сумматора 19 и 20 по модулю два, на другие входы которых поступают сигналы с выходов блоков 17 и 18 буферной памяти.

Блоки 17 и 18 буферной памяти тактируются той же тактовой частотой, что и регистр 12 сдвига.

Таблица работы сумматоров 19 и 20 по модулю два приведена в табл.2.

10

15

Выходной сигнал с выходов сумматора 19 и 20 по модулю два вновь записывается в блоки 17 и 18 буферной памяти. Их состояние опрашивает коммутатор 9. В первый момент времени при включении питания п блоках 17 и 18 буферной памяти должна быть обязательно разная информация. Это достигается тем, что на их установочные R- и S-входы подаются кратковременно импульсы установки (не показано). Сигнал с выхода коммутатора 9 подается на сумматор 21 по модулю два. На управляющий второй вход сумматора 21 по модулю два подается управляющий сигнал, который вырабатывается в триггере 10 с помощью дешифратора 2 и дифференцирующего блока 3, который

0 формирует короткие импульсы. Дешифратор 2 дешифрирует троичные двойки с выхода регистра 12 сдвига. Как только на выходе регистра 12 сдвига появляется троичная двойка, на выходе де

5 шифратора 2 появляется логическая 1, в остальных случаях на выходе дешифратора 2 - логический О. Сигнал с выхода дешифратора 2 подается на первый информационный вход триггера 10, на (тактовый) второй вход которого подана синхрочастота. С второго выхода дешифратора 2 появляется логическая 1, задним фронтом тактовой последовательности она записывается в триггер 10. Триггер 10 находится в единичном состоянии 1/4 периода цикла преобразования и после этого принудительно обнуляется импульсом с выхода дифференцирующего блока 3. Далее, управляющий сигнал с выхода триггера 10 складывают по модулю два с сигналом на выходе коммутатора 9 в сумматоре 21 по модулю два и подают в выходной согласующий блок 14. Выходной согласующий блок 14 преобразует логическую 1 с выхода сумматора 21 по модулю два в сигнал +n, a логический О в сигнал -п.

Сигнал 2В2Т-ОВС, прошедший физическую цепь, входной согласующий блок 24 и фильтр 25, поступает на формирователь 26 импульсов, преобразующий переходы в импульсную последовательность. Нуль-переходы принимаемого сигнала существуют в середине каждого троичного символа (за исключением троичных нулей) . Помимо -этого нуль- переходы существуют по краям троичных единиц. Из последовательности импуль0

5

0

5

0

5

сов с помощью сигнала одновибратора 33 резонансный блок 36 и инвертор 37 восстанавливают тактовый сигнал, который далее подается в приемник 45 тактового сигнала. Благодаря обратной связи с выхода инвертора 37 на второй вход одновибратора 33 и инерцинности резонансного блока 36 из смеси импульсов с выхода формирователя 26 импульсов выделяются только импульсы, расположенные в середине тактовых интервалов и отсутствующие при передаче троичных нулей. Тактовый сигнал резонансного блока 36 пропускает через элемент И 27 импульсы формирователя 26 импульсов, возникающие на границах тактовых интервалов принимаемого сигнала, В одновибраторе 34 происходит увеличение длительности импульсов для уверенного приема, а перезапись положительными переходами тактового сигнала в триггер 30 позволяет восстановить длительности сигналов. Отсутствие переходов в середние тактовых интервалов при передаче троичных нулей и, соответственно, высокий уровень напряжения на выходе одновибратора 33 в моменты положительных переходов сигнала резонансного блока 36 позволяют в триггере 31 восстановить импульсы троичных нулей. Для выделения синхросигнала сигнал с выхода т триггера 32 задерживают во втором триггере 31. Состояние триггеров 31 и 32 контролирует элемент ИЛИ-НЕ 44. Как только следуют подряд два нулевых сигнала, на выходе элемента ИЛИ-НЕ 44 появляется высокий потенциал. С помощью дифференцирующего блока 38 выделяется передний фронт сигнала. Данный короткий импульс используется для поддержания синфазности синхрочасто- ты. Синхрочастота получается путем деления на два тактовой частоты в счетном триггере 40. При появлении короткого импульса на выходе дифференцирующего блока 38 счетный триггер 40 принудительно устанавливается в нулевое состояние, тем самым поддерживается синфазность циклового сигнала. Дифференцирующим блоком 39 выделяются передние и задние фронты циклового синхросигнала и подаются на вход одновибратора 35. В элементах И 28 и 29 производится декодирование троичных сигналов (нулей, единиц и двоек). Действительно, при появлении нулевого сигнала на выходе

0

5

0

5

0

5

0

триггера 31 на выходах элементов И 28 и 29 логические О. Следовательно, принимается троичный нуль. При появлении на выходе триггера 31 логической 1 элементами И 28 и 29 производится опрос состояния триггера 30. Ведется опрос прямого и инверсного сигналов на выходе триггера 30. В случае появления логического О на прямом выходе 0 (на инверсном - единица) , на выходе элемента И 28 - логический О, а на выходе элемента И 29 логическая 1. Появляется комбинация 01 - троичная единица. В случае появления логической I на прямом выходе триггера 30 появляется комбинация 10 - троичная двойка. Сигналы троичной системы счисления записываются в регистр 41 сдвига. Запись производится задним фронтом импульсной последовательности с выхода одно- вибратора 35. Сигналы с выхода регистра 41 сдвига задним фронтом цикловой синхрочастоты переписываются в блок 42 буферной памяти. Далее два троичных символа (моменты t1f t

-5,. . .

j

t и) демодулируются в декодере 43, порядок работы которого обра- тен порядку работы шифратора 15 на передающей стороне и для дешифрации можно воспользоваться табл.1. При по- явлении троичной комбинации 11 на выходе блока 42 буферной памяти на выходе дешифратора 51 (выход 11) появляется высокий потенциал (логическая 1). Данный сигнал через элемент ИЛИ 54 выдается на выход декодера 43 . в виде комбинации 1002. Данная двоичная комбинация выдается получателю 22 цифрового сигнала, на выходе блока 42 буферной памяти появляется комбинация 20Э, которая аналогично дешифрируется в комбинацию 1 I 11 и т.д. Таким образом, на приемной стороне де- модулированы передаваемые сообщения и выданы получателю 12 цифрового сиг- |нала, который по своему усмотрению может их использовать в параллельном виде либо считать информацию последовательно.

Формула изобретения

I. Устройство для передачи и приема цифровых сигналов, содержащее на передающей стороне источник цифрового сигнала, формирователь синхросигнала,

триггер, выходной гргласующий блок, формирователь тактовых импульсов, выход которого соединен с первым входом формирователя импульсов, а на приемной стороне - вх9Дной согласующий блок, выход которого через фильтр соединен с входом формирователя импульсов, выход которого соединен с первым входом первого элемента И и с первым входом первого одновнбратора, второй вход которого подключен к выходу инвертора, к входу приемника тактового сигнала и к первому входу первого триггера, второй вход которого подключен к выходу второго одновибрато- ра, вход которого подключен к выходу первого элемента И, второй вход которого соединен с входом инвертора, с первым входом второго триггера и с выходом резонансного блока, вход которого подключен к выходу первого од- новибратора и к второму входу второго триггера, выход которого соединен с первым входом третьего триггера, получатель цифрового сигнала и блок выделения синхросигнала, отличающееся тем, что, с целью повышения помехоустойчивости, введены на передающей стороне три блока буферной памяти, три сумматора по модулю два, два регистра сдвига, шифратор, два коммутатора, дифференцирующий блок, два дешифратора и элемент ИЛИ, выход которого соединен с первыми входами первого и второго сумматоров по модулю два, впходы которых подключены к сигнальным входам соответственно второго и третьего блоков буферной памяти, выходы которых соединены соответственно с первым и вторым входами первого коммутатора, выход которого соединен с первым входом третьего сумматора по модулю два, второй вход которого подключен к выходу триггера, первый вход которого соединен с выходом первого дешифратора, вход которого подключен к первому выходу второго регистра сдвига, второй выход которого через второй дешифратор соединен с входами элемента ИЛИ, выход источника цифрового сигнала соединен с первым входом первого регистра сдвига, вьсход которого соединен с входом первого блока буферной памяти, первый выход которого соединен с входом шифратора, первый и второй выходы которого соединены соответственно с пер- вым и вторым входами второго коммута0

0

5

0

5

0

5

С

5

тора, третий вход которого соединен с синхронизирующим входом третьего блока буферной памяти и с первым выходом формирователя импульсов, второй выход которого соединен с третьим входом первого коммутатора и с вторым входом триггера, третий вход которого подключен к выходу дифференцирующего блока, вход которого подключен к второму выходу первого блока буферной памяти, выход формирователя синхросигнала соединен с вторым входом формирователя импульсов, третий выход которого соединен с вторым входом первого регистра сдвига, выходы второго и третьего блоков буферной памяти соединены с вторыми входами соответственно первого и второго сумматоров по модулю два, выход третьего сумматора по модулю два подключен к входу выходного согласующего блока, выход второго коммутатора соединен с входом второго регистра сдвига, а на приемной стороне введены элемент ИЛИ-НЕ, два дифференцирующих блока, счетный триггер, третий одновибратор, блок буферной памяти, декодер, регистр сдвига и второй и третий элементы И, выходы которых соединены соответственно с первым и вторым выхог дами регистра сдвига, третий вход которого подключен к выходу треяьет-о одновибратора, вход которого подключен к выходу второго дифференцирующего блока, вход которого соединен с входом блока выделения синхросигнала, с первым входом блока буферной памяти и с выходом счетного триггера, первый вход которого соединен с выходами первого дифференцирующего блока, вход которого подключен к выходу элемента ИЛИ-НЕ, первый вход которого соединен с выходом третьего триггера, первый вход которого подключен к второму входу элемента ИЧИ-НЕ и к первым входам второго и третьего элементов И, вторые входы которых соединены соответственно с первым и вторым выг ходами первого триггера, первый и второй выходы регистра сдвига соединены соответственно с вторым и третьим входами блока буферной памяти, выход которого через декодер соединен с входом получателя цифрового сигнала, выход резонансного блока соединен с вторым входом третьего тртгера, выход инвертора соединен с HI орым входом счетного триггера.

2. Устройство по п.1, о т л и ч а- ю щ е е с я тем, что шифратор содержит четыре элемента ИЛИ и дешифратор, первый выход которого соединен с пер- вым входом второго элемента ИЛИ, второй вход которого подключен к второму выходу дешифратора и к первому входу третьего элемента ИЛИ, второй вход которого соединен с пятым выходом де- шифратора и с вторым входом первого элемента ИЛИ, первый вход которого подключен к третьему выходу дешифратора, четвертый выход которого подключен к третьему входу второго элемента ИЛИ и к первому входу четвертого элемента ИЛИ, второй вход которого соединен с третьим входом первого элемента ИЛИ и с седьмым выходом дешифратора, шестой и восьмой выходы которого соединены соответственно с третьим входом третьего элемента ИЛИ и с третьим входом четвертого элемента ИЛИ, при этом входы дешифратора являются входом шифратора, первым и вторым выходами которого являются выходы соответственно первого, второ

5

0

5

го, третьего и четвертого элементов ИЛИ.

3. Устройство поп.1,отлича- ю щ е е с я тем, что декодер содержит три элемента ИЛИ и дешифратор, первый выход которого соединен с первым входом второго элемента ИЛИ, третий выход дешифратора соединен с первым входом первого элемента ИЛИ и с первым входом третьего элемента ИЛИ, второй вход которого подключен к четвертому выходу дешифратора, пятый выход которого соединен с вторым входом первого элемента ИЛИ, третий вход которого соединен с шестым выходом дешифратора, с вторым входом второго элемента ИЛИ и с третьим входом . третьего элемента ИЛИ, четвертый вход которого подключен к седьмому выходу дешифратора и к третьему входу второго элемента ИЛИ, четвертый вход которого соединен с четвертым входом первого элемента ИЛИ и с восьмым выходом дешифратора, входы которого являются входом декодера, выходом которого являются выходы первого, второго и третьего элементов ИЛИ.

Таблица

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ РАСПОЗНАВАНИЯ ИЗОБРАЖЕНИЯ ОБЪЕКТА | 1992 |

|

RU2054196C1 |

| Устройство для определения ядер нелинейных объектов | 1981 |

|

SU1008747A1 |

| Устройство для сопряжения канала передачи данных с магистралью | 1986 |

|

SU1444787A1 |

| Устройство автоматизированной подготовки программ для станков с ЧПУ | 1986 |

|

SU1354160A1 |

| Программно-управляемый генератор синусоидальных колебаний | 1985 |

|

SU1451830A1 |

| Генератор сигналов сложной формы | 1980 |

|

SU983692A1 |

| Полевая телеметрическая сейсмическая станция | 1986 |

|

SU1368837A1 |

| Устройство для кодирования аналоговых сигналов | 1989 |

|

SU1624696A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1030801A1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО ПОИСКА КАНАЛОВ РАДИОСВЯЗИ | 2011 |

|

RU2450447C1 |

Изобретение относится к электросвязи. Цель изобретения - повышение помехоустойчивости. Устройство для передачи и приема цифровых сигналов содержит на передающей стороне источник 1 цифрового сигнала, формирователь (Ф) 5 тактовых импульсов, Ф 8 синхросигнала, триггер 10, согласующий блок 14, а на приемной стороне получатель 22 цифрового сигнала, блок выделения 23 синхросигнала, согласующий блок 24, фильтр 25, Ф 26 импульсов, эл-т И 27, триггеры 30, 31 и 32, одновибраторы 33 и 34, резонансный блок 36, инвертор 37 и приемник 45 тактового сигнала. Для повышения помехоустойчивости в устройство введены на передающей стороне дешифраторы 2 и 7, дифференцирующий блок 3, эл-т ИЛИ 4, Ф 6 импульсов, коммутаторы 9 и 13, регистры 11 и 12 сдвига, шифратор 15, блоки 16, 17 и 18 буферной памяти и сумматоры 19, 20 и 21 по модулю два, а на приемной стороне эл-ты И 28 и 29, одновибратор 35, дифференцирующие блоки 38 и 39, счетный триггер 40, регистр 41 сдвига, блок буферной памяти 42, декодер 43 и эл-т ИЛИ-НЕ 44. 2 з.п. ф-лы, 3 ил.

Двоичный сигнал на входе шифратора000 001 010 011 100 101 МО 111

Троичный сигнал на выходе шифратора 1502 12 01 22 11 Ю 21 20

, лиц а2

Сигнал с выходов блоков 17 и 18 буферной памяти

О О О

Сигнал с выхода элемента ИЛИ 4

Выходной сигнал сумматоров 19 и 20 по модулю два

О О О

| Устройство для передачи и приема цифровых сигналов | 1980 |

|

SU978375A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1990-05-23—Публикация

1988-06-27—Подача