йены соответственно с пятым выходом блока памяти микрокоманд и первым входом второго элемента ИЛИ, второй вход которого соединен с входом начальной установки устройства и входом сброса регистра начального адреса, выход второго элемента ИЛИ соединен с нулевым входом триггера, прямой выход которого соединен с вторым входом третьего элемента ИЛИ и управляющим уходом регистра начального адреса, шестой выход блока памяти микрокоманд является управляющим выходом устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки программ | 1986 |

|

SU1410038A1 |

| Устройство для микропрограммного управления | 1983 |

|

SU1188742A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1354192A1 |

| Микропрограммное устройство управления с контролем | 1985 |

|

SU1267414A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1522203A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1310816A1 |

| Микропрограммный процессор | 1986 |

|

SU1462339A1 |

| Микропрограмный процессор | 1980 |

|

SU875385A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1183964A1 |

| Микропрограммное устройство управления | 1981 |

|

SU1015383A1 |

МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ И ОТЛАДКИ МИКРОПРОГРАММ ПРОЦЕССОРА, содержащее регистр микропрограммного адреса, блок памяти микрокоманд, дешифратор, генератор тактовых импульсов, регистр начального адреса, первый и второй коммутаторы адреса, два элемента И, причем выход регистра микропрограммного адреса объединен с выходом регистра начального адреса и с входом блока памяти микрокоманд, первый и второй выходы которого соединены соответственно с входом дешифратора и с первыми информационными входами коммутагоров адреса, вторые информационные входы которых соединены с третьим выходом блока памяти микрокоманд, четвертый выход которого соединен с третьими информационными входами коммутаторов адреса, четвертые информационные входы которых подключены к шине внешних запросов, а выходы соединены соответственно с первыми информационными входами регистра микропрограммного адреса и регистра начального адреса, входы синхронизации которых соединены соответственно с выходами первого и второго элементов-И, первые входы которых соединены с выходом генератора тактовых импульсов, управляюшие входы коммутаторов адреса соединены с шиной внешних условий, отличающееся тем, что, с целью сокрашения аппаратурных затрат для отладки микропрограмм, в него введены триггер, счетчик микрокоманд, два регистра ветвления, две схемы сравнения, коммутатор признаков, четыре элемента ИЛИ, третий элемент И, причем первый и второй выходы дешифратора соединены соответственно с первыми входами третьего и четвертого элементов ИЛИ, выходы которых соединены с вторыми входами соответственно первого и второго элементов И, третий выход дешифратора соединен с единичным входом триггера, инверсный выход которого соединен с вторым входом четвертого элемента ИЛИ, управляюш.им входом регистра микропрограммного адреса и первым входом третьего элемента И, второй вход и вы ход которого соединены соответственно с вы(Л ходом генератора тактовых импульсов и счетным входом счетчика микрокоманд, информационный вход и выход которого соединены соответственно с четвертым выходом дешифратора и управляюш.им входом коммутатора признаков, первый информационный вход которого подключен к выходу первого элемента ИЛИ, первый вход которого соединен с выходом первой схемы сравнения, первый вход которой подключен к выходу а первого регистра ветвления, информацион00 ный вход которого соединен с шиной внешсо оо них запросов, установочным входом счетчика микрокоманд и информационными входами первого и второго регистров ветвления, управляющий вход первого регистра ветвления соединен с пятым выходом дешифратора, шестой выход которого соединен с управляюшим входом второго регистра ветвления, выход которого соединен с первым входом второй схемы сравнения, второй вход которой соединен с вторым входом первой схемы сравнения и выходом регистра микропрограммного адреса, выход второй схемы сравнения соединен с вторым входом первого элемента ИЛИ, второй информационный вход и выход коммутатора признака соеди

1

Изобретение относится к вычислительной технике и может найти применение при создании специализированных и универсальных микропрограммируемых процессоров.

Известны системы логического и функционального моделирования для отладки алгоритмов, логики функционирования микропрограмм 1.

Недостатком данных систем моделирования является использование больщих вычислительных мащин с высокой стоимостью машинного и, как правило, пакетной обработкой, что повыщает стоимость отладки и увеличивает ее время. Кроме того, уровень достоверности отладки низок.

Наиболее близким к изобретению является микропрограммный процессор, содержащий регистр микропрограммного адреса, блок хранения микрокоманд, дешифратор, генератор импульсов, регистр начального адреса, два коммутатора адреса, два элемента И, причем выход регистра микропрограммного адреса объединен с выходом регистра начального адреса и соединен с входом блока хранения микрокоманд, первый и второй выходы которого соединены соответственно с входом дешифратора и с первыми входами коммутаторов адреса, вторые входы которых соединены с третьим выходом блока хранения микрокоманд, четвертый выход которого соединен с третьими входами коммутаторов адреса, четвертые входы которых подключены к внешней шине, а выходы соединены соответственно с первым входом регистра микропрограммного адреса и с первым входом регистра начального адреса, вторые входы которых соединены соответственно с выходами второго и первого элементов И, первые входы которых соединены с выходом генератора импульсов, пятые входы коммутаторов адреса соединены с шиной внешнего условия 2.

Недостатком известного устройства является использование кроме специального программного обеспечения дополнительного оборудования, фактически не используемого

при выполнении рабочих микропрограмм процессора.

Целью изобретения является сокращение аппаратурных затрат, для отладки микропрограмм.

Поставленная цель достигается тем, что в микропрограммное устройство управления и отладки микропрограмм процессора, содержащее регистр микропрограммного адреса, блок памяти микрокоманд, дешифратор, генератор тактовых импульсов, регистр начального адреса, первый и второй коммутаторы адреса, два элемента И, причем выход регистра микропрограммного адреса объединен с выходом регистра начального адреса и соединен с входом блока памяти микрокоманд, первый и второй выходы которого соединены соответственно с входом дещифратора и с первыми информационными входами коммутаторов адреса, вторые информационные входы которых соединены с третьим входом блока памяти микрокоманд, четвертый выход которого соединен с третьими информационными входами коммутаторов адреса, четвертые информационные входы которых подключены к шине внешних запросов, а выхО;С1ы соединены соответственно с первыми информационными входами регистра микропрограммного адреса и

0 регистра начального адреса, входы синхронизации которых соединены соответственно с выходами первого и второго элементов И, первые входы которых соединены с выходом генератора тактовых импульсов, управляющие входы коммутаторов адреса соединены с

5 шиной внешних условий, введены триггер, счетчик микрокоманд, два регистра ветвления, две схемы сравнения, коммутатор признаков, четыре элемента ИЛИ, третий элемент И, причем первый и второй выходы

0 дешифратора соединены соответственно с первыми входами третьего и четвертого элементов ИЛИ, выходы которых соединены с вторыми входами соответственно первого и второго элементов И, третий выход дешифратора - с единичным входом триггера, первый выход которого соединен с вторым

входом четвертого элемента ИЛИ, управляющим входом регистра микропрограммного адреса и первым входом третьего элемента И, второй вход и выход которого соединены соответственно с выходом генератора тактовых импульсов и счетным входом счетчика микрокоманд, информационный вход и выход которого соединены соответственно с четвертым выходом дешифратора и управляющим входом коммутатора признаков, первый информационный вход которого подключен к выходу первого элемента ИЛИ, первый вход которого соединен с выходом первой схемы сравнения, первый вход которой подключен к выходу первого регистра ветвления, информационный вход которого соединен с шиной внешних запросов, установочным входом счетчика микрокоманд и информационным входом второго регистра ветвления, управляющий вход первого регистра ветвления соединен с пятым выходом дешифратора, шестой выход которого соединен с управляющим входом второго регистра ветвления, выход которого соединен с первым входом второй схемы сравнения, второй вход которой соединен с вторым входом первой схемы сравнения и выходом регистра микропрограммного адреса, выход второй схемы сравнения - с вторым входом первого элемента ИЛИ, второй информационный вход и выход коммутатора признака - соответственно с пятым выходом блока памяти микрокоманд и первым входом второго элемента ИЛИ, второй вход которого соединен с входом начальной установки устройства и входом сброса регистра начального адреса, выход второго элемента ИЛИ - с нулевым входом триггера, прямой выход которого соединен с вторым входом третьего элемента ИЛИ и управляющим входом регистра начального адреса, щестой выход блока хранения макрокоманд является управляющим выходом устройства.

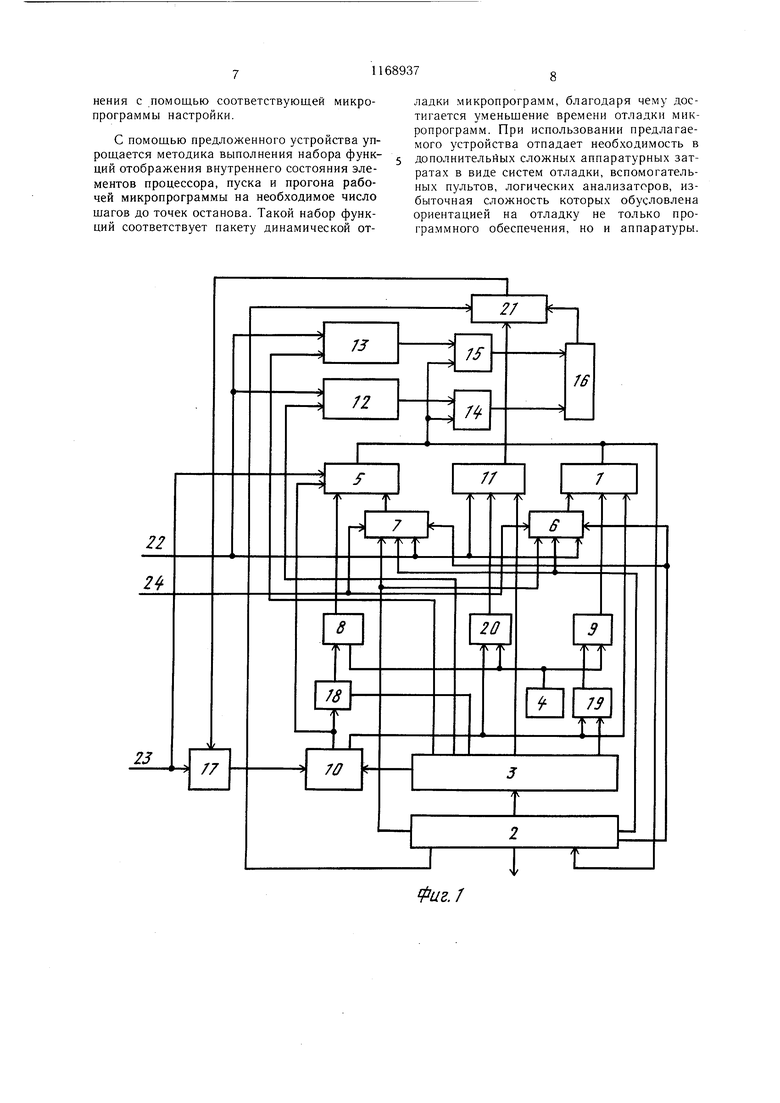

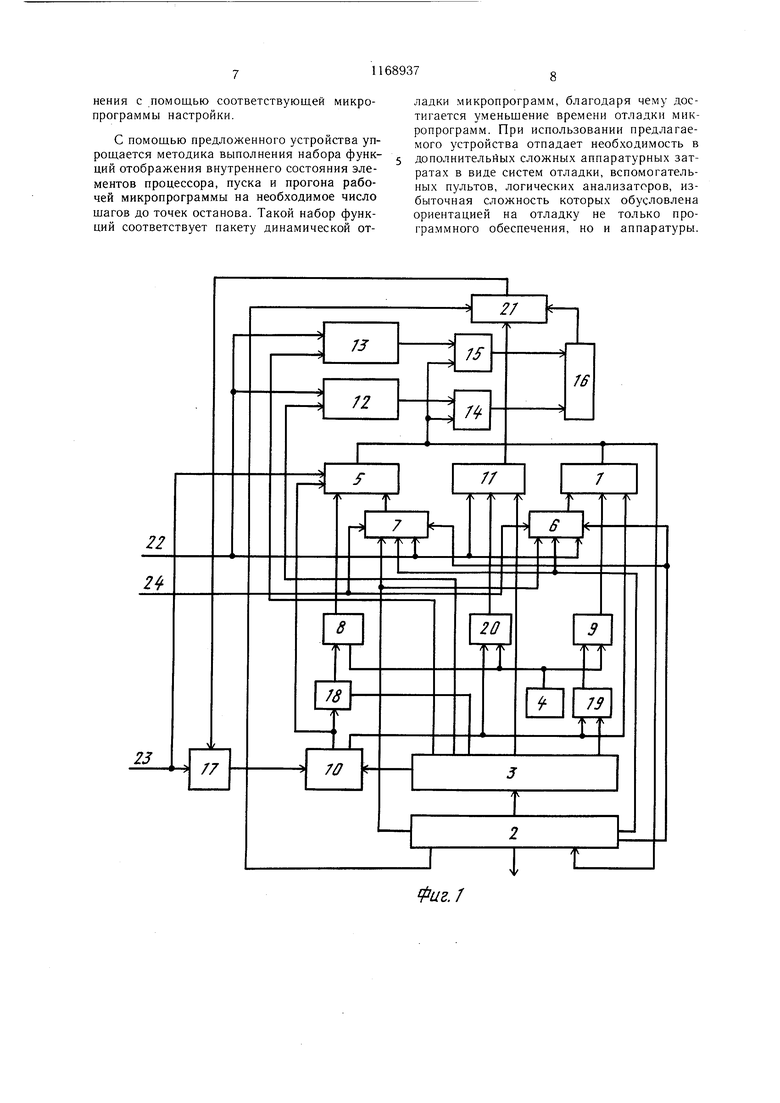

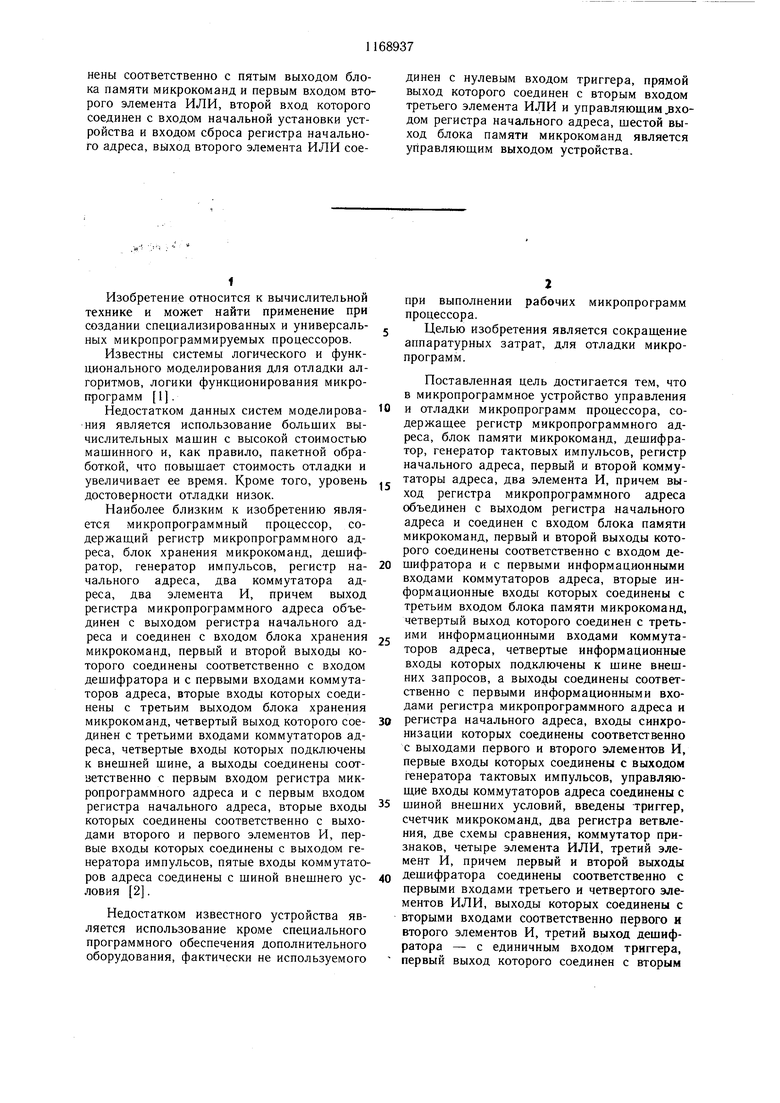

На фиг. 1 приведена структурная схема устройства; на фиг. 2 - временные диаграммы работы устройства; на фиг. 3 - блок-схема алгоритма работы устройства в режиме настройки.

Устройство содержит регистр 1 микропрограммного адреса, блок 2 памяти микрокоманд, дещифратор 3, генератор 4 тактовых импульсов, регистр 5 начального адреса, первый 6 и второй 7 коммутаторы адреса, первый 9 и второй 8 элементы И, триггер 10, счетчик 11 микрокоманд, первый 12 и второй 13 регистры ветвления, первая 14 и вторая 15 схемы сравнения, первый 16 второй 17, третий 18 и четвертый 19 элементы ИЛИ, третий элемент И 20, коммутатор 21 признаков, шину 22 внешних запросов, вход 23 начальной установки, шину 24 внешних условий.

Устройство работает в двух режимах, режиме настройки и режиме выполнения рабочей микропрограммы. В исходном состоянии сигнал начальной установки с входа 23 поступает на третий вход регистра 5 начального адреса и через первый в.ход второго элемента ИЛИ 17 на нулевой вход триггера 10, при этом последний устанавливается в нулевое состояние, а в регистре 5 начального адреса устанавливается нулеП«

вой адрес - начальный адрес микропрограммы приема и реализации функции настройки. Единичный разрешающий сигнал с прямого выхода триггера 10 поступает через третий элемент ИЛИ 18 на второй вход первого элемента И 8, обеспечивая поступление синхроимпульсов с выхода генератора 4 импульсов через первый элемент И 8 на второй вход, являющийся синхронизирующим, регистра 5 начального адреса. Кроме того, единичный сигнал с прямого выхода

0 триггера 10 поступает на четвертый вход регистра 5, переводя его выход из третьего состояния (высокий импеданс) в открытое, т.е. подключая выход регистра 5 к входу блока 2. Благодаря этому устройство переводится в режим настройки. В этом режиме регистр 5 адресует блок 2 памяти микрокоманд, обеспечивая считывание из него микрокоманд микропрограммы настройки. Дещифратор 3 из соответствующих полей микрокоманды формирует управляющие сигналы, обеспечивающие выполнение микроопераций в режиме настройки. Дешифратор 3 осуществляет декодирование полей микрокоманды, обеспечивающих управление блоками устройства так же и во втором режиме.

Для формирования адреса следующей микрокоманды код адреса с второго выхода блока 2 памяти микрокоманд поступает через первый вход второго коммутатора 7 адреса на первый вход регистра 5 началь0 ного адреса и записывается в него при поступлении синхроимпульса на второй вход регистра 5 (диаграммы А, Б, В, Г, фиг. 3). Рассмотрим функционирование устройства в режиме настройки на примере настройки устройства на выполнение функции вы пол нения рабочей программы с начального адреса на N шагов. Первый параметр, принимаемый с шины 22 внешних запросов и являющийся адресом микропрограммы, реализующей требуемую функцию настройки, загружается по управляющему коду 10, поступающему с четвертого выхода блока 2 памяти микрокоманд, через второй коммутатор 7 адреса в регистр 5 начального адреса. Тем самым осуществляется выбор нужной микропрограммы, которая будет

интерпретировать последующие параметры, поступающие с внешней шины 22. В данном случае второй параметр, являющийся числом шагов N, поступает с шины 22 внешних запросов на третий вход счетчика 11 микрокоманд, запись в который выполняется по управляюп1.ему сигналу, выдаваемому с четвертого выхода дешифратора 3 на второй вход счетчика 11 микрокоманд. Третий параметр, поступающий с шины 22 внешних запросов на третьи входы первого и второго коммутаторов 6 и 7, передается через первый коммутатор 6 адреса на первый вход регистра 1 микропрограммного адреса. При этом с второго выхода дешифратора 3 выдается микропрограммно задаваемый управляющий сигнал, поступающий на первый вход элемента ИЛИ 19.

При подаче этого сигнала один синхроимпульс проходит через элемент И 9 на второй вход регистра 1, обеспечивая загрузку в него заданного адреса. После этого должен быть загружен в регистр 5 адрес инициализирующей микропрограммы, обеспечивающей загрузку вновь поступающего параметра в качестве кода функции настройки, что может потребоваться при выполнении следующей функции настройки в процессе отладки программы. В конце каждой микропрограммы настройки выполняется переход в режим выполнения рабочей микрокоманды. Это обеспечивается тем, что по окончании микропрогра.ммы настройки с третьего выхода дешифратора 3 управляющий сигнал поступает на первый вход триггера 10 и переводит его в единичное состояние (диаграммы Б и Д, фиг. 3).

Разрешающий единичный сигнал с первого выхода триггера 10, поступая через элемеггг ИЛИ 19 на второй вход элемента И 9, обеспечивает поступление последовательности из N синхроимпульсов с генератора 4 на управляющий вход регистра 1 микропрограммного адреса. Тем самым устройство переводится в режим выполнения N щагов рабочей микропрограммы (диаграммы Е и Ж) фиг. 3).

Выполнение рабочей микропрограммы во втором режиме в зависимости от выбранной ранее функции настройки может осуществляться в следующих вариантах: выполнение рабочей микропрограммы с требуемого адреса, пуск микропрограммы с требуемого или текущего адреса до точек останова, выполнение микропрограммы на определенное число шагов как с заданного, так и с текущего адреса. Режим выполнения рабочей программы обеспечивается подачей разрещающего сигнала с второго выхода триггера 10 на третий вход регистра 1 микропрограммного адреса, подключая его выход к входу блока 2 хранения микрокоманд. Одновременно подачей запрещающего (нулевого) сигнала с инверсного выхода триггера 10 на четвертый вход регистра 5 осуществляется отключение выхода регистра 5 начального адреса от блока 2 памяти микрокоманд. Адресация блока 2 памяти микрокоманд осуществляется с выхода регистра 1 микропрограммного адреса.

Дешифратор 3 формирует управляющие сигналы для выполнения микроопераций коды которых записаны в соответствующих полях каждой микрокоманды, считываемой с первого выхода блока 2 памяти микрокоманд Формирование адреса производится путем подачи кода адреса с второго выхода блока

2 через первый вход первого коммутатора 6 на первый вход регистра I микропрограммного адреса. Выполнение микропрограммы осуществляется без остановки, либо до соответствующей точки останова. Выполнение микропрограммы на определенное число шагов обеспечивается наличием в устройстве счетчика 11 микрокоманд, который при выполнении каждой микрокоманды вычитает единицу из параметра, определенного в режиме настройки.

0 В режиме выполнения рабочей микропрограммы на первый вход счетчика 11 микрокоманд поступает синхроимпульс с выхода элемента И 20. Последний обеспечивает передачу синхроимпульсов с выхода генератора 4, так как на первый вход его поступает разрещающий сигнал с инверсного выхода триггера 10. Когда значение счетчика 11 микрокоманд станет равным нулю, на его выходе формируется управляющий сигнал, который поступает на первый вход

Q коммутатора 21 признака. В соответствии с кодом признака, поступающего из отдельного поля микрокоманды с пятого выхода блока 2 на третий вход коммутатора 21 признака, управляющий сигнал с выхода коммутатора 21 (диаграмма 3, фиг. 3) поступает на первый вход элемента ИЛИ 17 и затем на нулевой вход триггера 10, останавливая выполнение рабочей микропрограммы и переводя устройство в режим настройки. Счетчик 11 микрокоманд, кроме того, может использован для реализации пошагового выполнения рабочей микропрограммы.

Аналогично при выполнении рабочих программ до точек остановок, хранящихся в

5 регистрах 12 и 13 ветвления, схемы 14 и 15 сравнения обеспечивают проверку на совпадение точек останова с текущим микропрограммным адресом, сформированным в регистре 1 микрокомандного адреса. В случае совпадения управляющий сигнал с выхода любой из схем 14 и 15 сравнения через элемент ИЛИ 16, коммутатор 21 признаков, элемент ИЛИ 17 поступает на нулевой вход триггера 10, переводя его в нулевое состояние, а устройство - в режим настройки. После перехода в режим настройки состояние элементов памяти процессора, управляемого предлагаемым устройством, может быть выведено для индикации и изменения с помощью соответствующей микропрограммы настройки.

С помощью предложенного устройства упрощается методика выполнения набора функций отображения внутреннего состояния элементов процессора, пуска и прогона рабочей микропрограммы на необходимое число щагов до точек останова. Такой набор функций соответствует пакету динамической отладки микропрограмм, благодаря чему достигается уменьщение времени отладки микропрограмм. При использовании предлагаемого устройства отпадает необходимость в дополнительных сложных аппаратурных затратах в виде систем отладки, вспомогательных пультов, логических анализаторов, избыточная сложность которых обусловлена ориентацией на отладку не только программного обеспечения, но и аппаратуры.

Фиг. 7

С Начало I

Установка , режима /застройки

С (онец

иг.З

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Клингман | |||

| Проектирование микропроцессорных систем | |||

| М., «Мир,-1980 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Микропрограммный процессор | 1980 |

|

SU947868A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-07-23—Публикация

1984-01-26—Подача