ел

оо со

00

J

Изобретение относится к вычислительной технике и может быть использовано в системах обработки данных в качестве субпроцессора обмена информацией между абонентами и центральным процессором.

Целью изобретения является увеличение быстродействия устройства.

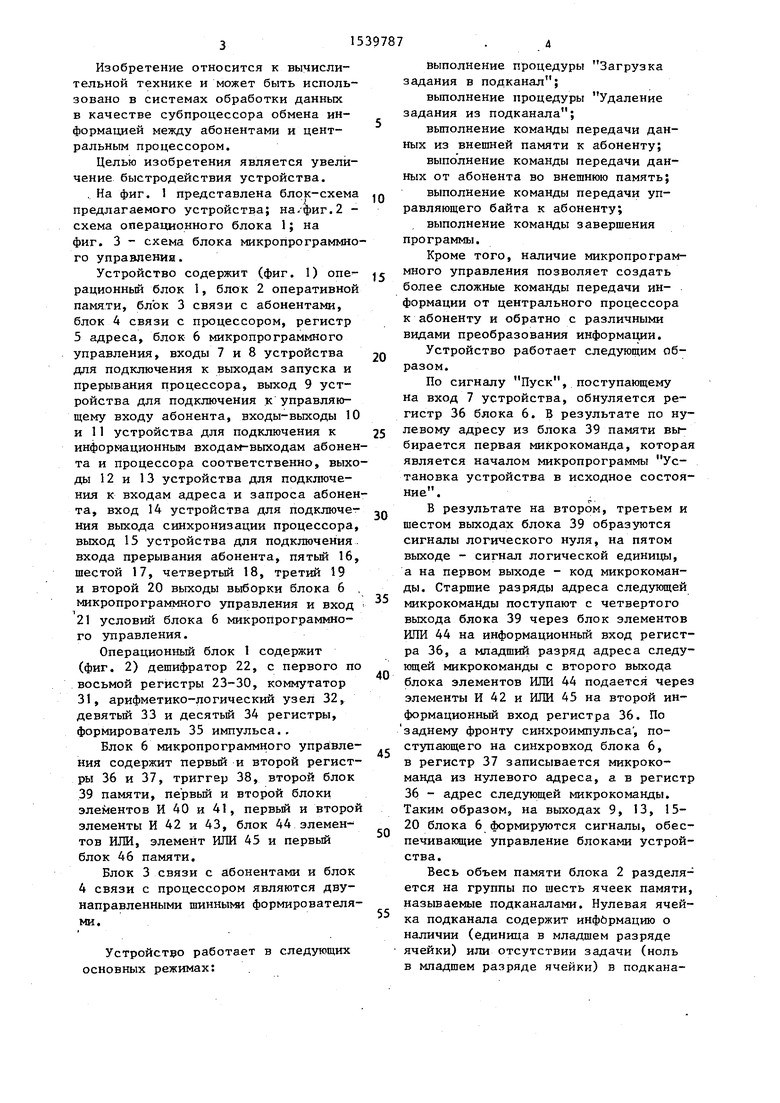

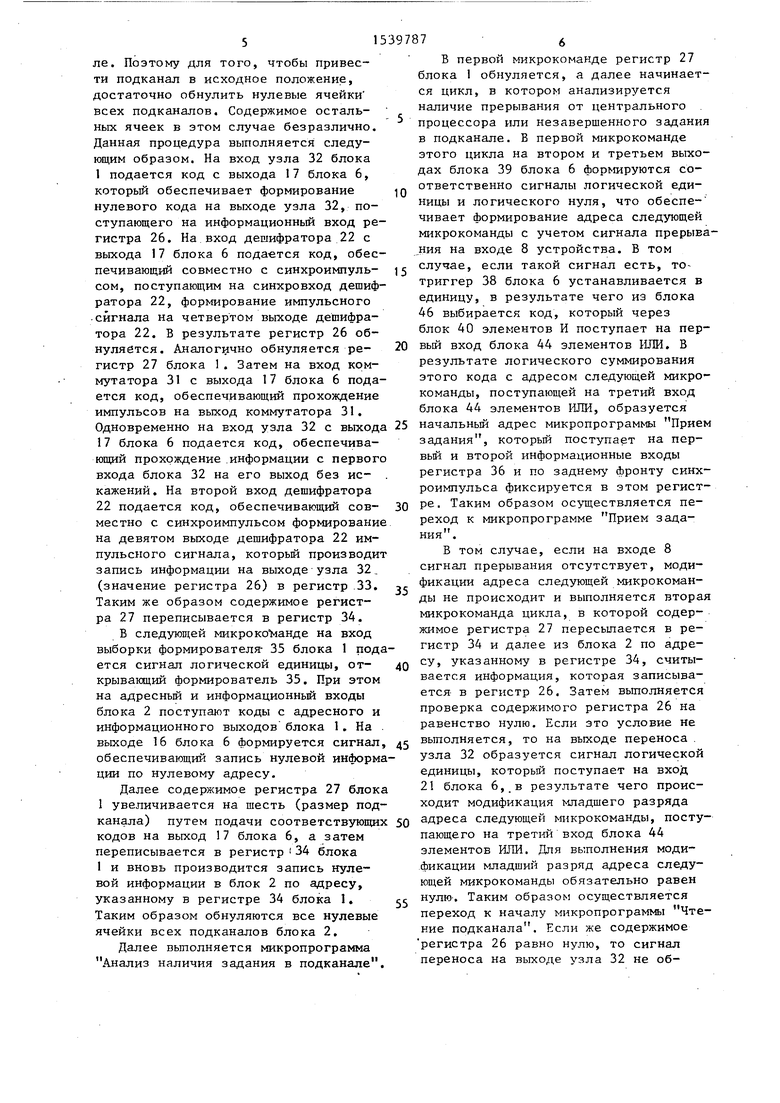

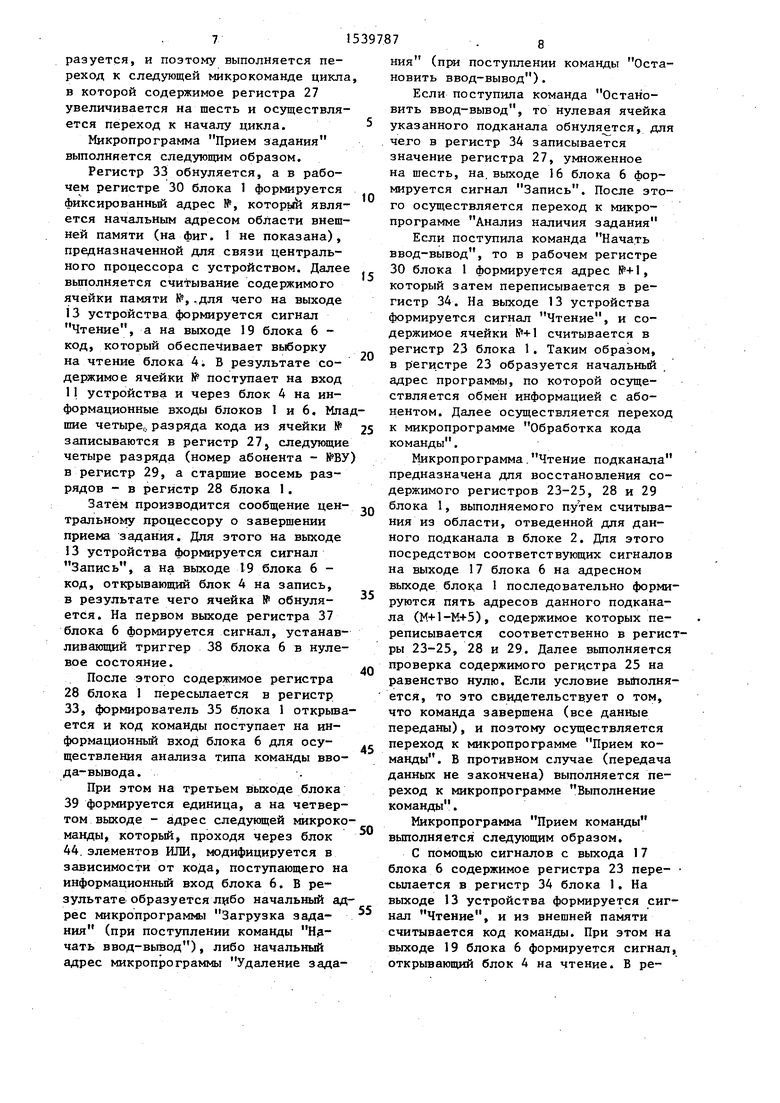

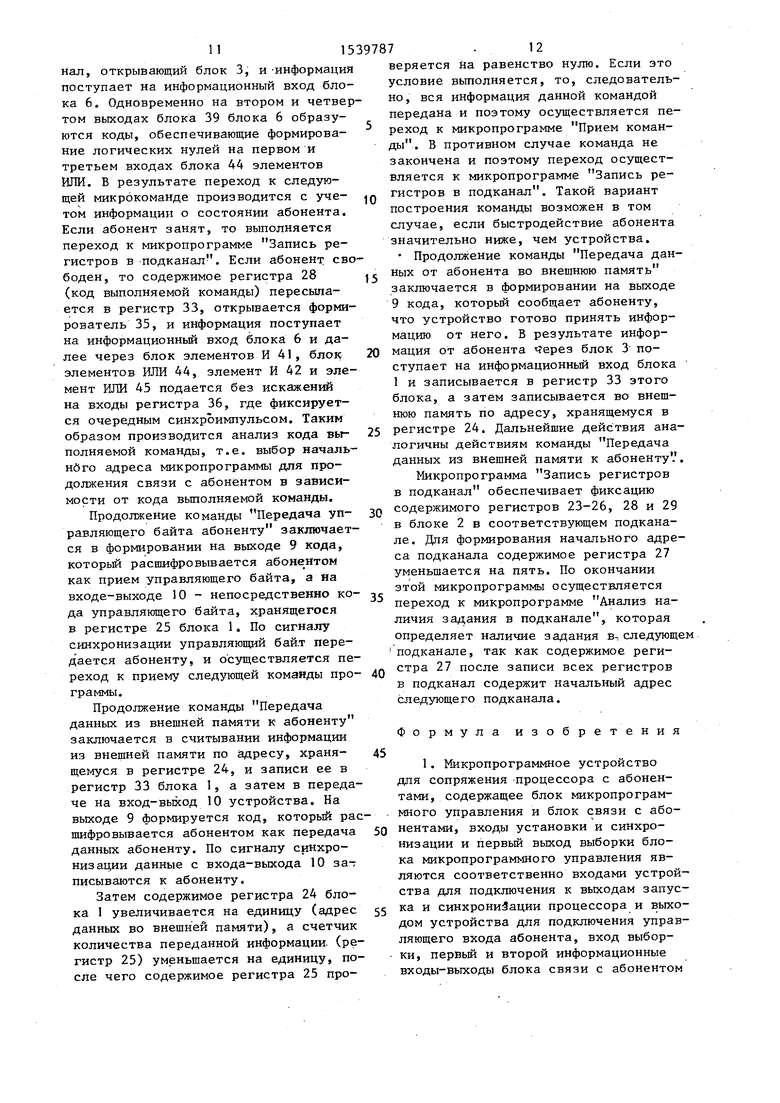

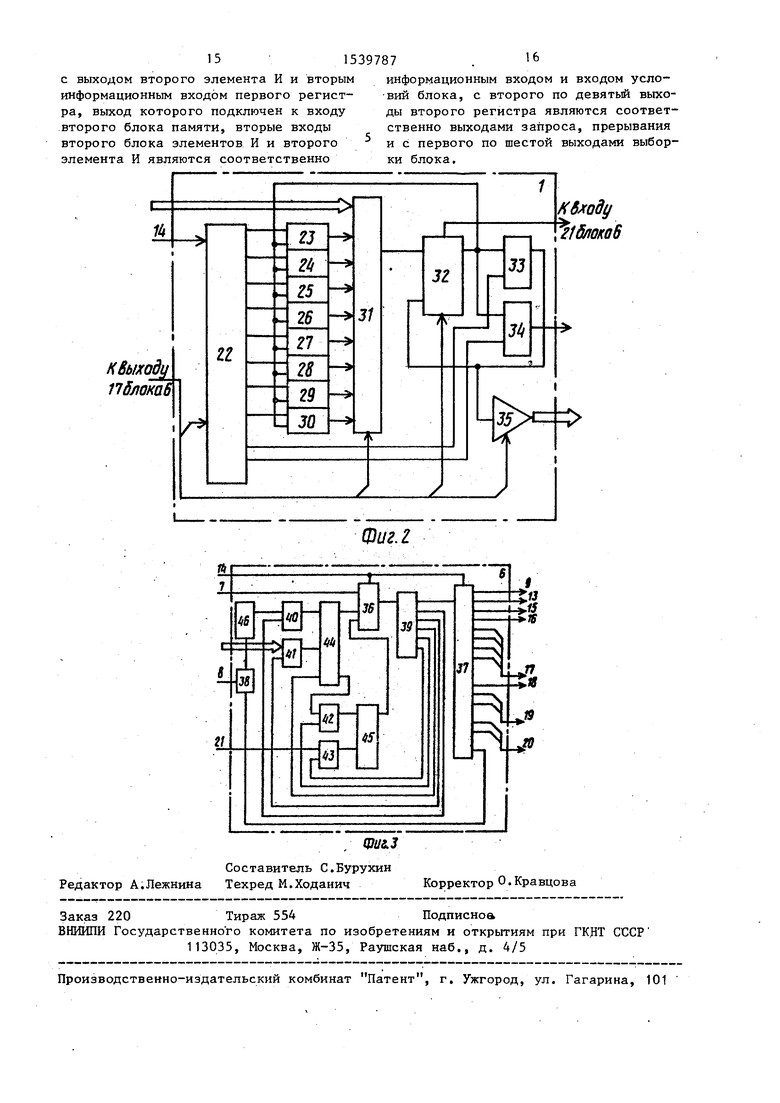

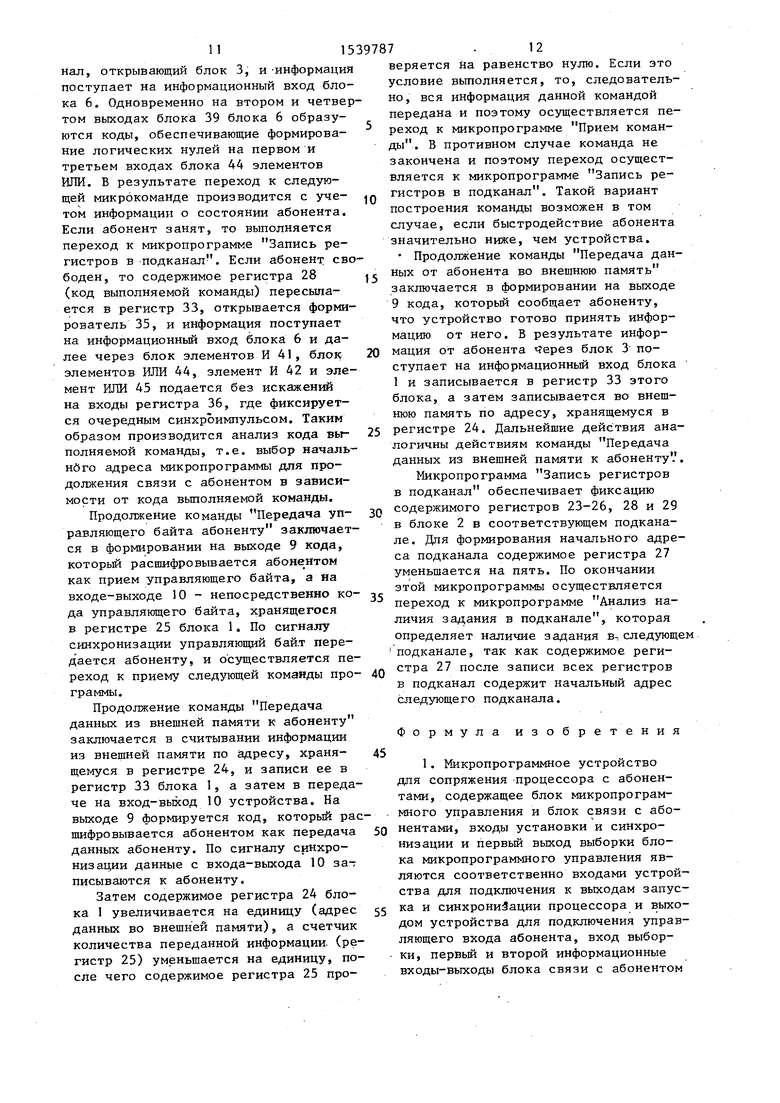

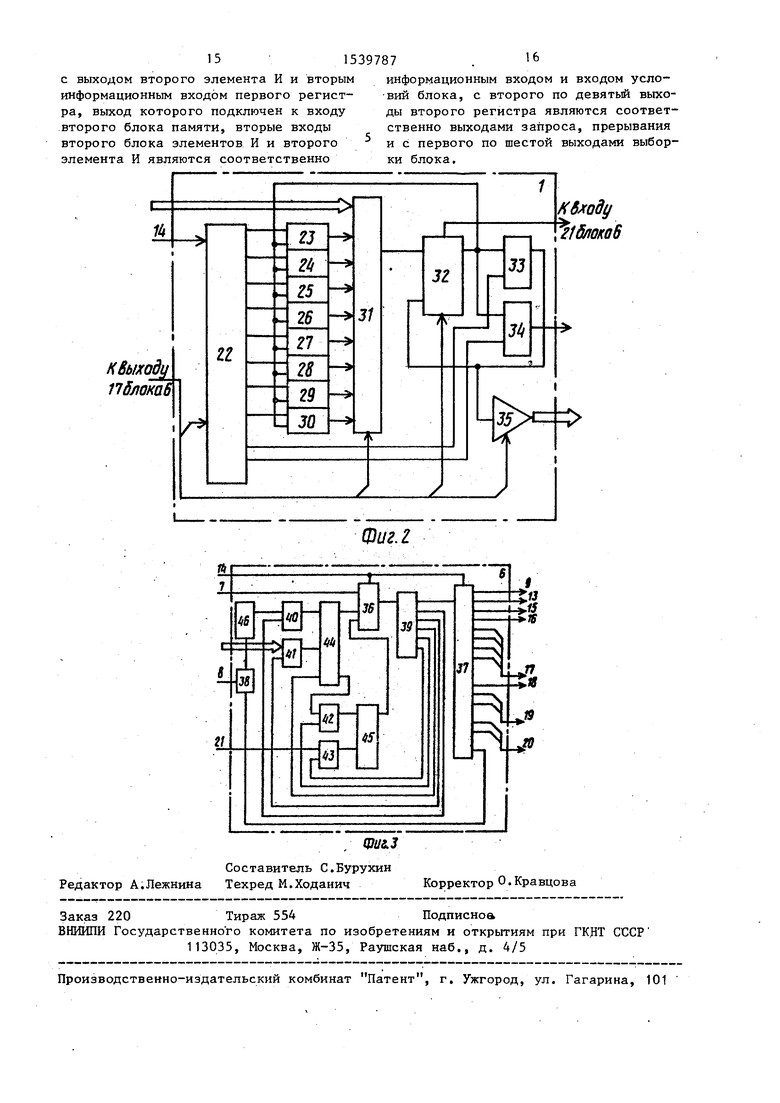

На фиг. 1 представлена блок-схема предлагаемого устройства; на.фиг.2 - схема операционного блока 1; на фиг. 3 - схема блока микропрограммного управления.

Устройство содержит (фиг. 1) операционный блок 1, блок 2 оперативной памяти, блок 3 связи с абонентами, блок 4 связи с процессором, регистр 5 адреса, блок 6 микропрограммного управления, входы 7 и 8 устройства для подключения к выходам запуска и прерывания процессора, выход 9 устройства для подключения к управляющему входу абонента, входы-выходы 10 и 11 устройства для подключения к информационным входам-выходам абонента и процессора соответственно, выходы 12 и 13 устройства для подключения к входам адреса и запроса абонента, вход 14 устройства для подключения выхода синхронизации процессора, выход 15 устройства для подключения входа прерывания абонента, пятый 16, шестой 17, четвертый 18, третий 19 и второй 20 выходы выборки блока 6 микропрограммного управления и вход 21 условий блока 6 микропрограммного управления.

Операционный блок 1 содержит (фиг. 2) дешифратор 22, с первого по восьмой регистры 23-30, коммутатор 31, арифметико-логический узел 32, девятый 33 и десятый 34 регистры, формирователь 35 импульса..

Блок 6 микропрограммного управления содержит первый и второй регистры 36 и 37, триггер 38, второй блок 39 памяти, первый и второй блоки элементов И 40 и 41, первый и второй элементы И 42 и 43, блок 44 элементов ИЛИ, элемент ИЛИ 45 и первый блок 46 памяти.

Блок 3 связи с абонентами и блок 4 связи с процессором являются двунаправленными шинными формирователями.

Устройство работает в следующих основных режимах:

5

0

5

0

5

0

5

0

5

выполнение процедуры Загрузка задания в подканал ;

выполнение процедуры Удаление задания из подканала ;

выполнение команды передачи данных из внешней памяти к абоненту;

выполнение команды передачи данных от абонента во внешнюю память;

выполнение команды передачи управляющего байта к абоненту;

выполнение команды завершения программы.

Кроме того, наличие микропрограммного управления позволяет создать более сложные команды передачи информации от центрального процессора к абоненту и обратно с различными видами преобразования информации.

Устройство работает следующим образом.

По сигналу Пуск, поступающему на вход 7 устройства, обнуляется регистр 36 блока 6. В результате по нулевому адресу из блока 39 памяти выбирается первая микрокоманда, которая является началом микропрограммы Установка устройства в исходное состояние .

В результате на втором, третьем и шестом выходах блока 39 образуются сигналы логического нуля, на пятом выходе - сигнал логической единицы, а на первом выходе - код микрокоманды. Старшие разряды адреса следующей микрокоманды поступают с четвертого выхода блока 39 через блок элементов ИЛИ 44 на информационный вход регистра 36, а младший разряд адреса следующей микрокоманды с второго выхода блока элементов ИЛИ 44 подается через элементы И 42 и ИЛИ 45 на второй информационный вход регистра 36. По заднему фронту синхроимпульса , поступающего на синхровход блока 6, в регистр 37 записывается микрокоманда из нулевого адреса, а в регистр 36 - адрес следующей микрокоманды. Таким образом, на выходах 9, 13, 15- 20 блока 6 формируются сигналы, обеспечивающие управление блоками устройства.

Весь объем памяти блока 2 разделяется на группы по шесть ячеек памяти, называемые подканалами. Нулевая ячейка подканала содержит информацию о наличии (единица в младшем разряде ячейки) или отсутствии задачи (ноль в младшем разряде ячейки) в подкана5

ле. Поэтому для того, чтобы привести подканал в исходное положение, достаточно обнулить нулевые ячейки всех подканалов. Содержимое остальных ячеек в этом случае безразлично. Данная процедура выполняется следующим образом. На вход узла 32 блока 1 подается код с выхода 17 блока 6, которьй обеспечивает формирование нулевого кода на выходе узла 32, поступающего на информационный вход регистра 26. На вход дешифратора 22 с выхода 17 блока 6 подается код, обеспечивающий совместно с синхроимпульсом, поступающим на синхровход дешифратора 22, формирование импульсного сигнала на четвертом выходе дешифратора 22. В результате регистр 26 обнуляется. Аналогично обнуляется регистр 27 блока 1. Затем на вход коммутатора 31 с выхода 17 блока 6 подается код, обеспечивающий прохождение импульсов на выход коммутатора 31.

В первой микрокоманде регистр 27 блока 1 обнуляется, а далее начинается цикл, в котором анализируется наличие прерывания от центрального 5 процессора или незавершенного задания в подканале. В первой микрокоманде этого цикла на втором и третьем выходах блока 39 блока 6 формируются соответственно сигналы логической единицы и логического нуля, что обеспечивает формирование адреса следующей микрокоманды с учетом сигнала прерывания на входе 8 устройства. В том случае, если такой сигнал есть, то- триггер 38 блока 6 устанавливается в

10

15

единицу, в результате чего из блока 46 выбирается код, который через блок 40 элементов И поступает на пер- 20 вый вход блока 44 элементов ИЛИ. В результате логического суммирования этого кода с адресом следующей микрокоманды, поступающей на третий вход блока 44 элементов ИЛИ, образуется

Одновременно на вход узла 32 с выхода 25 начальный адрес микропрограммы Прием

17 блока 6 подается код, обеспечивающий прохождение информации с первого входа блока 32 на его выход без искажений. На второй вход дешифратора 22 подается код, обеспечивающий совместно с синхроимпульсом формирование на девятом выходе дешифратора 22 импульсного сигнала, которьй производит запись информации на выходе узла 32 (значение регистра 26) в регистр 33. Таким же образом содержимое регистра 27 переписывается в регистр 34.

В следующей микрокоманде на вход выборки формирователя- 35 блока 1 подается сигнал логической единицы, от- крывающий формирователь 35. При этом на адресный и информационный входы блока 2 поступают коды с адресного и информационного выходов блока 1. На выходе 16 блока 6 йормируется сигнал, обеспечивающий запись нулевой информации по нулевому адресу.

Далее содержимое регистра 27 блока 1 увеличивается на шесть (размер подканала) путем подачи соответствующих кодов на выход 17 блока 6, а затем переписывается в регистр 34 блока 1 и вновь производится запись нулевой информации в блок 2 по адресу, указанному в регистре 34 блока 1. Таким образом обнуляются все нулевые ячейки всех подканалов блока 2.

Далее выполняется микропрограмма Анализ наличия задания в подканале.

97876

В первой микрокоманде регистр 27 блока 1 обнуляется, а далее начинается цикл, в котором анализируется наличие прерывания от центрального 5 процессора или незавершенного задания в подканале. В первой микрокоманде этого цикла на втором и третьем выходах блока 39 блока 6 формируются соответственно сигналы логической единицы и логического нуля, что обеспечивает формирование адреса следующей микрокоманды с учетом сигнала прерывания на входе 8 устройства. В том случае, если такой сигнал есть, то- триггер 38 блока 6 устанавливается в

10

15

единицу, в результате чего из блока 46 выбирается код, который через блок 40 элементов И поступает на пер- вый вход блока 44 элементов ИЛИ. В результате логического суммирования этого кода с адресом следующей микрокоманды, поступающей на третий вход блока 44 элементов ИЛИ, образуется

0

5

0 5

0 5

задания, который поступает на первый и второй информационные входы регистра 36 и по заднему Аронту синхроимпульса фиксируется в этом регистре. Таким образом осуществляется переход к микропрограмме Прием задания.

В том случае, если на входе 8 сигнал прерывания отсутствует, модификации адреса следующей микрокоманды не происходит и выполняется вторая микрокоманда цикла, в которой содержимое регистра 27 пересылается в регистр 34 и далее из блока 2 по адресу, указанному в регистре 34, считывается информация, которая записывается в регистр 26. Затем выполняется проверка содержимого регистра 26 на равенство нулю. Если это условие не выполняется, то на выходе переноса узла 32 образуется сигнал логической единицы, которьй поступает на вход 21 блока 6,.в результате чего происходит модификация младшего разряда адреса следующей микрокоманды, поступающего на третий вход блока 44 элементов ИЛИ. Для выполнения модификации младший разряд адреса следующей микрокоманды обязательно равен нулю. Таким образом осуществляется переход к началу микропрограммы Чтение подканала. Если же содержимое регистра 26 равно нулю, то сигнал переноса на выходе узла 32 не об

разуется, и поэтому выполняется переход к следующей микрокоманде цикла в которой содержимое регистра 27 увеличивается на шесть и осуществляется переход к началу цикла.

Микропрограмма Прием задания выполняется следующим образом.

Регистр 33 обнуляется, а в рабочем регистре 30 блока 1 формируется фиксированный адрес №, который является начальным адресом области внешней памяти (на фиг. 1 не показана), предназначенной для связи центрального процессора с устройством. Далее выполняется считывание содержимого ячейки памяти №,.для чего на выходе 13 устройства формируется сигнал Чтение, а на выходе 19 блока 6 - код, который обеспечивает выборку на чтение блока 4. В результате содержимое ячейки № поступает на вход 11 устройства и через блок 4 на информационные входы блоков 1 и 6. Млашие четырег, разряда кода из ячейки № записываются в регистр 27} следующие четыре разряда (номер абонента - №ВУ в регистр 29, а старшие восемь разрядов - в регистр 28 блока 1.

Затем производится сообщение центральному процессору о завершении приема задания. Для этого на выходе 13 устройства формируется сигнал Запись, а на выходе 19 блока 6

код, открывающий блок 4 на запись, в результате чего ячейка № обнуляется. На первом выходе регистра 37 блока 6 формируется сигнал, устанавливающий триггер 38 блока 6 в нулевое состояние.

После этого содержимое регистра 28 блока 1 пересыпается в регистр 33, формирователь 35 блока 1 открывается и код команды поступает на информационный вход блока 6 для осуществления анализа типа команды ввода-вывода.

При этом на третьем выходе блока 39 формируется единица, а на четвертом выходе - адрес следующей микрокоманды, который, проходя через блок 44 элементов ИЛИ, модифицируется в зависимости от кода, поступающего на информационный вход блока 6. В результате образуется либо начальный адрес микропрограммы Загрузка задания (при поступлении команды Начать ввод-вывод), либо начальный адрес микропрограммы Удаление зада0

5

5

0

0

5

0

5

0

5

ния (при поступлении команды Остановить ввод-вывод).

Если поступила команда Остановить ввод-вывод, то нулевая ячейка указанного подканала обнуляется, для чего в регистр 34 записывается значение регистра 27, умноженное на шесть, на. выходе 16 блока 6 формируется сигнал Запись. После этого осуществляется переход к микропрограмме Анализ наличия задания

Если поступила команда Начать ввод-вывод, то в рабочем регистре 30 блока 1 формируется адрес №+1, который затем переписывается в регистр 34. На выходе 13 устройства формируется сигнал Чтение, и содержимое ячейки К«+1 считывается в регистр 23 блока 1. Таким образом, в регистре 23 образуется начальный адрес программы, по которой осуществляется обмен информацией с абонентом. Далее осуществляется переход к микропрограмме Обработка кода команды.

Микропрограмма Чтение подканала предназначена для восстановления содержимого регистров 23-25, 28 и 29 блока 1, выполняемого путем считывания из области, отведенной для данного подканала в блоке 2. Для этого посредством соответствующих сигналов на выходе 17 блока 6 на адресном выходе блока 1 последовательно формируются пять адресов данного подканала (М+1-М+5), содержимое которых переписывается соответственно в регистры 23-25, 28 и 29. Далее выполняется проверка содержимого регистра 25 на равенство нулю. Если условие выполняется, то это свидетельствует о том, что команда завершена (все данные переданы), и поэтому осуществляется переход к микропрограмме Прием команды. В противном случае (передача данных не закончена) выполняется переход к микропрограмме Выполнение команды.

Микропрограмма Прием команды выполняется следующим образом.

С помощью сигналов с выхода 17 блока 6 содержимое регистра 23 пере- сылается в регистр 34 блока 1. На выходе 13 устройства формируется сигнал Чтение, и из внешней памяти считывается код команды. При этом на выходе 19 блока 6 формируется сигнал, открывающий блок 4 на чтение. В результате код команды поступает на информационные входы блоков 1 и 6. Старшие восемь разрядов записываются в регистр 28, а младшие восемь - в регистр 25 блока 1. Адрес следующей микрокоманды определяется кодом, поступающим на информационный вход блока 6, для чего на .вторые входы блока 41 элементов И подается сигнал логической единицы с соответствующего выхода блока 39.

В том случае, если поступила команда безусловного перехода, переход осуществляется к микропрограмме Безусловный переход, Во втором слове этой команды указывается адрес следующей команды программы. Поэтому с помощью сигналов на выходе 17 блока 6 содержимое регистра 23 блока 1 увеличивается на единицу и записывается в регистр 34. Далее выполняется операция чтения внешней памяти по адресу в регистре 34, и информация записывается в регистр 23 блока 1, т.е. записывается адрес следующей команды программы. На этом действия команды заканчиваются и осуществляется переход к микропрограмме Прием команды.1.

В том случае, если поступили команды Передача данных из внешней памяти к абоненту или Передача данных от абонента во внешнюю память, переход осуществляется к началу микропрограммы, в которой содержимое регистра 23 блока 1 увеличивается на единицу, а затем из внешней памяти по адресу, указанному в регистре 23, считывается информация и записывается в регистр 24 блока 1. По смыслу эта информация представляет собой начальный адрес зоны внешней памяти, в которую или из которой данные передаются соответственно от абонента или к абоненту. Далее содержимое регистра 23 увеличивается на единицу и осуществляется переход к микропрограмме Выполнение команды.

Если поступила команда Передача управляющего байта абоненту, то осуществляется переход к микропрограмме, где содержимое регистра 23 увеличивается на единицу, а затем выполняется переход к микропрограмме Выполнение команды.

Если поступила команда Заверше-- ние программы ввода-вывода, то осуществляется переход к микропрограмме, которая выполняется следующим обра

10

3978710

зом. В регистре 34 формируется адрес №+2, по которому во внешнюю память записывается предварительно сформированное содержимое регистра 33, представляющее собой код завершения программы ввода-вывода по команде Завершение программы ввода-вывода. Регистр 26 обнуляется, т.е. аннулируется признак наличия задания в подканале. Кроме того, на выходе 15 формируется сигнал Прерывание, которым центральный процессор оповещается о завершении программы ввода-вывода, причем в ячейке Кч2 внешней памяти указана причина, по которой ввод-вывод завершен. Затем осуществляется переход к микропрограмме Запись регистров в подканал.

Микропрограмма Выполнение команды производит действия по организации связи между устройством и абонентом и передачу данных. По сигналу синхронизации, поступающему по одной 25 из линий на выход 9(на остальных линиях код Номер абонента), абонент, чей номер сформирован на входе-выходе 10, включается для дальнейшего продолжения сеанса связи. Затем на выходе 9 устанавливается код, который расшифровывается абонентом как признак необходимости сформировать ответ о

15

20

30

5

0

5

0

5

том, что он включен. В результате на входе-выходе 10 образуется номер включившегося абонента, который поступает через блок 3 на информационный вход блока 1 и записывается в регистр 30. Далее сравниваются номера включившегося и затребованного абонентов путем сравнения содержимого регистров 29 и 30. В том случае, если эти номера не совпадают, в регистре 33 формируется код ошибки Неверная адресация. На этом действия программы заканчиваются, так как продолжение сеанса связи невозможно. Выполняется переход к микропрограмме, где производятся действия по доведению этого сообщения до центрального процессора.

Если переданный номер и принятый номер абонента совпадают, то это сви- детельствует о правильном включении абонента, и на выходе 9 формируется код, который абонентом расшифровывается как сигнал о выдаче информации на вход-выход 10 о состоянии (свободен - занят) абонента. При этом на вход выборки блока 3 поступает сигт

нал, открывающий блок 3, и информация поступает на информационный вход блока 6. Одновременно на втором и четвертом выходах блока 39 блока 6 образуются коды, обеспечивающие формирование логических нулей на первом и третьем входах блока 44 элементов ИЛИ. В результате переход к следующей микрокоманде производится с учетом информации о состоянии абонента. Если абонент занят, то выполняется переход к микропрограмме Запись регистров в подканал. Если абонент свободен, то содержимое регистра 28 (код выполняемой команды) пересылается в регистр 33, открывается формирователь 35, и информация поступает на информационный вход блока 6 и далее через блок элементов И 41, блок элементов ИЛИ 44, элемент И 42 и элемент ИЛИ 45 подается без искажений на входы регистра 36, где фиксируется очередным синхроимпульсом. Таким образом производится анализ кода выполняемой команды, т.е. выбор началь- нбго адреса микропрограммы для продолжения связи с абонентом в зависимости от кода выполняемой команды.

Продолжение команды Передача управляющего байта абоненту заключается в формировании на выходе 9 кода, который расшифровывается абонентом как прием управляющего байта, а на входе-выходе 10 - непосредственно кода управляющего байта, хранящегося в регистре 25 блока 1. По сигналу синхронизации управляющий байт передается абоненту, и осуществляется переход к приему следующей команды программы.

Продолжение команды Передача данных из внешней памяти к абоненту заключается в считывании информации из внешней памяти по адресу, хранящемуся в регистре 24, и записи ее в регистр 33 блока 1, а затем в передаче на вход-выход 10 устройства. На выходе 9 формируется код, который расшифровывается абонентом как передача данных абоненту. По сигналу синхронизации данные с входа-выхода 10 за-; писываются к абоненту.

Затем содержимое регистра 24 блока 1 увеличивается на единицу (адрес данных во внешней памяти), а счетчик количества переданной информации (регистр 25) уменьшается на единицу, после чего содержимое регистра 25 про5

веряется на равенство нулю. Если это условие выполняется, то, следовательно, вся информация данной командой передана и поэтому осуществляется переход к микропрограмме Прием команды . В противном случае команда не закончена и поэтому переход осуществляется к микропрограмме Запись регистров в подканал. Такой вариант построения команды возможен в том случае, если быстродействие абонента значительно ниже, чем устройства.

Продолжение команды Передача данных от абонента во внешнюю память заключается в формировании на выходе 9 кода, которьй сообщает абоненту, что устройство готово принять информацию от него. В результате инфор0 нация от абонента ерез блок 3 поступает на информационный вход блока 1 и записывается в регистр 33 этого блока, а затем записывается во внешнюю память по адресу, хранящемуся в

5 регистре 24. Дальнейшие действия аналогичны действиям команды Передача данных из внешней памяти к абоненту1..

Микропрограмма Запись регистров в подканал обеспечивает фиксацию

Q содержимого регистров 23-26, 28 и 29 в блоке 2 в соответствующем подканале. Для формирования начального адреса подканала содержимое регистра 27 уменьшается на пять. По окончании этой микропрограммы осуществляется

переход к микропрограмме Анализ наличия задания в подканале, которая определяет наличие задания в- следующем 1 подканале, так как содержимое реги- Q стра 27 после записи всех регистров в подканал содержит начальный адрес следующего подканала.

Формула изобретения

1. Микропрограммное устройство для сопряжения процессора с абонентами, содержащее блок микропрограммного управления и блок связи с абонентами, входы установки и синхронизации и первый выход выборки блока микропрограммного управления являются соответственно входами устройства для подключения к выходам запуска и синхронизации процессора и выходом устройства для подключения управляющего входа абонента, вход выборки, первый и второй информационные входы-выходы блока связи с абонентом

13-

соединены соответственно с вторым выходом выборки, информационным входом блока микропрограммного управления и входом-выходом устройства для подключения к информационному входу- выходу абонента, отличающееся тем, что, с целью увеличения быстродействия устройства, в него введены операционный блок, блок оперативной памяти, регистр адреса и блок связи с процессором, вход прерывания, выходы прерывания и запроса блока микропрограммного управления являются соответственно выходом устройства для подключения выхода прерывания процессора и выходами устройства для подключения входов прерывания и готовности процессора, вхо условий, третий, четвертый, пятьй и шестой выходы выборки блока микропрограммного управления соединены соответственно с выходом переноса операционного блока и входами синхронизации блока связи с процессором, регистра адреса и входами выборки блока оперативной памяти и операционного блока, вход синхронизации которого является входом устройства дл

14

0

5

0

5

ратора соединены с входами синхронизации соответственно с первого по десятьй регистров, информационный выход арифметико-логического узла соединен с информационными входами с первого по десятый регистров, первый информационный вход коммутатора и выход формирователя импульса соединены с информационным входом-выходом блока, выходы с первого по восьмой регистров соединены соответственно с второго по девятый информационными входами коммутатора, выход которого соединен с первым информационным входом арифметико-логического узла, второй информационный вход и выход переноса которого соединены соответственно с выходом девятого регистра и выходом переноса блока, выход десятого регистра является адресным выходом блока.

2. Устройство по п. 1, отличающееся тем, что блок микропрограммного управления содержит первый и второй регистры, первьй и второй блоки памяти, триггер, первый и второй блоки элементов И, блок элементов ИЛИ, первьй и второй элементы

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения периферийных устройств с процессором и оперативной памятью | 1983 |

|

SU1156084A1 |

| Микропрограммный мультиплексный канал | 1985 |

|

SU1305693A2 |

| Комбинированный канал | 1986 |

|

SU1405067A1 |

| Устройство для сопряжения процессоров обмена с внешними устройствами | 1984 |

|

SU1257650A1 |

| Устройство для сопряжения оперативной памяти с внешними устройствами | 1981 |

|

SU993237A1 |

| Устройство для сопряжения электронно-вычислительной машины (ЭВМ) с внешним устройством | 1984 |

|

SU1272337A1 |

| Устройство для сопряжения электронно-вычислительной машины с внешним устройством | 1986 |

|

SU1388880A2 |

| Устройство управления | 1989 |

|

SU1654820A1 |

| Устройство для сопряжения | 1980 |

|

SU926645A2 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1280642A2 |

Изобретение относится к вычислительной технике и может быть использовано в системах обработки данных в качестве субпроцессора обмена информацией между абонентами и центральным процессором. Целью изобретения является повышение быстродействия устройства. Устройство содержит операционный блок 1, блок 2 оперативной памяти, блок 3 связи с абонентами, блок 4 связи с процессором, регистр 5 адреса, блок 6 микропрограммного управления. Устройство обеспечивает под управлением микропрограммы в блоке 6 скоростной двунаправленный обмен информацией между процессором и абонентом. 1 з.п. ф-лы, 3 ил.

подключения выхода синхронизации про- зо И и элемент ИЛИ, причем входы синхцессора, адресный выход операционного блока соединен с адресным входом блока оперативной памяти и информационным входом регистра адреса, выход которого является выходом устройства для подключения к адресному входу абонента, информационные входы-выходы операционного блока и блока оперативной памяти и первый информационный вход-выход блока связи с процессором соединены с информационным входом блока микропрограммного управления, второй информационный вход-выход блока связи с процессором является входом-выходом устройства для подключения к информационному входу-выходу процессора, причем операционный блок содержит дешифратор, коммутатор, арифметико-логический узел, формирователь импульса и с первого по десятьй регистры, причем в операционном блоке входы выборки арифметико-логического узла формирователя импульса, управляющий

вход коммутатора и первьй вход дешиф- 55 ционным входом первого регистра и

ратора соединены с входом выборки блока, второй вход дешифратора соединен с входом синхронизации блока, с первого по десятьй выходы дешифвторым входом первого элемента И, ход которого соединен с первым вхо дом элемента ИЛИ, второй вход и вы ход которого соединены соответстве

5

0

5

0

ронизации первого и второго регистров являются входом синхронизации блока, нулевой вход первого регистра является входом установки блока, единичный и нулевой входы и выход триггера соединены соответственно с входом прерывания блока, первым выходом второго регистра и входом первого блока памяти, выход которого соединен с первым входом первого блока элементов И, второй вход и выход которого соединены соответственно с первым выходом второго блока памяти и первым входом блока элементов ИЛИ, с второго по шестой выходы второго блока памяти соединены соответственно с информационным входом второго регистра, первыми входами первого и второго элементов И и второго блока элементов И и вторым входом блока элементов ИЛИ, третий вход и первый и второй выходы которого соединены соответственно с выходом второго блока элементов И, первым информационным входом первого регистра и

вторым входом первого элемента И, выход которого соединен с первым входом элемента ИЛИ, второй вход и выход которого соединены соответственно

с выходом второго элемента И и вторым информационным входом и входом услоинформационным входом первого регистра, выход которого подключен к входу второго блока памяти, вторые входы второго блока элементов И и второго элемента И являются соответственно

23

2Ь

25

сн

- -

-&

26

12

: 27

28

вий блока, с второго по девятый выходы второго регистра являются соответственно выходами запроса, прерывания и с первого по шестой выходами выборки блока.

1

Кбходу 21блокоВ

32

33

31

ЗЬ

Фиг. 2

| Устройство для сопряжения источников и приемников с магистралью | 1984 |

|

SU1252788A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР № 1114099, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-01-30—Публикация

1987-12-15—Подача