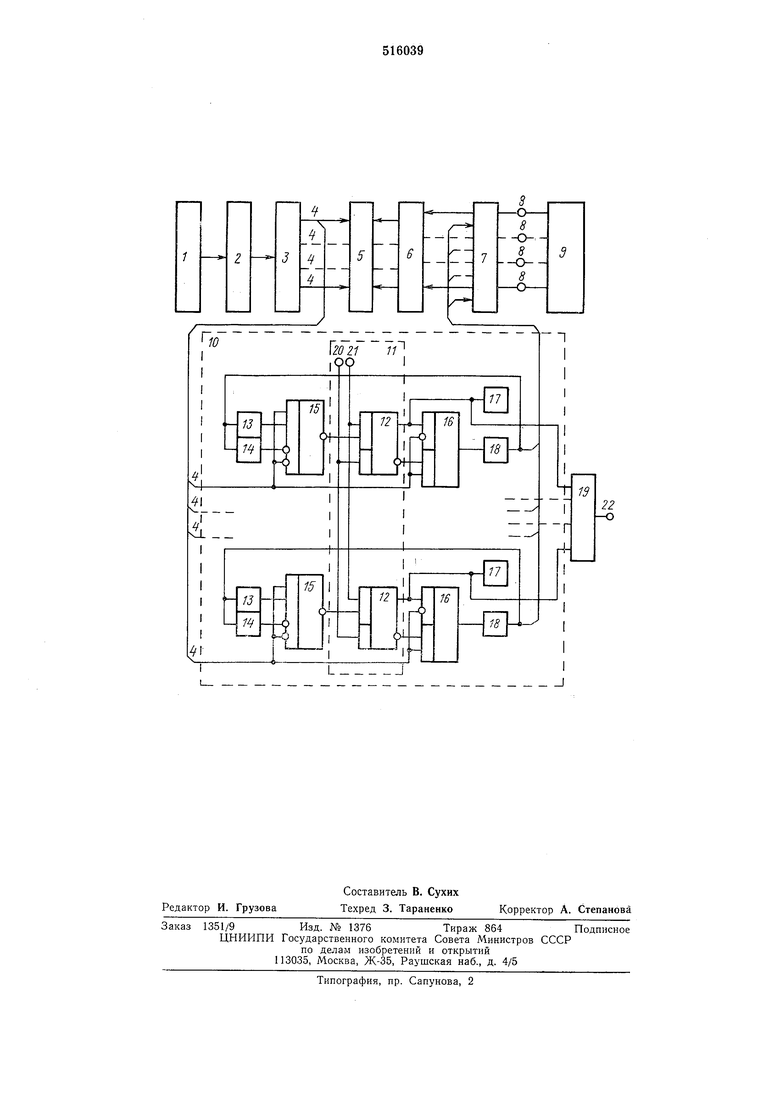

узла 9, каналы 10 контроля, регистр 11 защиты с элементами 12 памяти, входящие в состав каналов контроля пороговые элементы 13 с высоким порогом срабатывания, пороговые элементы 14 с низким порогом срабатывания, элементы 15 сравнения, элементы «И - ИЛИ 16 и блоки 17 индикации, а также формирователи 18 выходных сигналов и элемент «ИЛИ 19. Кроме того, на чертеже указаны: день 20 обнуления регистра защиты, цепь 21 стробирующего сигнала записи в регистр защиты, вход 22 элемента «ИЛИ. Устройство работает следующим образом. Тестовая информация из запоминающего блока 1 через блок 2 записи поступает в празрядный регистр 3 тестов, информация с выходов 4 регистра - в блок 5 сравнения. Кроме того, каждый выход регистра тестов подсоединен через элемент «И - ИЛИ 16 и формирователь 18 выходных сигналов к блоку 7 коммутации. Блок коммутации подключает выходы формирователей 18 к входным контактам 8 контролируемого узла 9 и к входам формирователей 6 входных сипналов, а выходные контакты проверяемого узла 9 - только к входам формирователей 6 входных сигналов. В случае отсутствия перегрузки формирователей 18 выходных сигналов элементы 12 памяти (триггеры) регистра И защиты установлены в «О и их инверсные выходы дают разрещение на прохождение сигнала разряда регистра тестов через нижние вентили элементов «И - ИЛИ 16 на входы формирователей 18. Когда на выходах разряда регистра тестовый сигнал «1 («О), на выходах формирователей 18 и на выходах пороговых элементов 13 (14) сигнал «1 («О). Элементы 15 в этом случае сравнивают регистровые и выходные сигналы, на их выходах появляются сигналы «О, которые, поступая на входы схем совпадения триггеров, запрещают запись «1 в триггеры по стробирующему сигналу. Если возникла перегрузка какогонибудь формирователя 18 выходных сигналов, вырабатывающего сигнал «1 («О) из-за коммутации его с источником «нулевого («единичного) сигналов или с выходом другого формирователя, вырабатывающего сигнал «О («1), а также с добавочной нагрузкой, то для устранения иерегрузки достаточно изменить сигнал на выходе формирователя 18 на противоположный. Перегрузка формирователя 18 приведет либо к тому, что уровень сигнала на его выходе не сталет соответствовать единичному (нулево,му) сигналу при единичном (нулевом) сигнале соответствующего разряда регистра тестов, либо к тому, что появится дополнительная задержка времени переключения формирователя. В первом случае элементы 13 и 14 не срабатывают, что вызывает «несравнение сигнала после формирователя 18 выходных сигналов с сигналом соответствующего разряда регистра тестов. Элемент 15 сравнения вырабатывает сигнал «1. При задержке переключения какого-либо формирователя 18 из «О в «1 (из «1 в «О) пороговый элемент 13 с высоким порогом (низким порогом 14) срабатываиия выдает на элемент 15 сравнения сигнал «1 («О) с запаздыванием. На время запаздывания на выходе элемента 15 оказывается сигнал «Ь. В обоих случаях при совпадении единичного сигиала с выхода элемента сравнения и стробирующего сигнала проводится запись «1 в регистр того разряда регистра 11 защиты, формирователь 18 которого подвергся перегрузке. Стробирующий сигнал приходит с задержкой относительно начала выдачи каждого теста, учитывающей задержки прохождения сигнала по цепи: разряд регистра тестов, элемент «И - ИЛИ 16, нормально нагруженный формирователь 18 выходных сигналов, пороговый элемент 13 (пороговый элемент 14) и элемент 15 сравнения. Если триггер переброщен в состояние «1, то цулевой потенциал его инверсного выхода запрещает прохождение прямого сигнала разряда регистра тестов через нижний вентиль элемента «И - ИЛИ, а единичный потенциал прямого выхода триггера разрещает прохождение инвертированного сигнала разряда регистра тестов через верхний вентиль этого элемента. Таким образом, выходной сигнал формирователя 18 изменяется на противоположный, что устраняет перегрузку последнего. Блоки 17 индикации, подключенные к выходам регистра 11 защиты, позволяют определить пеисправные внещние каналы устройства, а элемент «ИЛИ 19 вырабатывает сигнал, запрещающий дальнейший тестовый контроль. Формула изобретения Многоканальное устройство для тестового контроля, содержащее формирователи выходных сигналов, подключенные через блок коммутации к контролируемым узлам, и последовательно соединенные запоминающий блок, блок записи, регистр тестов и блок сравнения, связанный через формирователи входных сигналов с выходами блока коммутации, отличающееся тем, что, с целью повыщеиия достоверности контроля и надежности работы устройства, в него введены регистр защиты формирователей выходных сигналов, элемент «ИЛИ и каналы контроля, состоящие из пороговых элементов, элементов сравнения и «И - ИЛИ и блоков индикации, причем в аждом канале контроля выходы пороговых лементов, входы которых связаны с выходаи соответствующего формирователя выходных сигналов, подключены через элемент равнения к входу регистра защиты формиователей выходных сигналов, выходы котоого подключены к входам элемента «ИЛИ и входам блоков индикации и через элемены «И - ИЛИ к входам формирователей ыходных сигналов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля и диагностики цифровых блоков | 1985 |

|

SU1278855A1 |

| Устройство для контроля логических схем | 1986 |

|

SU1381517A1 |

| Устройство для контроля цифровых узлов | 1981 |

|

SU1013960A1 |

| Устройство для контроля дискретной аппаратуры с блочной структурой | 1987 |

|

SU1539783A1 |

| Многоканальное устройство тестового контроля логических узлов | 1988 |

|

SU1564623A1 |

| Устройство для контроля цифровых объектов | 1988 |

|

SU1691841A1 |

| Многоканальное устройство тестового контроля логических узлов | 1985 |

|

SU1265778A1 |

| СПОСОБ ФОРМИРОВАНИЯ СИГНАЛА ИЗОБРАЖЕНИЯ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1987 |

|

RU1612956C |

| Устройство тестового контроля цифровых блоков | 1985 |

|

SU1315982A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ И ВОССТАНОВЛЕНИЯ ТЕХНИЧЕСКИХ СРЕДСТВ МЕДИЦИНСКОГО НАЗНАЧЕНИЯ | 1992 |

|

RU2072788C1 |

Авторы

Даты

1976-05-30—Публикация

1974-10-24—Подача