го шифратора, выходы которого подключены к входам первой группы входов ассоциативного накопителя, входы второй группы входов которого соединены с выходами формирователя номера исправной ячейки памяти, а входы третьей группы входов - с выходами адресного блока, входы сумматоров по модулю два первой группы и одни из входов второго коммутатора подключены к выходам элементов ИЛИ, выходы ассоциативного накопителя соединены с другими входами первого и второго коммутаторов, выходы сумматоров по модулю два первой группы и выходы второго коммутатора подключены к входам блока записи информации, входы блоков свертки соединены с выходами элементов И четвертой группы, а выходы - с другими входами регистров второй группы выходы блока обнаружения некорректируемых ошибок являются выходами отказов устройства.

2. Устройство ПОП.1, отличающееся тем, что блок контроля и коррекции содержит группы сумматоров по модулю два и шестую группу элементов И, причем входы сумматоров по модулю два второй группы являются входами блока, входы сумматоров по модулю два третьей

группы и первые входы сумматоров по модулю два четвертой группы подключены к одноименным . (входам сумматоров по модулю два второй группы выход каждого из которых соединен с первкЕми входами соответствукмцих элементов И шестой группы, выход каждого сумматора по модулю два тре тьей группы подключен к второму входу соответствующего элемента И шестой группы, выходы элементов И. шестой группы соединены с вторыми i входами сумматоров по модулю два .четвертой группы, выходы которых и выходы сумматоров по модулю два второй, группы являются выходами блока.

3. Устройство Ш)пп.1и2, отличающееся тем, что блок обнаружения некорректируемых оиибок содержит первый элемент ИЛИ, элемент |1есовпадения, элемент НЕ и элемент И, выход которого является |В лходом блока, а входы подключены ; соответственно к выходу второго элемента ИЛИ и к выходу элемента НЕ, вход которого соединен с выходом элемента несовпадения, входы которого и входы второго элемента ИЛИ соответственно объединены и являются входами блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ДИНАМИЧЕСКИМ РЕЗЕРВИРОВАНИЕМ | 1990 |

|

RU2028677C1 |

| Запоминающее устройство с коррекцией групповых ошибок | 1983 |

|

SU1141453A1 |

| Устройство для коррекции ошибок | 1987 |

|

SU1541677A1 |

| Запоминающее устройство с автономным контролем | 1984 |

|

SU1161994A1 |

| Запоминающее устройство с самоконтролем | 1986 |

|

SU1374284A1 |

| Запоминающее устройство с исправлением ошибок | 1989 |

|

SU1667156A1 |

| Запоминающее устройство с исправлением ошибок | 1981 |

|

SU982098A1 |

| Запоминающее устройство с коррекцией групповых ошибок | 1983 |

|

SU1092570A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1805503A1 |

1. ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С БЛОКИРОВКОЙ НЕИСПРАВНЫХ ЯЧЕЕК ПАМЯТИ, содержащее адресный накопитель, выходы которого подключены к входам усилителей, а входы соответственно к выходам адресного блока и выходам блока записи информации группы регистров, формирователи сигналов, блок.управления, первый регистр, элемент ИЛИ и группы элементов И, причем выходы усилителей подключены к первым входам элементов И первой группы выходы которых соеди.нены с входами регистров первой груп, пы, а вторые входы подключены к стробкрукидему выходу блока управления, установочный, адресный и считывающий. выходы которого соединены с входами , адресногр блока, а выход разрешения считывания подключен и первым входам элементов И второй группы/ первые входы элементов И третьей группы соединены с одними из выходов первого регистра, вход которого подключен к выходу первого формирователя сигналов, первые входы элементов И четвертой группы соединены с выходом разрешения записи блока управления, вьбсод запрета которого подключен к управл}пощему входу блока записи информёщии, вторым входам элементов ,И третьей группы и первым входам элементов И пятой группы, вторые ходы которых соединены с другими выходами первого регистра, а третьи ВХОДЫ - с выходами регистров второй группы, одни из входов которых прд- , ключены к выходам элементов И четвертой группы, первый и вторые входов элементов ИЛИ соединены соответственно с выходами элементов И третьей группы и выходами элементов И пятой группы, выходы регистров третьей группы подключены соответственно к входу первого формирователя сигналов и входу второго формирователя сигнсшов, выход которого соединен с вторыми входами элементов И второй группы, выходы которых и вторые входы элементов И четвертой группы являются соответственно ин- -, формационными выходами, и входами у Л- @ ройства, отличающееся (Л тем, что, с целью повышения надежности устройства, в него введены с: блоки свертки,блок контроля и коррекции, коммутаторы, второй и третий i регистры, первый шифратор, первая группа сумматоров по модулю два, формирователь номера исправной ячейки памяти, ассоциативный накопитель и блок обнаружения некоррек-п тируемых ошибок, причем входы и одни из выходов блока контроля и коррекции подключены соответственно к выходам регистров первой группы и : :. одним из входов первого коммутатора, выходы которого соединены с третьими входами элементов. И второй и третьей групп, входы второго регистра подключены к выходам элементов И первой группы, а выходы - к одним из входов формирователя номера исправной ячейки памяти, другие входы которого соединены с выходами первого формирователя сигналов, другие выходы блока контроля и коррекции подключены к входам третьего регистра, выходы которого соединены с входами блока обнаружения некорректируемых ошибок и входс1ми перво

Изобретение относился к вычислительной технике и может найти нение для построения высоконадежной памяти в многопроцессорных системах. Известно запоминающее.устройство с блокировкой неисправных ячеек памяти, которое содержит накопитель, .включающий основное и дополнительное поля элементов памяти, первый регист адреса, дешифратор адреса, регистр числа, второй регистр адреса, дополнительный регистр, схему сравнения, счетчик и блок управления 1. Недостатком этого устройства является его сложаость. Наиболее близким техническим решением к изобретению является оперативное за.поминакхцее устройство с блокировкой неисправных ячеек памяти , содержащее накопитель, блок усилителей считывания, элементы И, регистры чисел, шины выдачи яисел, бло записи-регенерации, адресный блок, блок управления, дополнительный регистр маски, дополнительные элементы И, дополнительные регистры чисел элементы ИЛИ, блок формирования маски в режиме записи, блок формиро- вания маски в режиме считывания, блок регистров, шину начальной установки, обеспечивающую выдачу сигнала установки в исходное состояние, шину адреса для выдачи сигнала приема адресов, шину считывания, обеспечивающую выдачу сигнала считывания,- шчну стробирования, шину запрета, шину переда чи для выдачи управляющего сигнала, шину числа, шины приема чисел из арифметического устройства, причал входы накопителя подключены к блоку записи-регенерации и адресному блоку, а выход - к блоку усилителей считывания, входы регистров чисел соединены через элементы И с выходами блока усилителей считывания, выходы блока регистров подключены к входам блоков формирования масок, входы дополнитель «ого регистра маски и регистров чисел подключены соответственно к выходам одних дополнительных элементов И и выходам одного из блоков формирования масок, а выходы через последовательно соединенные другие дополнительные элементы И и элементы ИЛИ подключены к входам блока записирегенерации I. 2 J.

i Недостатком известного устройства является низкая надежность, так как оно не способно.восстанавливать свою работоспособность при отказах его элементов.

Цель изобретения - повышение надежности устройства.

Поставленная цель достигается тем, что в оперативное запоминающее устройство с. блокировкой неисправшзих ячеек памяти, содержащее адресный накопитель, вшсоды которог подключены к входам усилителей, а входы - соответственно к выходам адресного блока и выходам блока записи информации, группы регистров, фомирователи сигналов, блок управления, первый регистр, элементы ИЛИ и группы элементов И, причем выходы усилителей подключены к первым вхог дам элементов И первой группы, выходы которых соединены с входами регистров первой группы, а вторые, входы подключены к стробирующему выхода блока управления, установочный, адресный и считывающий выходы которого соединены с входами адресного блока, а выход разрецения считывания подключен к Первым входам элементов И второй группы, первые входы элементов И.третьей группы соединены с однигш из выходов первого регистра, вход которого подключе к выходу первого формирователя сигналов, первые входы элементов И четвертой группы соединены с выходо разрешения записи блока управления, выход запрета которого подключен к управляющему входу блока записи информации, вторым входам элементов И третьей группы и первым входам элементов И пятой группы, вторые входы которых соединены с другими выходами первого регистра, а третьи входы - с выходами регистров второй группы, одни из входов которых покключены к выходгш элементов И четвертой группы, первые и вторые входы элементов ИЛИ соединены соответственно с выходами элементов И третьей группы и выходами элементов И пятой группы, выходы регистров третьей группы подключены соответственно к входу первого фО 1ироваГеля сигналов и входу второго формирователя сигналов, выход которого соединен с вторыми входами элементов И второй группы, которых и BTOiXiie входы элементов И четвертой группы являются соответственно информационными выходами и входами устройства, введены блоки свертки, блок контроля и коррекции, коммутаторы, второй и третий регистры, первый шифратйр, первая группа сукматоров по модулю два, формирователь номера исправной ячейки памяти, ассоциативный нг копитель и блок обнаружения некорректирующих ошибок, причем входы и одни из выходов блока контроля, и коррекции подключены соответственно к выходам регистров первой группы и-одним из входов первого коммутатора, выходы которого соединены с третьими входами элементов И

0 И второй и третьей групп, входы второго регистра подключены к выходам элементов И первой группы, а выходы - к одним из входов формирователя номера исправной ячейки памяти,

5 другие входы которого соединены с выходами первого формирователя сигналов, другие выходы блока контроля и коррекции подключены к входгил третьего регистра, выходы которого соединены с входами блока обнаруOжения -некорректируемых ошибок и входами, первого шифратора, выходы кото-, рого подключены к входам первой группы входов ассоциативного накопителя,, входы второй группы входов которого

5 соединены с выходами формирователя номера исправной ячейки памяти, а входы третьей группы входов - с выходами адре.сного блока, входы сумматоров по модулю два первой группы

0 и одни из входов второго коммутатора подключены к выходам элементов ИЛИ,; выходы ассоциативного накопителя соединены с другими входами первого и второго коммутаторов,- выходы сум5маторов по модулю два первой группы и выходы второго коммутатора подкйючены к входам блока записи информа-i ции, входы блоков свертки соединенвэс выходами элементов И четвёртой группы, а выходы - с другими входами ;.

0 регистров второй группы/ В1 хода1 вло4 ка обнаружения некорректируемых ошибок являются выходами отказов устройства. .. ; . Кроме того, блок контроля и коррек5ции содержит группы сумматоров по ; модулю два и шестую группу элементов И, лричем входы сумматоров по модулю два второй группы являются входами блока, входы Сумматоров по модулю

0 ,два третьей группы и первые входы сумматоров по модулю два четвертой группы подключены к одноимённым входам сумматоров по модулю два второй группы, выход каждого из которых сое5динен с первыми входами соответствующих элементов И шестой группы, выг ход каждой из сумматоров по модулю . два третьей группы подключен к второ-му входу соответствуквдего элемента

0 И шестой группы, выходы элементов И шестой группы сбединены с з-ЕОрами входами сумматоров по модулю два четвертой .группы, выходы которых и Выходы сумматоров по модулю два второй группы яв 1яются выходами блока.

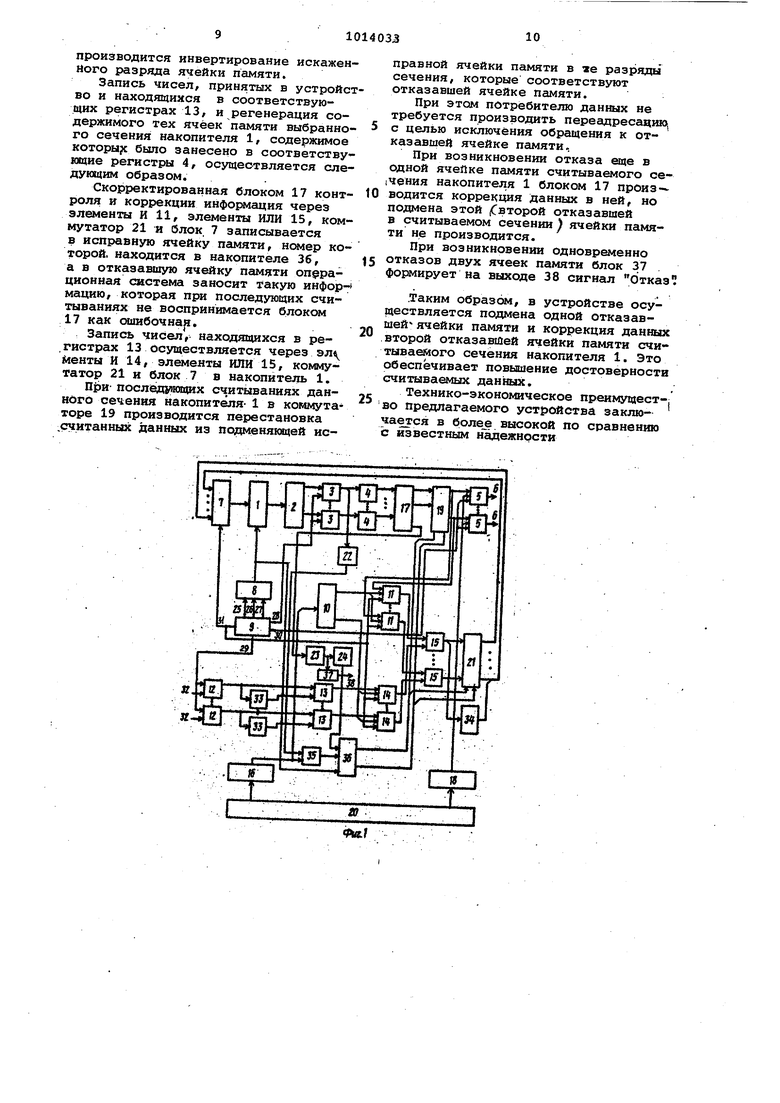

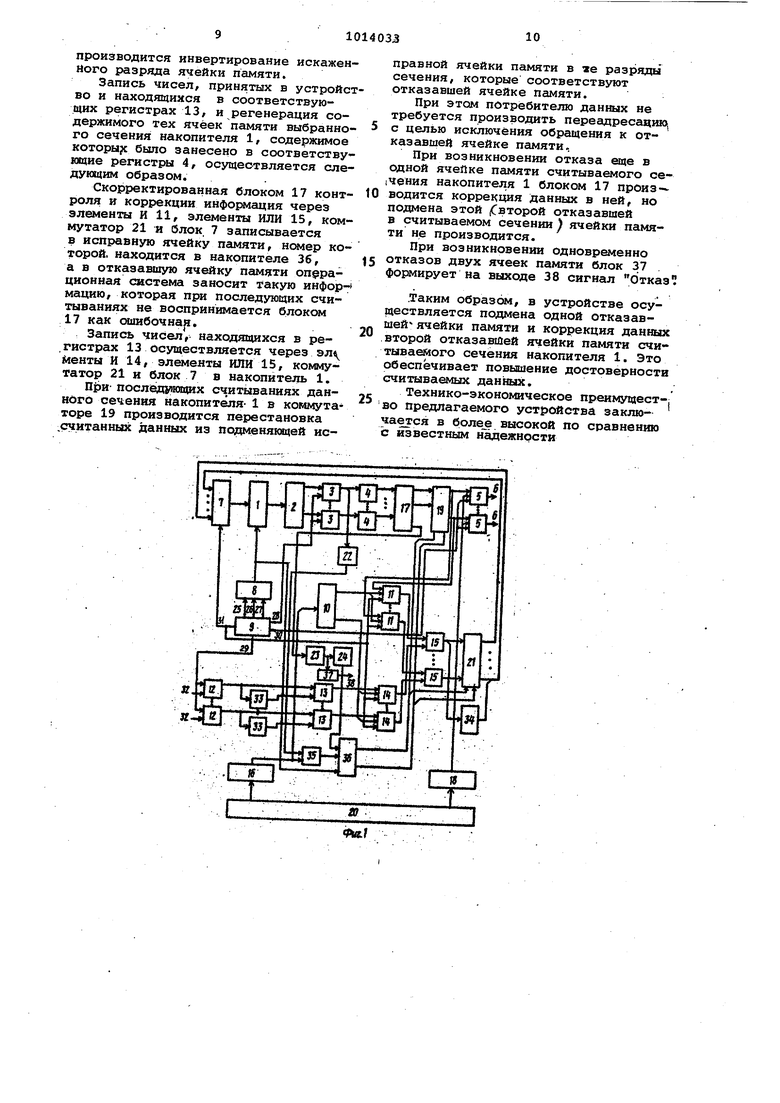

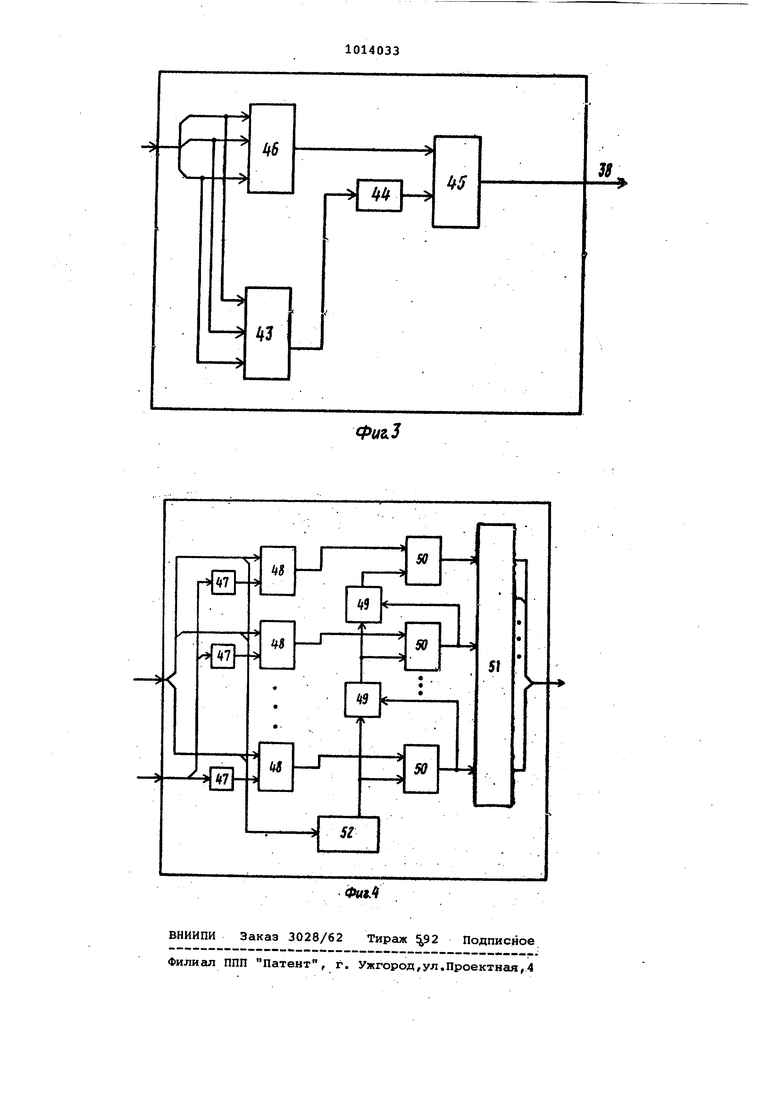

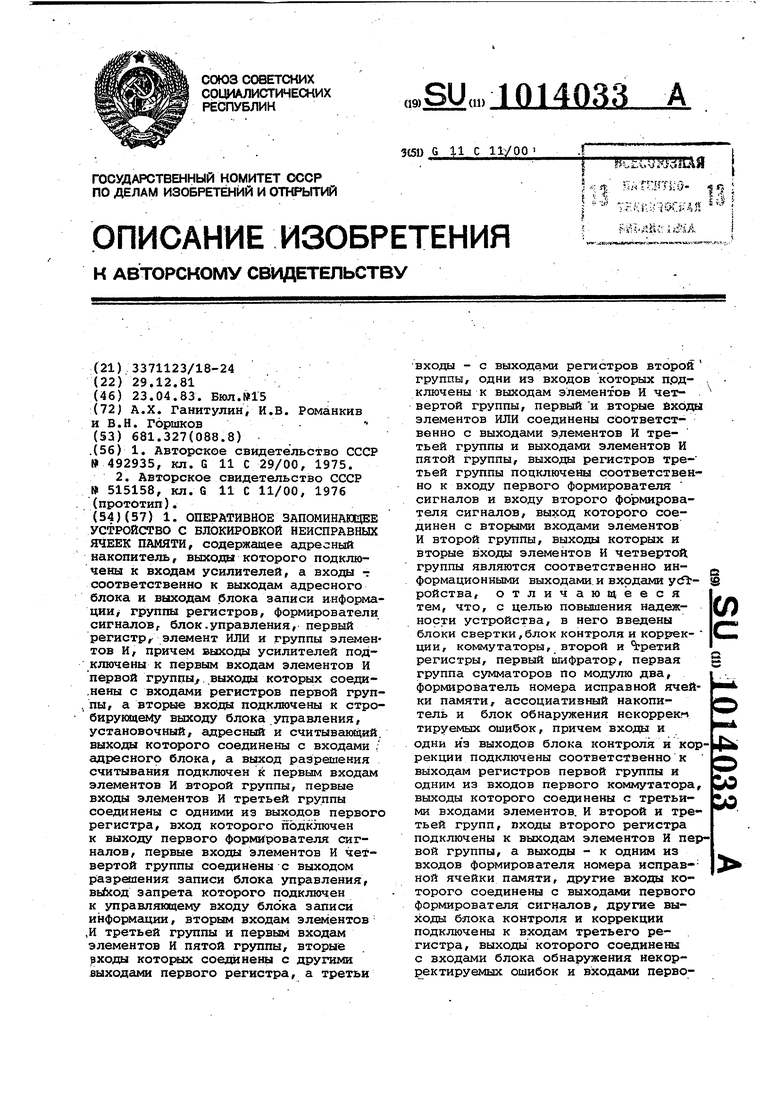

5 При этом блок обнаружения некорректируемых ошибок содержит второй элемент ИЛИ, элемент несовпадения, элемент НЕ и элемент И, выход которого является выходом блока, а вход подключены соответственно к выходу второго элемента ИЛИ и выходу .элемента НЕ, вход которого соединен с.выходом элемента несовпадения, вх ды которого и входы второго эле мента ИЛИ соответственно объединены и являются входами блока. Ка фиг.1 .представлена функционал схема предлагаемого устройства; на фиг.2 - функциональная схема бло ка контроля и коррекции; на фиг.З схема блока обнаружения некорректиру-емых ошибок; на фиг.4 - схема фор мирователя номера исправной ячейки памяти. Устройство содержит (фиг.1 адре вый накопитель 1, усилители 2, первую группу элементов И 3, первую группу регистров 4, вторую группу элементов И 5 с выходами б, блок 7 записи информации,,адресный блок В, обеспечивающий выбор сечения накопителя,.к которому производится обращение/ блок 9 управления, первый регистр 10, третью 11 и четверт 12 группы элементов И, вторую згрупп регистров 13, пятую группу элементов И 14, группу элементов ИЛИ 15, первый формирователь 16 сигналов, . блок 17 контроля и коррекции, второй формирователь 18 сигналов, первый коммуташор 19, третью группу регистров 20, второй коммутатор 2.1, .второй 22 и 23 регистры, , первый шифратор 24, Нафиг. 1 обознач,ены установочный 25, адресный.26 и считывающий 27 выходы, СТрОбКрУКНЦИЙ выход 28, BXJход 29 запрета, выход 30 разрешения считывания и выкод 31 разрешения записи блока управления, информацио .:ные входы 32 устрой JTBa. Устройство содержит также фик, ) блоки 33 свертки, сумматоры 34 по модулю два, формирователь 35 номера исправ ,ной ячейки памяти, ассоциативный накопитель 36 и блок 37 обнаружения некорректируемых -ошибок с выходом 38. Блок 17 контроля и коррекции содержит (фиг.2) первую 39 и вторую 40 группы cyNMaTopOB по модулю два шестую группу элементов И 41 и тре,тью группу сумматоров.42 по модулю два. Блок 37 обнаружения некорректиру мых ошибок содержит (.фиг, 3, элемент 43 несовпадения, элемент НЕ 44, элемент И 45 и первый элемент ИЛИ 4 Формирователь номера исправной ячейки памяти содержит фиг.4У груп элементов НЕ 47, седьмую 48 и восьмую 49 группы элементов И, группу элементов И-НЕ 50, второй шифратор 51 и второй элемент ИЛИ 52. В каждом сечении накопителя 1 содержится VI йчеек пагу1яти, причем ячейки с номерами 1-(и-1}используются для хранения данных, а ячейка памяти с номером и используется для хранения контрольного кода сечения, каждеай разряд которого является сумной по модулю два одноименных разрядов , ячеек памяти с номерами от 1 до(иги, где и 1 - целое число. В каждой ячейке памяти сеченкя разряды с номерами от 1 до ( ) используются для хранения данных, разряд с номером ( I -1) предназначен для хранения признака занятости, принимающего значение равное 1, если в этой ячейке записана информация ,, и О - в противном случае. Разряд с номером Т используется для хранения контрольного разряда, представляющего собой сумму по модулю два всех разрядов ячейки с номерами ©т 1- до (Г -1) , Устройство работает следукадим образом. . При поступлении в блок 9 сигнала Обращение обеспечивается следующая последовательность работы блокой устройства. По сигналу с выхода 25 блока 8 осуществляется гашение предшествующей информации в регистрах 4,10,13, 20, 22 и 23 и в блоке 8. По сигналу с выхода 26 блока 9 . в блок 8 производится прием адреса сечения накопителя 1, в регистры 20 - прием кодов маски для считывания и записи. При появлении сигнала на выходе 27 блока 9 сигнала блоком 8 выполня-г ется считывание содержимого всех ячеек соответствукнцего сечения накопителя 1. К этому моменту времени оказывается сформированными с помо-. щью формирователей 16 и 18 маски для записи и считывания, соответст- ; венно. Разряды маски в режиме записи формируются формирова -елем 16 так, что в j-и frдe )триггер регистра 10 заносится единица, если в j-ю ячейку памяти выбранного сечения накопителя 1 надлежит записать число, поступающее по входам , 32 в j-и регистр 13, Соответствующий триггер регистра 10 остается в нулевом состоянии, если в j -ю ячейку памяти выбранного сеч.ения накопителя 1 надлежит записать информацию с j -го регистра 4, т.е. регенерировать считанную ранее информацию. Разряды маски в режиме записи казываются записанными в соответстующие триггеры регистра 10, котоые содержат единичные разряды маеки и подготавливают к работе соответствующие элементы И 14. Одновременно со считыванием информации из накопителя 1 сигналом, снимаемые с выхода 31 блока 9, разрешается прием в регистры 13 Множества чисел подлежащих записи в накопитель.1 с одновременной сверткой их на блоках 33 и занесением полученных контрольных кодов в соответствующие разряды регистров 13. При появлении на выходе 29 сигна ла запрета производится передача данных через элементы ИЛИ 15 на коммутатор 21. Причем на коммутатор 21 из накопителя 36 поступает нулевой код. Каждый разряд записываемых данных проходит на выход коммутатора 21, а затем в блок 7. Из блока 7 производится запись данных в накопитель 1. Одновременно сумматоры 34 формируют контрольный код сечени который также записывается, через блок 7 в накопитель 1 в ячейку памя ти с номером У1 . Выдача считанных из накопителя 1 чисел производится через элементы И 5 по управляющему сигналу, формируемому на выходе 30 блока 9 одновременно с сигналом запрета. Подготовка к работе соответствующих .элементов И 5 осуществляется с помо щью выходных сигналов формирователя 18 в режиме считывания. При возникновении одиночной ошиб ки при считывании данных из ячейки памяти выбранного сечения накопите.ля 1 она обнаруживается блоком 17 . ..и фиксиру:ется в соответствующем разряде регистра 23. Обнаружение . ошибки производителя с помощью сумма торов 39 (фиг.2)гВ блоке 37 проверяется кратность возникшей ошибки. ;поскорьку возник одиночный отказ, .из регистра 23 на входы элементов ИЛИ 46 (фиг. элемента 43 несовпа дения поступает код, содержащий все го одну 1. На выходе этих элементов появляются единичные сигналы. Единичный СИГНАЛ с выхода элемента 43 несовпадения поступает через эле мент НЕ .44 на второй вход элемента И 45 и закрывает его. Сигнал о наличии некорректируемой ошибки на вы ход 38 не вьадается. Далее шифратор 24 формирует номер отказавшей ячей ки памяти, который поступает в нако тель 36 и запоминается в нем. Кроме того, номер отказавшей ячейки памяти разрешает запись в накопитель 36 адреса выбранного сечения, который ноступает из блока 8. К .этому времени формирователем 35 формируется номер исправной ячейки памяти, кото рая может использоваться для подме;ны отказавшей ячейки памяти в этом сечении накопителя 1. Этот номер .записывается в накопитель 36. Номер исправной ячейки памяти для подменврформируется на основании информации, поступающей из регистра 22 и формирователя 16 в режиме записи. ; Формирование номера исправной ячё{( ки памяти происходит следующим обраЗОМ. i: По -ому.входу первой группы входов формирователя 35 поступает оданочный сигнал/ если J -я ячейка выбранного сечения свободна, а по j -му ;. входу второй группы входов поступает единичный сигнал с формирователя 1б, если в j-ю ячейку надлежит.за- писать новые данные, поступакндие i . по входам 32. В этом случае j-ю ячейку памяти для подмены отказавшей использовать нельзя, это обесЯечива- ется подачей на j-Й элемент И 48 (фиг. 4) нулевого сигнала с выхода элемента НЕ 47. Если в J -.ю ячейку памяти нет записи новых данных, ; { в этом случае единичный сигнал с выт хода элемента И 48 поступает на иервый вход j-ro элемента И-НЕ 50, На- : личие на двух входах элементов И-НЕ :50 единичных сигналов приводит к по явлению нулевых сигналов на их выходах и блокировке элементов И 49, притчам подача нулевого сигнала на один вход одного из элементов И-НЕ 50 вызывает блокировку других элементов И-НЕ 50, имекядих больщий порядковый нЬмер (на фиг.4 порядковые номера элемен- тов И-НЕ 50 возрастают снизу вверх). Таким образом элемент И-НЕ 50 . с меньшим порядковым номером забло-. кируетс все остальные элементы И-НЕ г50, находящиеся выше его,Одновременно нулевой сигнал с выхода этого элемента И-НЕ 50 поступает на шифратор 51 с выхода которого номер исправной ячейки памяти, выделяемой для подмены, поступает на выходы формирователя 35.: Вьщача считанных из накопи еля 1 чисел после коррекции в блоке 17 производится через коммутатор 19 и соответствующие элементы И 5, Причем коррекция ошибки в блоке 17 производится следующим образом, С помощью сумматоров 39 определяется. ячейка памяти, в которой возник отказ. На выходе соответствующего сумматора 39 при этом будет код 1, . Отказавший разряд ячейки памяти находится с помощью сумматоров 40, на выходе одного из которых будет ксщ 1. Сигналы с выходов сумматоров 39 и 40 поступают на входы элементов И 41. При этом на входы одного из элементов И 41; соответствующе- го.отказавшему разряду ячейки памяти, поступают две 1, На выходе этого элемента И 41 появляется код 1, который поступает на соответствуняций сулматор 42 и за счет этого

производится инвертирование искаженного разряда ячейки памяти.

Запись чисел, принятых в устройство и находящихся в соответствующих регистрах 13, и регенерация содержимого тех ячеек памяти выбранного сечения накопителя 1, содержимое которырс было занесено в соответствующие регистры 4, осуществляется следующим образом.

Скорректированная блоком 17 контроля и коррекции информация через элементы И 11, элементы ИЛИ 15, коммутатор 21 и блок. 7 записывается в исправную ячейку памяти, номер которой, находится в накопителе 36, а в отказавшую ячейку памяти оп рационная система заносит такую информацию/ которая при последующих считываниях не воспринимается блоком 17 как (шгабочная.

Запись чисел, находягцихся в регистрах 13 осуществляется через эл Менты И 14, элементы ИЛИ 15, коммутатор 21 и блок 7 в накопитель 1.

при- послёдушщах считываниях данного сечения накопителя- 1 в коммутаторе 19 производится перестановка считанных данных из подменяющей исправной ячейки памяти в ге разряды сечения, которые соответствуют отказавшей ячейке памяти.

При этом потребителю данных не требуется производить переадресацию с целью исключения обращения к отказавшей ячейке памяти.

При возникновении отказа еще в одной ячейке памяти считываемого се|Чения накопителя 1 блоком 17 произ- водится коррекция данных в ней, но подмена этой (Свторой отказавшей в считываемом сечении) ячейки памяти не производится.

При возникновении одновременно отказов двух ячеек памяти блок 37 формирует на выходе 38 сигнал Отказ

.Таким образом, в устройстве осуществляется подмена одной отказавшейячейки памяти и коррекция данных второй отказавшей ячейки памяти считываемого сечения накопителя 1. Это обеспечивает повышение достоверности считываемых данных.

Технико-экономическое преимущество предлагаемого устройства заключается в более высокой по сравнению с известным надежности

Фиг. 2

6

38

«

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Оперативное запоминающее устройство с блокировкой неисправных ячеек | 1973 |

|

SU492935A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Оперативное запоминающее устройство с обращением к множеству ячеек памяти | 1974 |

|

SU515158A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1983-04-23—Публикация

1981-12-29—Подача