Изобретение относится к цифровой электроизмерительной технике и может быть применено в цифровых измерительных приборах, устройствах автоматики и вычислительной техники.

Известен преобразователь напряжения в код с системой сгъмоконтроля и автокоррекцией нуля, содержгиций нульорган, блок управления, преобразователь код-напряжение, регистр, KJnoчи, триггеры, элементы И, ИЛИ, НЕ. Устройство позволяет, переключая блоком управления входы нуль-органа и анализируя сигнал на выходе нуль-органа за К дополнительных тактов, произвести коррекцию полученного кода Ul.

Однако аналого-цифровой преобразовате ь имеет низкое быстродействие из-за того, что каждый цикл преобразования заканчивается коррекцией пЪлученного кода, требующей. К дополнительных тактов.

Известен также аналого-цифровой преобразователь, содержащий блок управления, счетчик, триггер интервала, селектор, триггер памяти, элементы совпадения, триггер коррекции, сравнивакицйй блок, инверторы, к.лючи, источник дополнительных образцовых г

напряжений, реверсивный счетчик коррекции, цифроаналогобый преобразователь коррекции

Недостаток устройства заключается в том, что при работе аналого-цифрового преобразователя напряжение, смещения нуля суьмируется с напряжением поразрядного уравновешивания и возникает несоответствие между кодом и

0 напряжением поразрядного уравновешивания. Схема коррекции охватывает только сравнивающий блок и не позволяет учесть напряжение смещения нуля цифроаналогового преобразователя, 5 что приводит к снижению точности преобразования напряжения в код.

Цель изобретения - повышение точности преобразования напряжения в код.

0

Поставленная цель достигается тем, что в аналого-цифровой преобразователь с автоматической коррекцией нуля, содержащий блок коррекции, вк.пючающий первый элемент И, первый эле5мент НЕ, первый и второй ключи, выходы которых объединены, а первые входы соединены соответственно с общей шиной и с шиной Вход, при этом вторые входам соединены соответ0ственно с единичным выходом триггера

коррекции и с выходом второго элемента НЕ, вход которого соединен с единичным выходом триггера коррекции и с первым входом второго элемента И, выход которого соединен с первым входом реверсивного счетчика, кроме того, первый вход блока сравнения цифроаналоговый преобразователь соединен с первыми выходами блока управления, первый вход которого соединен с первым входом счетчика, введены i блок регулирующих резисторов, аналоговый мультиплексор, первый и второй элементы ИЛИ, блок установки кода нуля, генератор тактовых импульсов, третий, четвертый и пятый элементы И и аналоговый запоминающий блок, причем первый вход его соединен с выходом первого ключа, второй с выходом первого элемента ИЛИ, третий с выходом аналогового мультиплексора, первый выход соединен со вторым входом блока сравнения, а второй выход через блок регулирующих резисторов соединен с первыми входами аналогового мультиплексора, BTOjMe входы которого соединены с выходами реверсивного счетчика, второй вход которого соединен с единичным выходом триггера коррекции, с первым входом первого Элемента И, через блок установки кода нуля с первыми входами блока управления и с первым входом первого элемента ИЛИ, второй вход которого соединен со втоЕядм выходом блока управления, третий вход которого соединен с выходом третьего элемента И, первый вход которого соединен с выходом блока сравнения, со вторым входом первого элемента И и через первый элемент НЕ с первым входом четвертого элемента И, второй вход соединен с выходом второго элемента НЕ и с первьл 1 входом пятого элемента И, второй вход которого соединен с выходом генератора тактовых импульсов и со вторым входом четвертого элемента И, а выход соединен с первым входом счетчика, второй вход которой соединен с первым входом второго элемента ИЛИ и с шиной Пуск, а выход соединен со вторым входом элемента ИЛИ, выход которого соединен с единичным входом триггера коррекции, нулевой вход KOTQporo соединен с выходом первого элемента И, при этом выход четвертого Элемента И соединен со вторым входом второго элемента И.

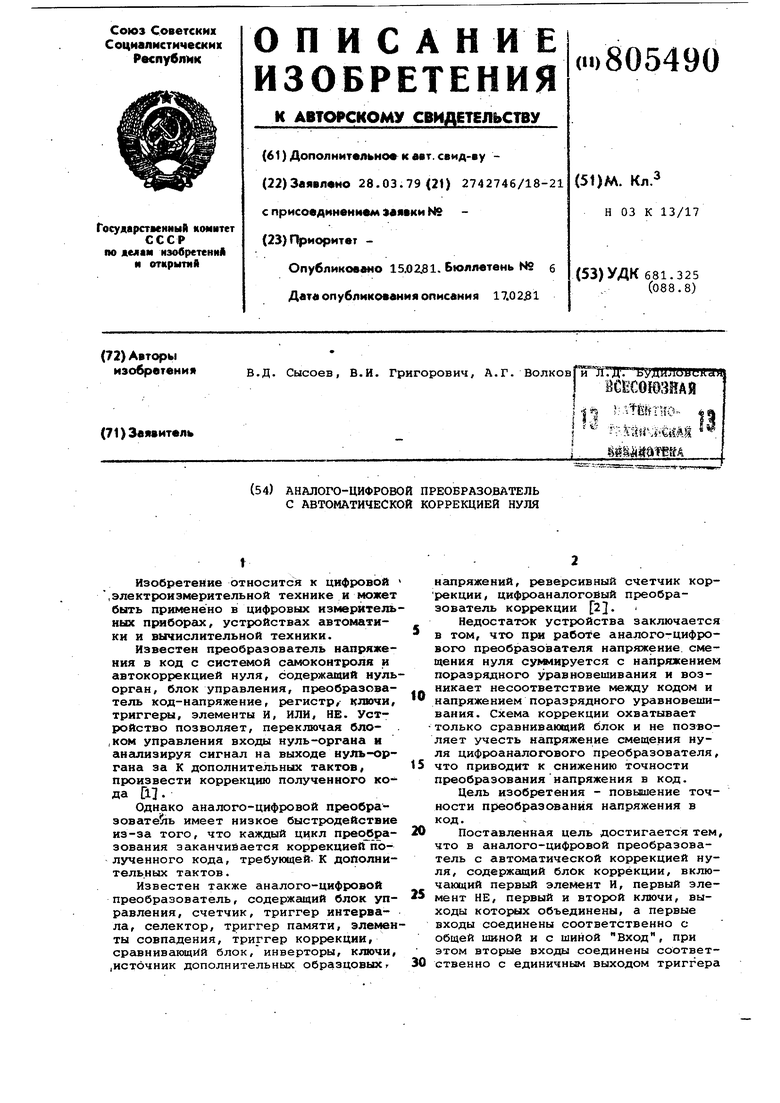

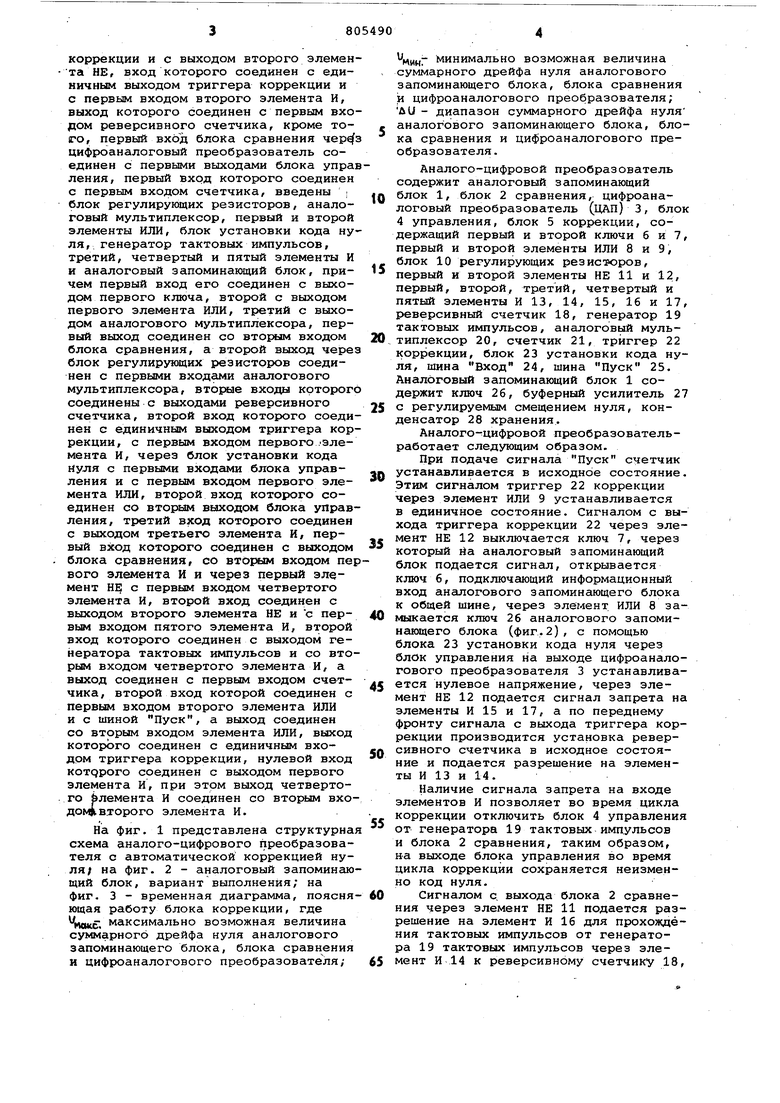

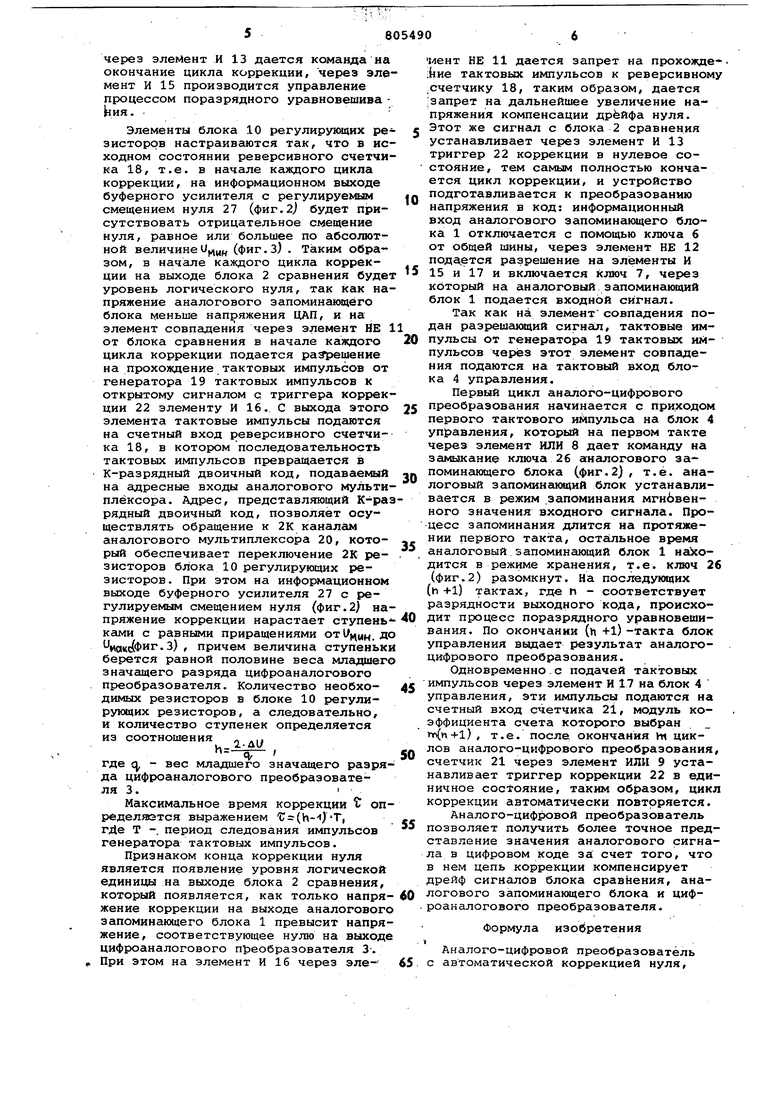

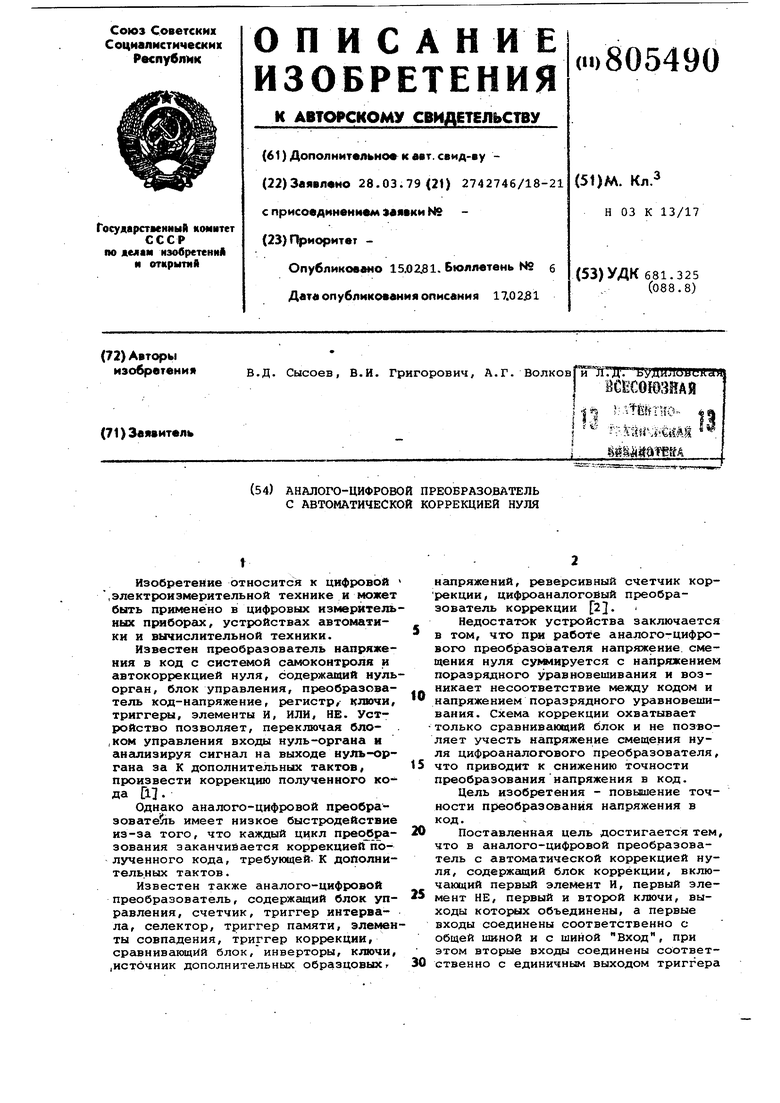

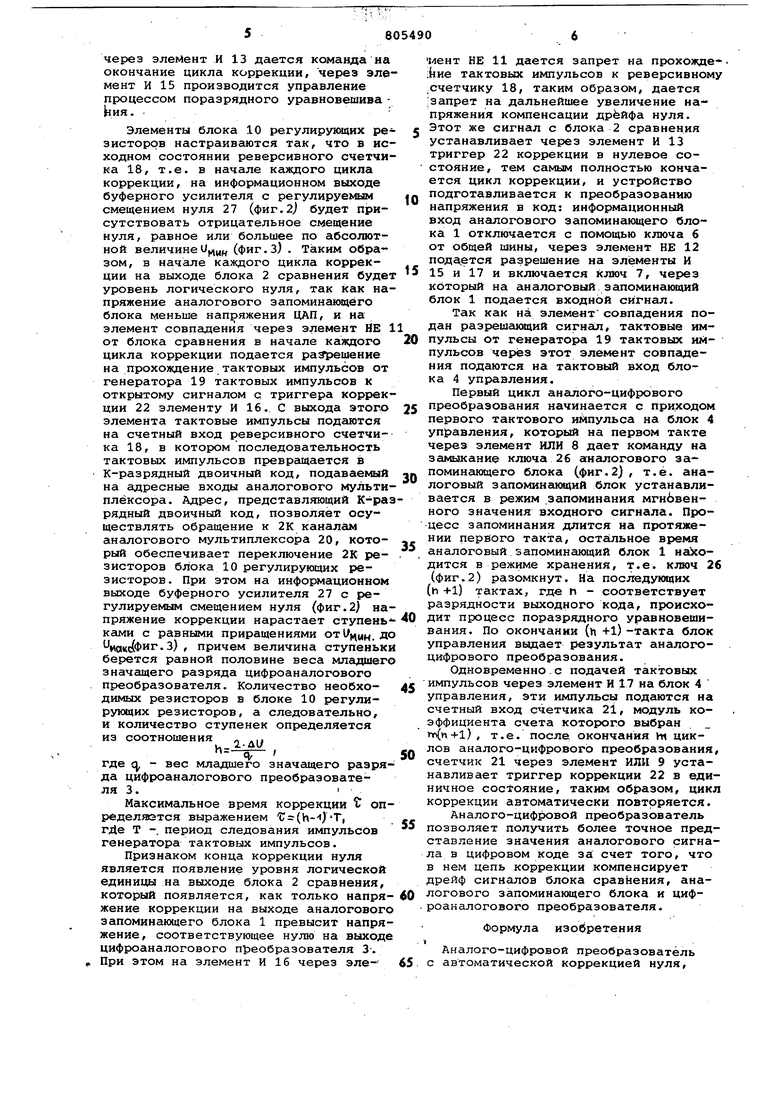

На фиг. 1 представлена структурная схема аналого-цифрового преобразователя с автоматической коррекцией нуля; на фиг. 2 - аналоговый запоминаиощий блок, вариант выполнения; на фиг. 3 - временная диаграмма, поясняющая работу блока коррекции, где Чммл. максимально возможная величина суммарного дрейфа нуля аналогового запоминающего блока, блока сравнения и цифроаналогового преобразователя/

минГ Минимально возможная величина суммарного дрейфа нуля аналогового запоминающего блока, блока сравнения и цифроаналогового преобразователя; ди - диапазон суммарного дрейфа нуля аналогового запоминающего блока, блока сравнения и цифроаналогового преобразователя.

Аналого-цифровой преобразователь содержит аналоговый запоминающий блок 1, блок 2 сравнения, цифроаналоговый преобразователь (ЦАП) 3, блок 4 управления, блок 5 коррекции, содержащий первый и второй ключи б и 7 первый и второй элементы ИЛИ 8 и 9, блок 10 регулирующих резис1юров, первый и второй элементы НЕ 11 и 12, первый, второй, третий, четвертый и пятый элементы И 13, 14, 15, 16 и 17 реверсивный счетчик 18, генератор 19 тактовых импульсов, аналоговый мультиплексор 20, счетчик 21, триггер 22 коррекции, блок 23 установки кода нуля, шина Вход 24, шина Пуск 25. Аналоговый запоминающий блок 1 содержит ключ 26, буферный усилитель 27 с регулируемым смещением нуля, конденсатор 28 хранения.

Ангшого-цифровой преобразовательработает следующим образом.

При подаче сигнала Пуск счетчик устанавливается в исходное состояние Этим сигналом триггер 22 коррекции через элемент ИЛИ 9 устанавливается в единичное состояние. Сигналом с выхода триггера коррекции 22 через элемент НЕ 12 выключается ключ 7, через который ria аналоговый запоминающий блок подается сигнал, открывается ключ 6, подключающий информационный вход аналогового запоминающего блока к общей шине, через элемент ИЛИ 8 замыкается ключ 26 аналогового запоминающего блока (фиг.2), с помощью блока 23 установки кода нуля через блок управления на выходе цифроаналогового преобразователя 3 устанавливается нулевое напряжение, через элемент НЕ 12 подается сигнал запрета на элементы И 15 и 17, а по переднему фронту сигнала с выхода триггера коррекции производится установка реверсивного счетчика в исходное состояние и подается разрешение на элементы И 13 и 14.

Наличие сигнала запрета на входе элементов И позволяет во время цикла коррекции отключить блок 4 управления от генератора 19 тактовых импульсов и блока 2 сравнения, таким образом, на выходе блока управления во время цикла коррекции сохраняется неизменно код нуля.

Сигналом с, выхода блока 2 сравнения через элемент НЕ 11 подается разрешение на элемент И 16 для прохождения тактовых импульсов от генератора 19 тактовых импульсов через элемент И 14 к реверсивному счетчику 18, через элемент И 13 дается командана окончание цикла коррекции, через эле мент И 15 производится управление процессом поразрядного уравновешива . Элементы блока 10 регулирующих ре зисторов настраиваются так, что в ис ходном состоянии реверсивного счетчи ка 18, т.е. в начале каждого цикла коррекции, на информационном выходе буферного усилителя с регулируемым смещением нуля 27 (фиг.2 будет присутствовать отрицательное смещение нуля, равное или большее по абсолютной величинеи „(фиг.З) . Таким образом, в начале каждого цикла коррекции на выходе блока 2 сравнения буде уровень логического нуля, так как на пряжение аналогового запоминакнцёго блока меньше напряжения ЦАП, и на элемент совпадения через элемент НЕ от блока сравнения в начале каждого цикла коррекции подается раз шение на прохождение тактовых импульсов от генератора 19 тактовых импульсов к открытому сигналом с триггера коррек ции 22 элементу И 16. С выхода этого элемента тактовые импульсы подаются на счетный вход реверсивного счетчика 18, в котором последовательность тактовых импульсов превращается в К-разрядный двоичный код, подаваемый на адресные входы аналогового мульти плексора. Адрес, представляющий К-ра рядный двоичный код, позволяет осуществлять обращение к 2К каналам аналогового мультиплексора 20, который обеспечивает переключение 2К резисторов блока 10 регулирующих резисторов. При этом на информационном выходе буферного усилителя 27 с регулируемым смещением нуля (фиг.2) на пряжение коррекции нарастает ступень ками с равными приращениями отУцин. яо адкd(Фиг. 3) , причем величина ступеньк берется равной половине веса младшего значащего разряда цифроаналогового преобразователя. Количество необходимых резисторов в блоке 10 регулирующих резисторов, а следовательно, и количество ступенек определяется из соотношения где q, - вес младшего значащего разряда цифроаналогового преобразователя 3.I Максимальное время коррекции t определязтся выражением C (h-t)T, гДе Т -. период следования импульсов генератора тактовых импульсов. Признаком конца коррекции нуля является появление уровня логической единицы на выходе блока 2 сравнения, который появляется, как только напряжение коррекции на выходе аналогового запоминающего блока 1 превысит напряжение, соответствующее нулю на выходе цифроаналогового п эеобразователя 3-. При этом на элемент И 16 через элемент НЕ 11 дается запрет на прохожде-. :йие тактовых импульсов к реверсивному .счетчику 18, таким образом, дается ;запрет на дальнейшее увеличение напряжения компенсации дрейфа нуля. Этот же сигнал с блока 2 сравнения устанавливает через элемент И 13 триггер 22 коррекции в нулевое состояние, тем самым полностью кончается цикл коррекции, и устройство подготавливается к преобразованию напряжения в код: информационный вход аналогового запоминающего блока 1 отключается с помощью ключа 6 от общей шины, через элемент НЕ 12 пода.ется разрешение на элементы И 15 и 17 и включается ключ 7, через который на аналоговый запоминающий блок 1 подается входной сигнал. Так как на элемент совпадения подан разрешакнций сигнал, тактовые импульсы от генератора 19 тактовых импульсов через этот элемент совпадения подаются на тактовый вход блока 4 управления. Первый цикл аналого-цифрового преобразования начинается с приходом первого тактового импульса на блок 4 управления, который на первом такте через элемент ИЛИ 8 дает команду на замыкание ключа 26 аналогового запоминающего блока (фиг,2) , т.е. аналоговый запоминающий блок устанавливается в режим запоминания мгнбвенного значения входного сигнала. Процесс запоминания длится на протяжении первого такта, остгшьное время аналоговый запоминающий блок 1 находится в режиме хранения, т.е. ключ 26 (фиг.2) разомкнут. На последующих (h H-l) тактах, где м - соответствует разрядности выходного кода, происходит процесс поразрядного уравновешивания. По окончании (h +l) -такта блок управления выдает результат аналогоцифрового преобразования. Одновременно.с подачей тактовых импульсов через элемент И 17 на блок 4 управления, эти импульсы подаются на счетный вход счетчика 21, модуль коэффициента счета которого выбран ) , т.е. после окончания hi циклов аналого-цифрового преобразования, счетчик 21 через элемент ИЛИ 9 устанавливает триггер коррекции 22 в единичное состояние, таким образом, цикл коррекции автоматически повторяется. Аналого-цифровой преобразователь позволяет получить более точное представление значения аналогового сигнала в цифровом коде за счет того, что в нем цепь коррекции компенсирует дрейф сигналов блока сравнения, аналогового запоминающего блока и цифроакалогового преобразователя. Формула изобретения Аналого-цифровой преобразователь с автоматической коррекцией нуля.

содержащий блок коррекции, включающкй первый.алемент И, первый элемент НЕ, первый и второйключи, выходы которых объединены, а первые входы соединены соответственно с общей шиной и с шиной Вход, при этом вторые входы соединены соответственно с единичным выходом триггера коррекции и с выходом второго элемента НЕ, вход которого соединен с единичным выходом триггера коррекции и с первым входом второго элемента И, выход которого соединен с первым входом реверсивного счетчика, креме того, первый вход блока сравнения через цифроаналоговый преобразователь соединен с первыми выходами блокг управления, первый вход которого соединен с первым входом счетчика, отличающийся тем, что, с целью повышения точности преобразования напряжения в код, введены блок регулирующих резисторов, аналоговый мультиплекссэр, первый и второй элементы ИЛИ, блок установки кода нуля, генератор тактовых импульсов, третий, четвертый и пятый элементы И и аналоговый запоминающий блок, первый вход которого соединен с выходом первого ключа, второй с выходом пер:вого элемента ИЛИ, третий с выходом аналогового мультиплексора, первый выход соединен со вторым входом блока сравнения, а второй выход через блок регулирующих резисторов соединен с первыми входами аналогового мультиплексора, вторые входы которого соединены с выходами реверсивного

счетчика, второй вход кбторого соединен с единичным выходом триггера коррекции, с первым входом первого элемента И, через блок установки кода нуля с первыми входами блока управления и с первым входом первого злемента ИЛИ, второй вход которого соединен со вторым выходом блока управления, третий вход которого соединен с выходом третьего элемента И, первый вход которого соединен с выходом блока

сравнения, со вторым входом первого элемента И и через первый элемент НЕ с первым входом четвертого элемента И, а второй вход соединен с выходом второго элемента НЕ с первьф входом пятого элемента и, второй вход которого соединен с выходом генератора тактовых импульсов и со вторым входом четвертого элемента И, а выход соединен с первым входом счётчика, второй вход которого соединен.с первым входом второго элемента ИЛИ и с шиной Пуск, а выход соединен со вторым входом элемента ИЛИ, выход которого соединен с единичным входом

триггера коррекции, нулевой вход ко-. торого соединен с выходом первого элемента И, при этом выход четвертого элемента И соединен со вторым входом второго элемента И.

Источники информации,

принятые во внимание при экспертизе

1.Авторское свидетельство СССР

379979, кл. Н 03 К 13/17, 20.04.71.

2.Авторское свидетельство СССР

№349100, кл. Н 03 К 13/17, 11.01.71.

п п п п п п п

Тцар. маис

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1981 |

|

SU945978A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1988 |

|

SU1594699A1 |

| Устройство для регистрации информации | 1984 |

|

SU1234858A1 |

| Аналого-цифровой преобразователь с коррекцией погрешности | 1988 |

|

SU1688473A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1989 |

|

SU1709526A1 |

| Параллельно-последовательный п-разрядный аналого-цифровой преобразователь с автоматической коррекцией функции преобразования | 1988 |

|

SU1732471A1 |

| Функциональный преобразователь | 1987 |

|

SU1462369A1 |

| УСТРОЙСТВО ДЛЯ ВВОДА АНАЛОГОВЫХ СИГНАЛОВ | 1991 |

|

RU2017203C1 |

| Многоканальное устройство для регистрации аналоговых и цифровых сигналов | 1988 |

|

SU1564649A1 |

| Устройство для поворота вектора | 1982 |

|

SU1076910A1 |

Авторы

Даты

1981-02-15—Публикация

1979-03-28—Подача