Изобретение относится к электронным дискретным устройствам автоматики, телемеханики и вычислительной техники, предназначено для сопряжени двух информационных каналов, когда необходимо обеспечить одновременные запись и считывание, и может быть использовано в телеметрических систе мах, предназначенных для сбора и хра нения информации. Известно устройство сопряжения,ко торое содержит последовательно соеди ненные элементы задержки, счетчик считывания, связанный с дешифратором считывания, компаратор, счетчик запи си, подключенный к накопителю через дешифратор записи, и элемент И.Оно позволяет сопрягать информационные каналы, формирует сигнал Очистка накопителя и исключает наложение избыточной информации на заранее записанную при переполнении накопителя 1. Однако указанное устройство не позволяет реализовать одновременные запись и считывание непрерывно следующего асинхронного потока цифровых данных. Известно также устройство сопряже ния, которое содержит четное число накопителей (от 2-х и более), записью в которые управляют младшие разряды адреса. Указанный способ управления памятью (расслоение памяти) позволяет увеличить пропускную способность памяти, однако не обеспечивает асинхронную запись и считывание информации 2 . Наиболее близким к предлагаемому изобретению по технической сущности является устройство сопряжения, которое содержит три ЗУ каждое с индикатором состояния, элементы И, которые обеспечивают поступление входных данных в нужное ЗУ. 5локи,ввода и вывода управляют соответственно вводом и выводом данных. Схема запрета формирует сигна11ы, которые используются блоком ввода для запрета вывода на время ввода . Однако известное устройство имеет относительно невысокое быстродействие при выдаче данных из накопителя: а именно, при неблагоприятном соотношении потоков требований на считывание и запись может затянуться время ожидания считываемого массива информации. Обращение к накопителям известного устройства организовано таким образом, что если в первый наопитель записывается информация,то читывание из него блокируется.Обраение на считывание в этом случае азрешено из второго и третьего наопителей.

Если скорость выдачи информации ревышает скорость записи, то после Очистки второго и третьего накопиелей устройство не может считать инормацию из первого накопителя до тех пор, пока запись в него не закончится. Это приводит к затягиванию вреени ожидания выдачи данных до полного заполнения первого накопителя.

Цель изобретения - повышение быстродействия.

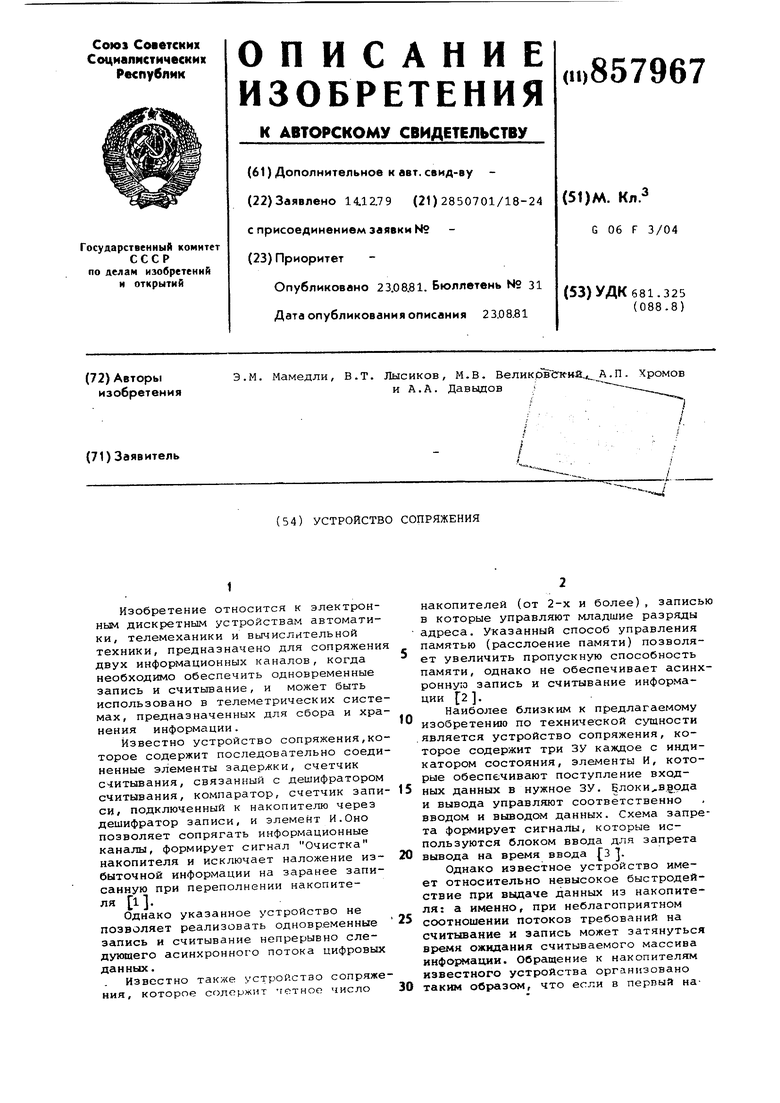

Поставленная цель достигается тем, то в устройство сопряжения, содержащее, два входных регистра, два блока стековой памяти, счетчик записи и счетчик чтения, два выходных регистра, коммутатор, четыре элемента И и индикатор состояния памяти, причеМ первый вход устройства соединен с информационными входами входных регистров, второй вход устройства соединен с первыми входами первого и второго элементов И и с синхронизирующим входом индикатора состояния памяти,выходы первого и второго элементов И соединены с управляющими входами соответственно первого и второго входных регистров, выход входного регистра соединен с информационным входом соответствующего блока стековой памяти, выход блока- стековой памяти соединен с информационным входом соответствующего выходного регистра, вьаходы выходных регистров соединены с информационными входами коммутатора, выход которого является первым выходом устройства, третий вход устройства соединен с первьми входами третьего и четвертого элемента И и с первым запускающим входом индикатора состояния памяти, первый и второй выходы которого соединены соответственно с вторым выходом устройства,с блокирующим входом счетчика адреса записи третьим выходом устройства, с блокирующим входом счетчика адреса чтения, выход счетчика адреса чтения соединен с адресными входами чтения блоков стековой памяти, Первый информационный выход счетчика адреса записи соединен с адресными вход с1ми записи блоков стековой памяти, выход третьего элементу И соединен с входом считывания первого блока стековой памяти и с управляющим входом первого выходного регистра, а выход четвертого элемента И соединен со входом считывания второго блока стековой Ламяти и с управляющим входом второго выходного регистра, введены распределитель импульсов записи, распределитель импульсов чтения, блок асинхронной за писи, схема сравнения, регистр начального адреса и блок формированияначалу сообщения, причем второй и третий входы устройства соединены с запуска1ощими входами распределителей импульсов соответственно записи и чтения, первый выход распределителя импульсов записи соединен с вторым входом первого элемента И и с первым входом блока асинхронной записи, второй выход распределителя импульсов записи соединен с вторым входом элемента И и с вторым входом блока асинхронной записи, третий выход аспределителя импульсов записи соединен с счетным входом счетчика адреса записи, второй информационный выход и информационный вход которого соединены с информационными соответственно входом и выходом регистра начального адреса, первый и второй управляющие входы которого соединены соответственно с выходом блока формирования начала сообщения и с первым выходом индикатора состояния памяти, выходы третьего и четвертого элементов И соединены соответственнЪ с третьим и четвертым входами блока асинхронной записи, первый и второй выходы которого соединены с входами записи соответственно первого и второго блоков стеков-ой памяти, первый управляющий вход коммутатора и второй вход третьего элемента И, второй управляющий вход коммутатора и второй вход четвертого элемента И соединены соответственно с первым и вторым входами распределителя импульсов чтения, третий выход которого соединен с счетным входом счетчика адреса чтения, выход которого н первый информационный выход счетчика адреса записи через схему сравнения соединены с вторым запускающим входом индикатора состояния Пс1мяти, а выход блока формирования начала сообщения соединен с вторым входом устройства.

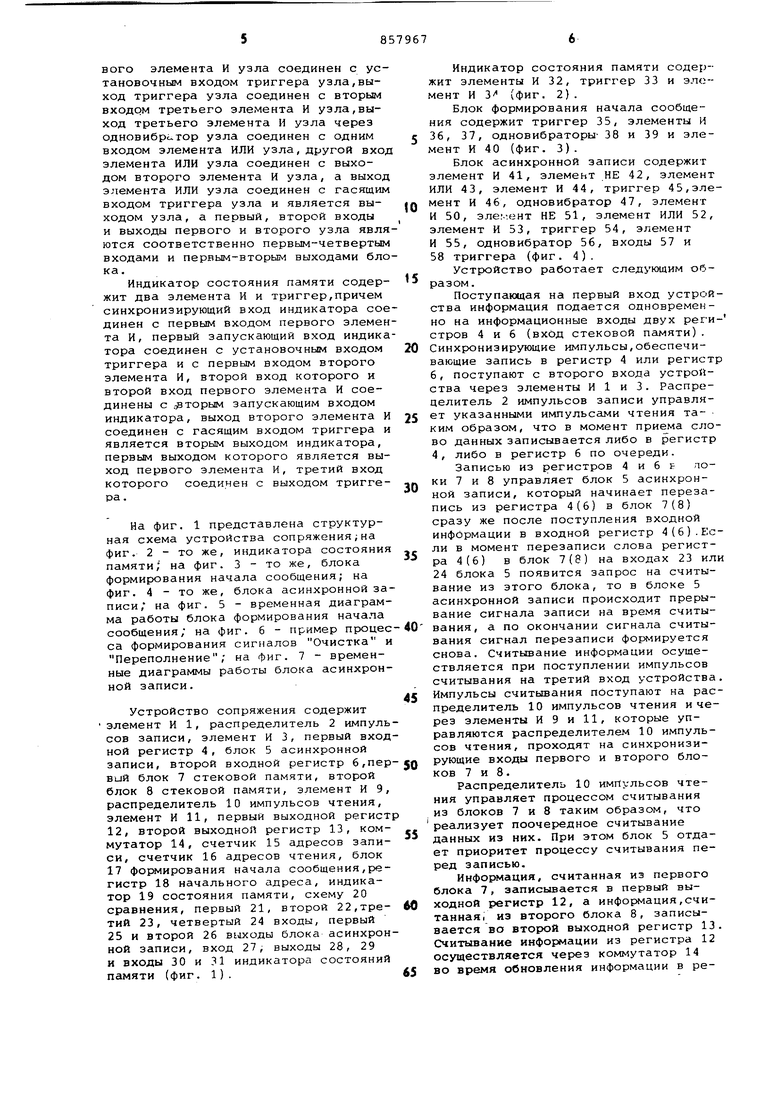

Блок формирования начала сообщения содержит триггер, три элемента И и два одновибратора, причем вход блока соединен с первыми входами элементов и и с установочным входом триггера, выходы которого соединены с вторыми входами первого и второго элементов И, выходы первого и второго элементов И через соответствующие одновибраторы соединены соответственно с вторым и третьим входами третьего элемента И, выход которого является выходом блока.

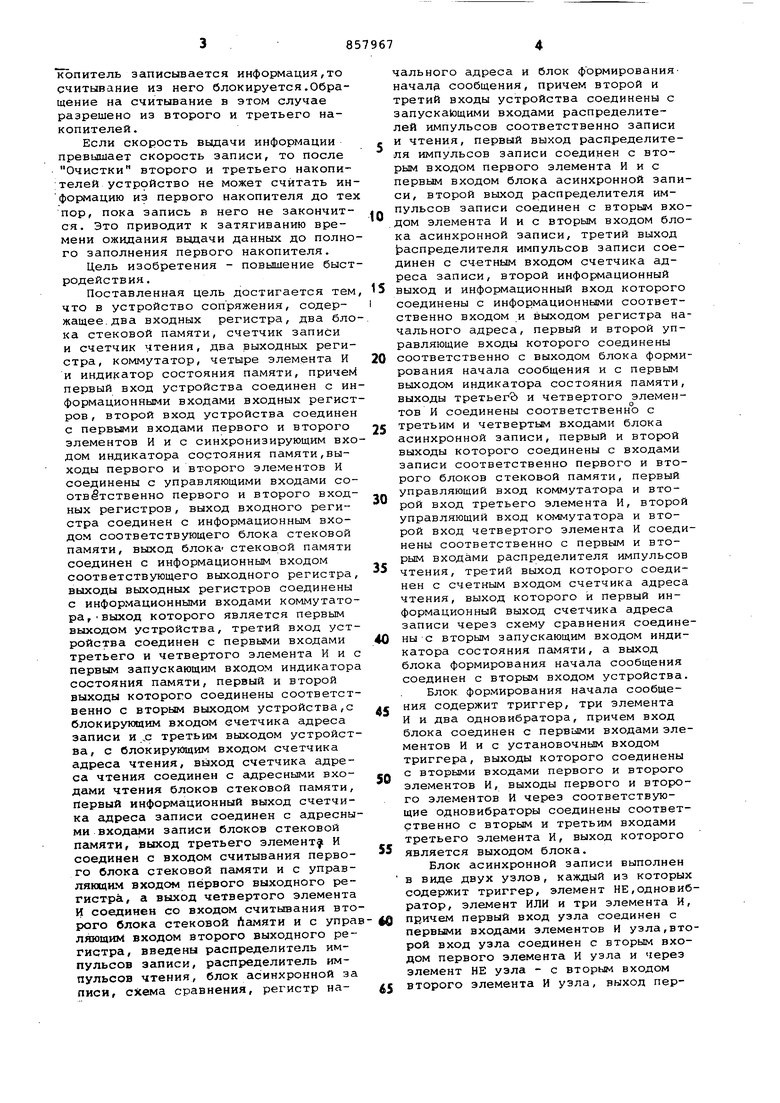

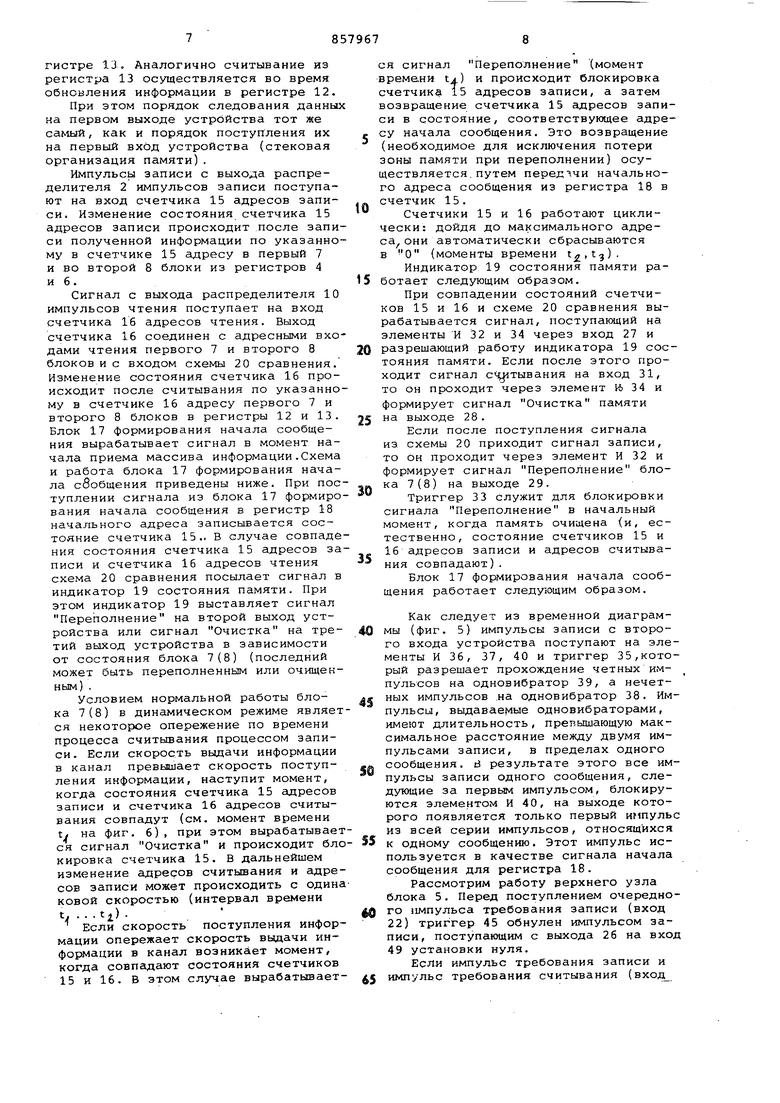

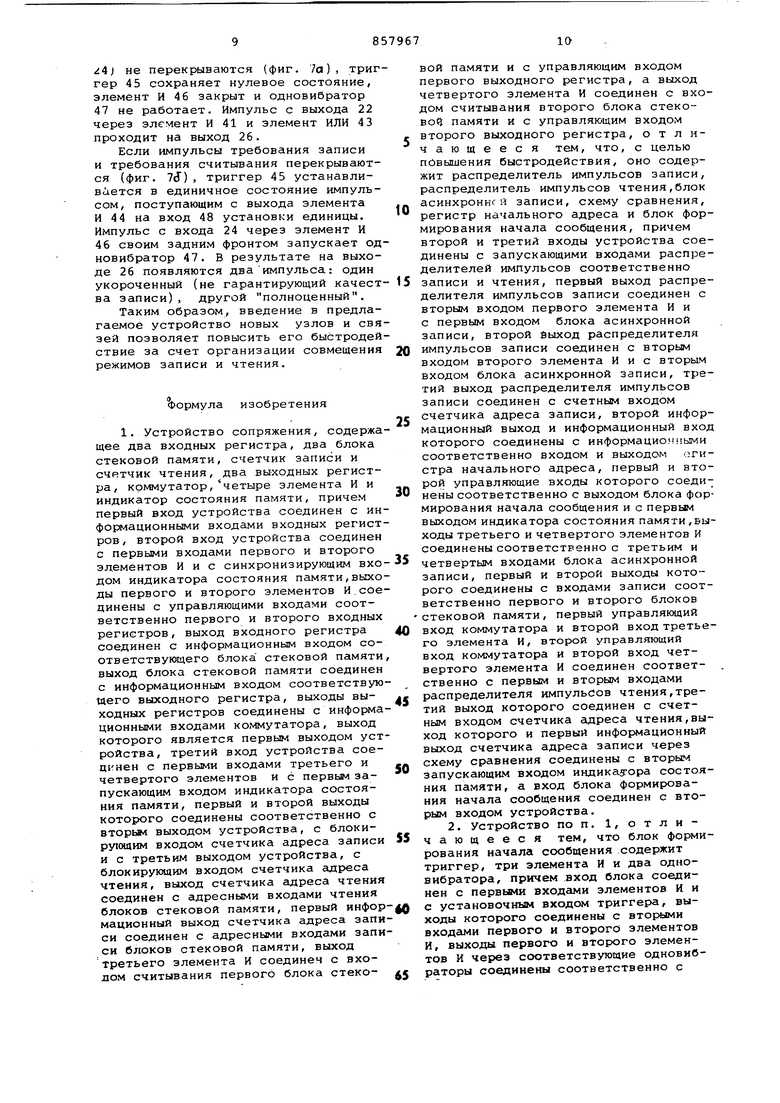

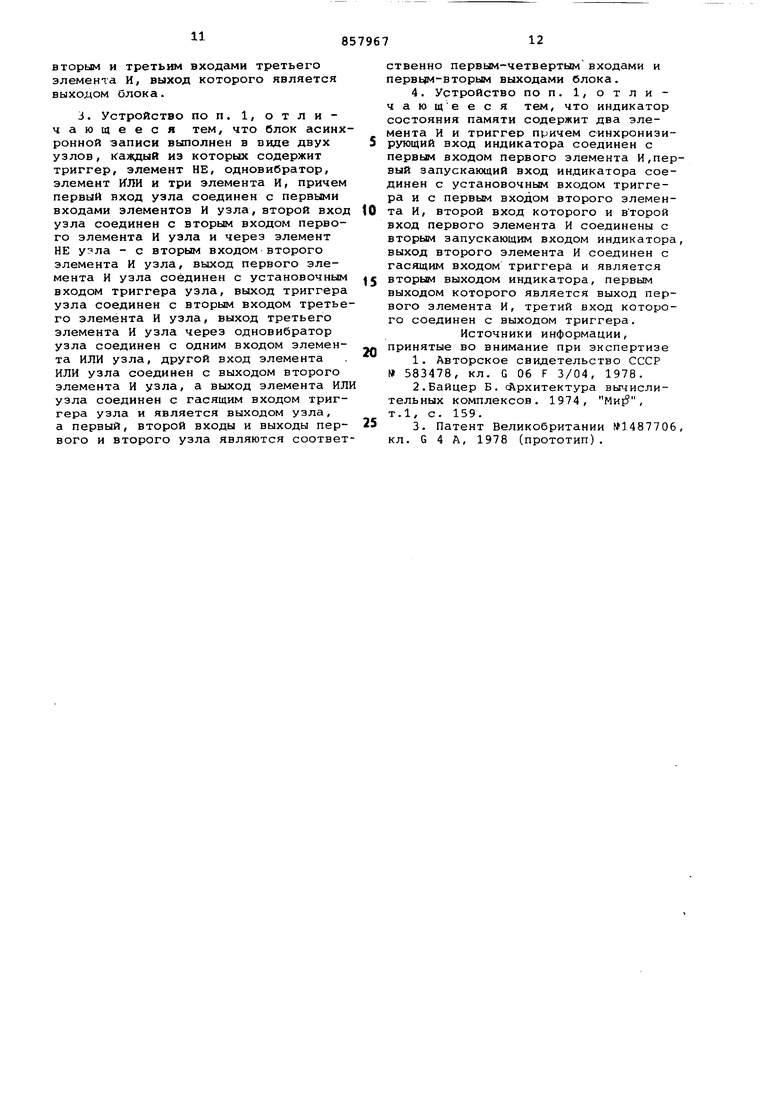

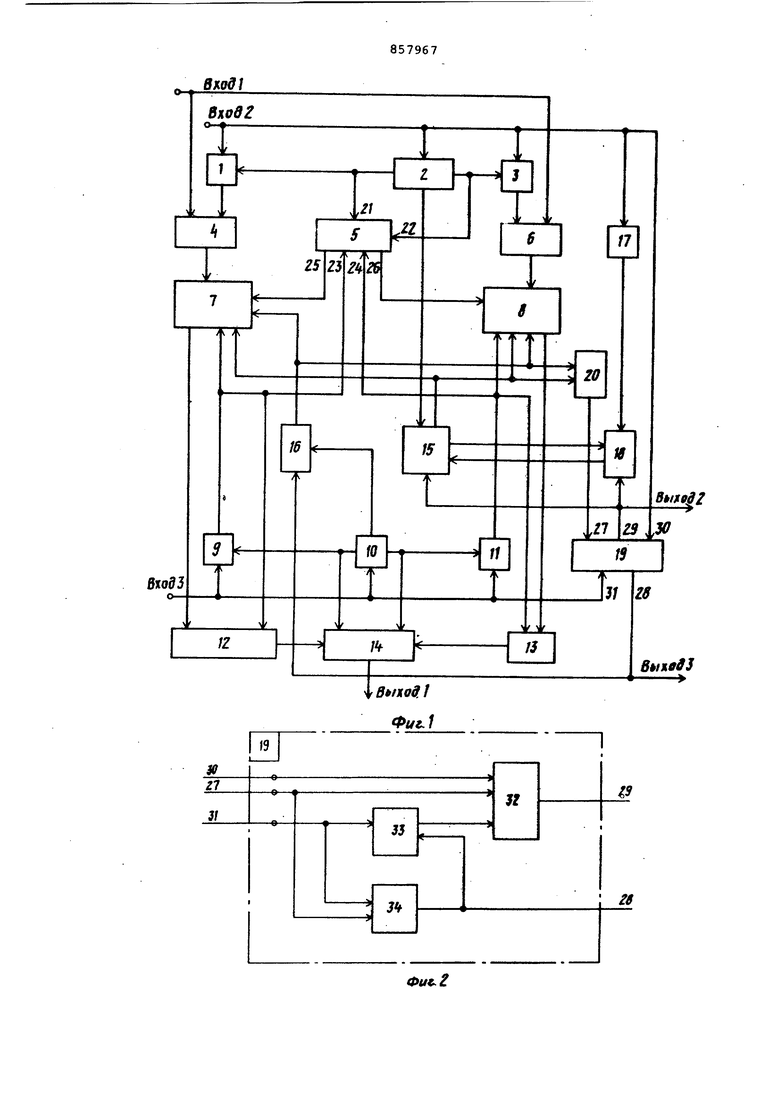

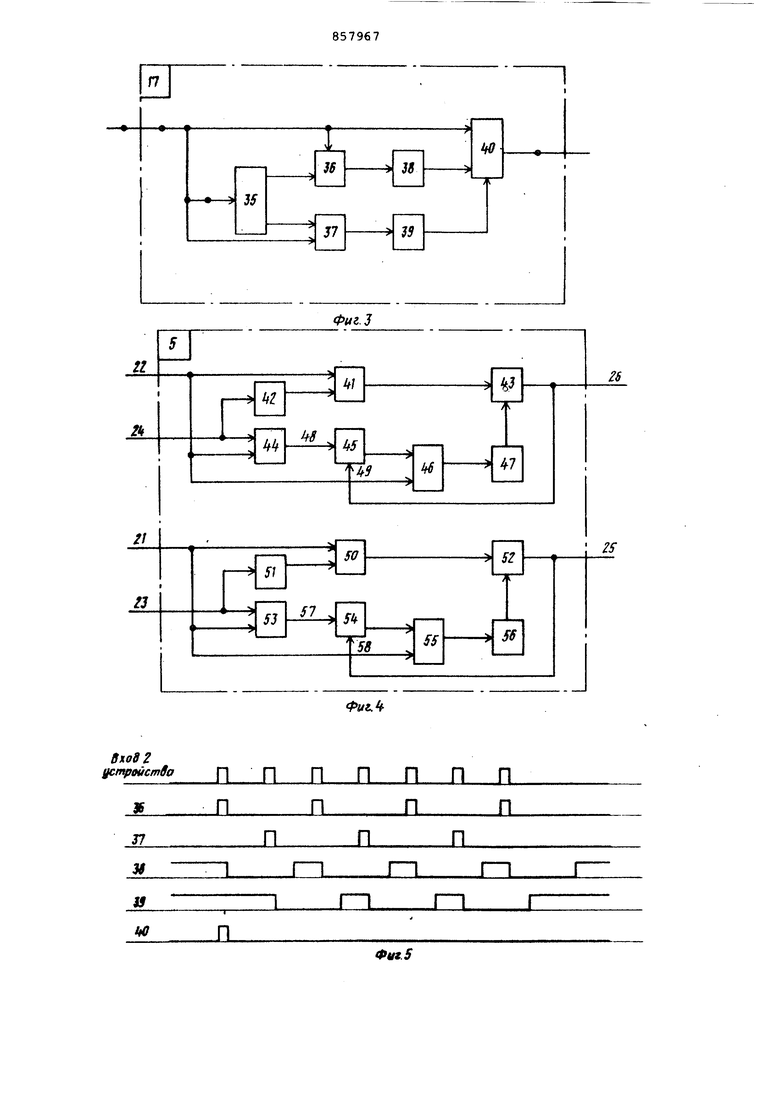

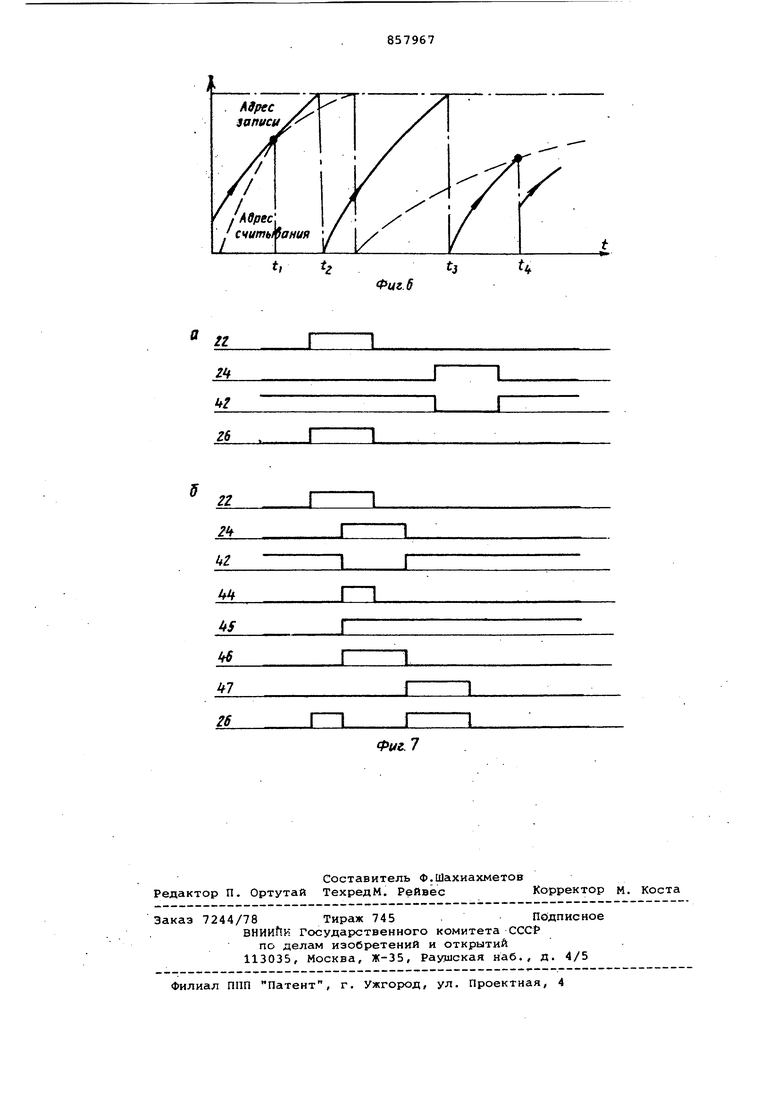

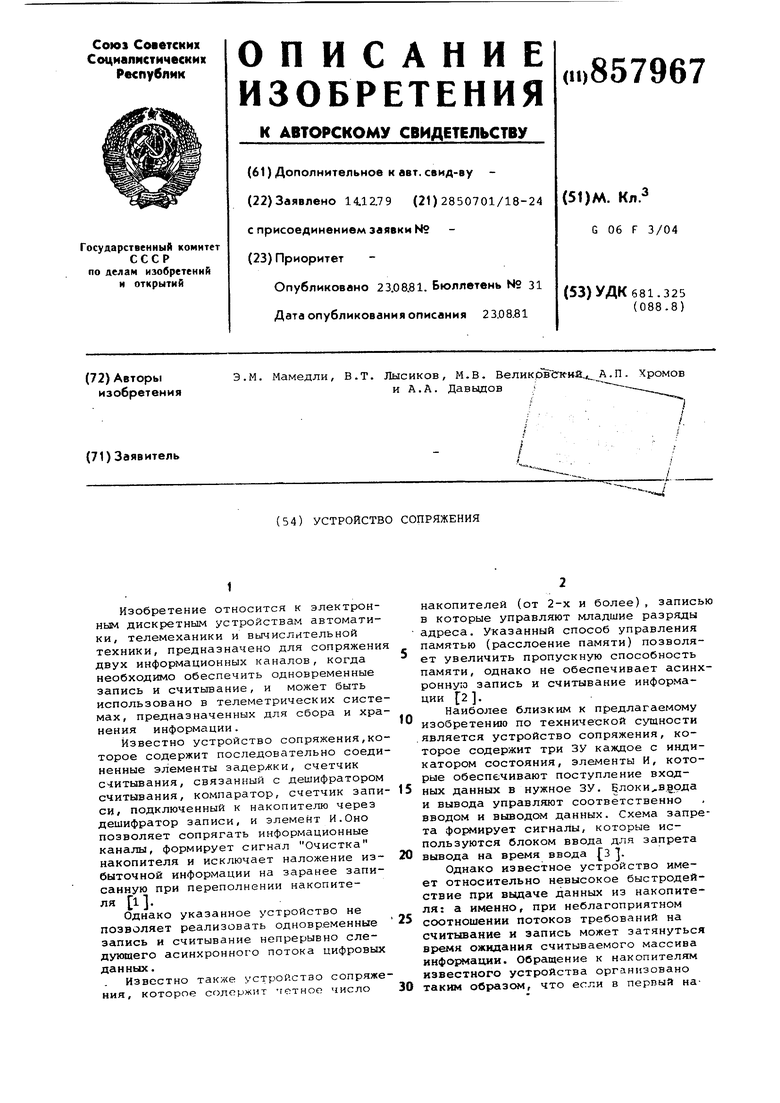

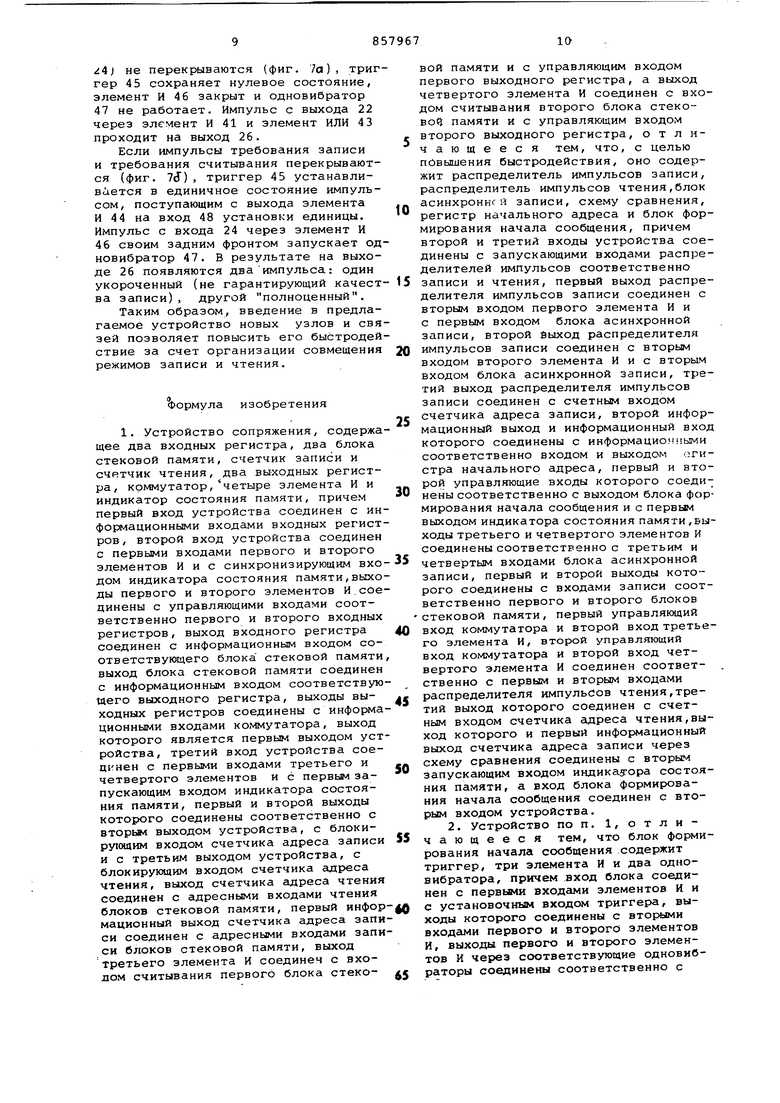

Блок асинхронной записи выполнен в виде двух узлов, каждый из которых содержит триггер, элемент НЕ,одновибратор, элемент ИЛИ и три элемента И, причем первый вход узла соединен с первыми входс1ми элементов И узла,второй вход узла соединен с вторым входом первого элемента И узла и через элемент НЕ узла - с вторым входом второго элемента И узла, выход первого элемента И узла соединен с ус тановочным входом триггера узла,выход триггера узла соединен с вторым входом третьего элемента И узла,выход третьего элемента И узла через одновибр -тор узла соединен с одним входом элемента ИЛИ узла,другой вхо элемента ИЛИ узла соединен с выходом второго элемента И узла, а выхо элемента ИЛИ узла соединен с гасящим входом триггера узла и является выходом узла, а первый, второй входы и выходы первого и второго узла явл ются соответственно первым-четвертым входами и первым-вторым выходами бло ка . Индикатор состояния памяти содер жит два элемента И и триггер,причем синхронизирующий вход индикатора сое динен с первым входом первого элеме та И, первый запускающий вход индика тора соединен с установочным входом триггера и с первьлм входом второго элемента И, второй вход которого и второй вход первого элемента И соединены с эвторым запускающим входом индикатора, выход второго элемента И соединен с гасящим входом триггера и является вторым выходом индикатора, первым выходом которого является выход первого элемента И, третий вход которого соединен с выходом триггера. На фиг. 1 представлена структурная схема устройства сопряжения;на фиг. 2 - то же, индикатора состояния памяти; на фиг. 3 - то же, блока формирования начала сообщения; на фиг. 4 - то же, блока асинхронной за пйси, на фиг. 5 - временная диаграмма работы блока формирования начала сообщения; на фиг. 6 - пример процес са формирования сигналов Очистка и Переполнение ; на фиг. 7 - временные диаграммы работы блока асинхронной записи. Устройство сопряжения содержит элемент И 1, распределитель 2 импуль сов записи, элемент И 3, первый вход ной регистр 4, блок 5 асинхронной записи, второй входной регистр 6,пер вый блок 7 стековой памяти, второй блок 8 стековой памяти, элемент И 9, распределитель 10 импульсов чтения, элемент И 11, первый выходной регист 12, второй выходной регистр 13, коммутатор 14, счетчик 15 адресов записи, счетчик 16 адресов чтения, блок 17 формирования начала сообщения,регистр 18 начального адреса, индикатор 19 состояния памяти, схему 20 сравнения, первый 21, второй 22,третий 23, четвертый 24 входы, первый 25 и второй 26 выходы блока асинхрон ной записи, вход 27, выходы 28, 29 и входы 30 и 31 индикатора состояний памяти (фиг. 1). Индикатор состояния памяти содержит элементы И 32, триггер 33 и эломент И З (фиг. 2) . Блок формирования начала сообщения содержит триггер 35, элементы И 36, 37, одновибраторы- 38 и 39 и элемент И 40 (фиг. 3). Блок асинхронной записи содержит элемент И 41, элемент НЕ 42, элемент ИЛИ 43, элемент И 44, триггер 45,элемент И 46, одновибратор 47, элемент И 50, элемент НЕ 51, элемент ИЛИ 52, элемент И 53, триггер 54, элемент И 55, одновибратор 56, входы 57 и 58 триггера (фиг. 4). Устройство работает следующим образом. Поступающая на первый вход устройства информация подается одновременно на информационные входы двух регистров 4 и 6 (вход стековой памяти). Синхронизирующие импульсы,обеспечивающие запись в регистр 4 или регистр 6, поступают с второго входа устройства через элементы И 1 и 3. Распределитель 2 импульсов записи управляет указанными импульсами чтения таким образом, что в момент приема слово данных записывается либо в регистр 4, либо в регистр 6 по очереди. Записью из регистров 4 и 6 Е локи 7 и 8 управляет блок 5 асинхронной записи, который начинает перезапись из регистра 4(6) в блок 7(8) сразу же после поступления входной информации в входной регистр 4(6).Если в момент перезаписи слова регистра 4(6) в блок 7(8) на входах 23 или 24 блока 5 появится запрос на считывание из этого блока, то в блоке 5 асинхронной записи происходит прерывание сигнала записи на время считывания, а по окончании сигнала считывания сигнал перезаписи формируется снова. Считывание информации осуществляется при поступлении импульсов считывания на третий вход устройства. Импульсы считьшания поступают на распределитель 10 импульсов чтения и через элементы И 9 и 11, которые управляются распределителем 10 импульсов чтения, проходят на синхронизирующие входы первого и второго блоков 7 и 8. Распределитель 10 импульсов чтения управляет процессом считывания из блоков 7 и 8 таким образом, что реализует поочередное считывание данных из них. При этом блок 5 отдает приоритет процессу считывания перед записью. Информация, считанная из первого блока 7, записывается в первый выходной регистр 12, а информация,считанная, из второго блока 8, записывается во второй выходной регистр 13. Считывание информации из регистра 12 осуществляется через коммутатор 14 во время обновления информации в регистре 13, Аналогично считывание из регистра 13 осуществляется во время обновления информации в регистре 12. При этом порядок следования данны на первом выходе устройства тот же самый, как и порядок поступления их на первый вход устройства (стековая организация памяти). Импульсы записи с выхода распределителя 2 импульсов записи поступают на вход счетчика 15 адресов записи. Изменение состояния счетчика 15 адресов записи происходит после запи си полученной информации по указанно му в счетчике 15 адресу в первый 7 и во второй 8 блоки из регистров 4 и б. Сигнал с выхода распределителя 10 импульсов чтения поступает на вход счетчика 16 адресов чтения. Выход счетчика 16 соединен с адресными вхо дами чтения первого 7 и второго 8 блоков и с входом схемы 20 сравнения. Изменение состояния счетчика 16 происходит после считывания по указанно му в счетчике 16 адресу первого 7 и второго 8 блоков в регистры 12 и 13 Блок 17 формирования начала сообщения вырабатывает сигнал в момент начала приема массива информации.Схема и работа блока 17 формирования начала обобщения приведены ниже. При пос туплении сигнала из блока 17 формиро вания начала сообщения в регистр 18 начального адреса записывается состояние счетчика 15., В случае совпаде ния состояния счетчика 15 адресов за писи и счетчика 16 адресов чтения схема 20 сравнения посылает сигнал в индикатор 19 состояния памяти. При этом индикатор 19 выставляет сигнал Переполнение на второй выход устройства или сигнал Очистка на тре тий выход устройства в зависимости от состояния блока 7(8) (последний может быть переполненным или очищен ным) . Условием нормальной работы блока 7(8) в динамическом режиме являе ся некоторое опережение по времени процесса считывания процессом записи. Если скорость выдачи информации в канал превышает скорость поступления информации, наступит момент, когда состояния счетчика 15 адресов записи и счетчика 16 адресов считывания совпадут (см. момент времени t, на фиг. 6), при этом вырабатывае ся сигнал Очистка и происходит бл кировка счетчика 15. В дальнейшем изменение адресов считывания и адре сов записи может происходить с один ковой скоростью (интервал времени t. ...ti). Если скорость поступления инфор мации опережает скорость выдачи информации в канал возникает момент, когда совпгщают состояния счетчиков 15 и 16. В этом случае вырабатывает ся сигнал Переполнение (момент времени .л) и происходит блокировка счетчика i5 адресов записи, а затем возвращение счетчика 15 адресов записи в состояние, соответствующее адресу начала сообщения. Это возвращение (необходимое для исключения потери зоны памяти при переполнении) осуществляется, путем передачи начального адреса сообщения из регистра 18 в счетчик 15. Счетчики 15 и 16 работают циклически: дойдя до максимального адреса они автоматически сбрасываются в О (моменты времени t.t)Индикатор 19 состояния памяти работает следующим образом. При совпадении состояний счетчиков 15 и 16 и схеме 20 сравнения вырабатывается сигнал, поступающий на элементы И 32 и 34 через вход 27 и разрешающий работу индикатора 19 состояния памяти. Если после этого проходит сигнал с Ц1Тывания на вход 31, то он проходит через элемент 14 34 и формирует сигнал Очистка памяти на выходе 28. Если после поступления сигнала из схемы 20 приходит сигнал записи, то он проходит через элемент И 32 и формирует сигнал Переполнение блока 7(8) на выходе 29. Триггер 33 служит для блокировки сигнала Переполнение в начальный момент, когда память очищена (и, естественно, состояние счетчиков 15 и 16 адресов записи и адресов считывания совпадают). Блок 17 формирования начала сообщения работает следующим образом. Как следует из временной диаграммы (фиг. 5) импульсы записи с второго входа устройства поступают на элементы И 36, 37, 40 и триггер 35,который разрешает прохождение четных импульсов на одновибратор 39, а нечетных импульсов .на одновибратор 38. Импульсы, выдаваемые одновибраторами, имеют длительность, превышающую максимальное расстояние между двумя импульсами записи, в пределах одного сообщения, в результате этого все импульсы записи одного сообщения, следующие за первьм импульсом, блокируются элементом И 40, на выходе которого появляется только первый иппульс из всей серии импульсов, относящихся к одному сообщению. Этот импульс используется в качестве сигнала начала сообщения для регистра 18. Рассмотрим работу верхнего узла блока 5. Перед поступлением очередного 1мпульса требования записи (вход 22) триггер 45 обнулен импульсом записи, поступающим с выхода 26 на вход 49 установки нуля. Если импульс требования записи и шлпульс требования считывания (вход ij4j не перекрываются (фиг. la}, триг гер 45 сохраняет нулевое состояние, элемент И 46 закрыт и одновибратор 47 не работает. Импульс с выхода 22 через элемент И 41 и элемент ИЛИ 43 проходит на выход 26. Если импульсы требования записи и требования считывания перекрываются (фиг. 7J), триггер 45 устанавлив 1ется в единичное состояние импульсом, поступающим с выхода элемента И 44 на вход 48 установки единицы. Импульс с входа 24 через элемент И 46 своим задним фронтом запускает од новибратор 47. В результате на выходе 26 появляются дваимпульса: один укороченный (не гарантирующий качест ва записи), другой полноценный. Таким образом, введение в предлагаемое устройство новых узлов и свя зей позволяет повысить его быстродей ствие за счет организации совмещения режимов записи и чтения. Формула изобретения 1. Устройство сопряжения, содержа щее два входных регистра, два блока стековой памяти, счетчик записи и счетчик чтения, два выходных регистра, коммутатор,четыре элемента И и индикатор состояния памяти, причем первый вход устройства соединен с ин формационными входами входных регист ров, второй вход устройства соединен с первыми входами первого и второго элементов И и с синхронизирующим вхо дом индикатора состояния памяти,выхо ды первого и второго элементов И.сое динены с управляющими входами соответственно первого и второго входных регистров, выход входного регистра соединен с информационным входом соответствующего блока стековой памяти выход блока стековой памяти соединен с информационным входом соответствую шего выходного регистра, выходы выходных регистров соединены с информа ционными входами коммутатора, выход которого является первым выходом устройства, третий вход устройства соединен с первыми входами третьего и четвертого элементов и с первым запускающим входом индикатора состояния памяти, первый и второй выходы которого соединены соответственно с вторьм выходом устройства, с блокирующим входом счетчика адреса записи и с третьим выходом устройства, с блокирующим входом счетчика чтения, выход счетчика адреса чтения соединен с адресными входами чтения блоков стековой памяти, первый информационный выход счетчика адреса записи соединен с адресными входами записи блоков стековой памяти, выход третьего элемента И соединен с входом считывания первого блока стековой памяти и с управляющим входом первого выходного регистра, а выход четвертого элемента И соединен с входом считывания второго блока стековоЧ памяти и с управляющим входом второго выходного регистра, отличающееся тем, что, с целью повышения быстродействия, оно содержит распределитель импульсов записи, распределитель импульсов чтения,блок асинхроннси записи, схему сравнения, регистр начального адреса и блок формирования начала сообщения, причем второй и третий входы устройства соединены с запускающими входами расп зеделителей импульсов соответственно записи и чтения, первый выход распределителя импульсов записи соединен с вторым входом первого элемента И и с первым входом блока асинхронной записи, второй выход распределителя импульсов записи соединен с вторым входом второго элемента И и с вторым входом блока асинхронной записи, третий выход распределителя импульсов записи соединен с счетным входом счетчика адреса записи, второй информационный выход и информационный вход которого соединены с информационными соответственно входом и выходом (згистра начального адреса, первый и второй управляющие входы которого соединены соответственно с выходом блока формирования начала сообщения и с первым выходом индикатора состояния памяти,выходы третьего и четвертого элементов И соединены соответственно с третьим и четвертым входами блока асинхронной записи, первый и второй выходы которого соединены с входами записи соответственно первого и второго блоков стековой памяти, первый управляющий вход коммутатора и второй вход третьего элемента И, второй управляющий вход коммутатора и второй вход четвертого элемента И соединен соответственно с первым и вторым входами распределителя импульсов чтения,третий выход которого соединен с счетным входом счетчика адреса чтения,выход которого и первый информационный выход счетчика адреса записи через схему сравнения соединены с вторым запускающим входом индикад-ора состояния памяти, а вход блока формирования начала сообщения соединен с вторым входом устройства. 2. Устройство по п. 1, отличающееся тем, что блок формирования начала сообщения содержит триггер, три элемента И и два одновибратора, причем вход блока соединен с первыми входами элементов И и с установочным входом триггера, выходы которого соединены с вторыми входами первого и второго элементов И, выходы первого и второго элементов И через соответствующие одновибраторы соединены соответственно с

вторым и третьим входами третьего элемента И, выход которого является выходом блока.

3. Устройство по п. 1, отличающееся тем, что блок асинхронной записи выполнен в виде двух узлов, каяодый из которых содержит триггер, элемент НЕ, одновибратор, элемент КЛИ и три элемента И, причем первый вход узла соединен с первыми входами элементов И узла, второй вход узла соединен с вторым входом первого элемента И узла и через элемент НЕ узла - с вторым входом второго элемента И узла, выход первого элемента И узла соединен с установочным входом триггера узла, выход триггера узла соединен с вторым входом третьего элемента И узла, выход третьего элемента И узла через одновибратор узла соединен с одним входом элемента ИЛИ узла, другой вход элемента . ИЛИ узла соединен с выходом второго элемента И узла, а выход элемента ИЛ узла соединен с гасящим входом триггера узла и является выходом узла, а первый, второй входы и выходы первого и второго узла являются соответственно первым-четвертым входами и первь -вторым выходами блока.

4. Устройство поп. 1, отличающееся тем, что индикатор состояния памяти содержит два элемента И и триггер причем синхронизирующий вход индикатора соединен с первым входом первого элемента И,первый запускающий вход индикатора соединен с установочным входом триггера и с первым входом второго элемента И, второй вход которого и второй вход первого элемента И соединены с вторым запускающим входом индикатора выход второго элемента И соединен с гасящим входом триггера и является вторым выходом индикатора, первым выходом которого является выход первого элемента И, третий вход которого соединен с выходом триггера.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 583478, кл. G 06 F 3/04, 1978.

2.Байцер Б. (Архитектура вычислительных комплексов. 1974, Ми1, Т.1, с. 159.

3. Патент Великобритании №1487706 кл. G 4 А, 1978 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения | 1983 |

|

SU1104498A1 |

| Устройство для обработки выражений языков программирования | 1981 |

|

SU1016790A1 |

| Устройство для вывода информации на дисплей | 1980 |

|

SU920696A1 |

| Устройство для управления сопрограммами | 1983 |

|

SU1144110A1 |

| Устройство для управления параллельным выполнением команд в электронной вычислительной машине | 1982 |

|

SU1078429A1 |

| Устройство для сопряжения источника и приемника информации | 1986 |

|

SU1401471A1 |

| Устройство управления обращением к подпрограммам | 1984 |

|

SU1273929A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство для сопряжения источника и приемника информации | 1988 |

|

SU1562921A1 |

| Устройство для ввода информации | 1985 |

|

SU1251091A1 |

6no82

устройс пваП П П П П П П

П

П

П

л

1ГП

у

ду

П

1

П

П

П

гб

Фиг. 7

Авторы

Даты

1981-08-23—Публикация

1979-12-14—Подача