функции от режима работы, задаваемого

В блоке 13,памяти двунаправленные 15 блоком 1 сигналами в линиях 29, 30 и выходы блоков 44-46 образуют внутреннюю двунаправленную магистраль. При записи информации в блок 13 памяти по линии 47 на управляющие входы запоминающего устройства 44 и приемника 45 поступает сигнал, подготавливающий схему к записи информации с линий 48, которая через приемник 45 поступает во внутреннюю магистраль.

26. Для минимизации, аппаратных затрат блок I6 выполнен на программируемом ПЗУ, которое должно хранить карты распеределения памяти для случая 20 эмуляции ПЗУ отлаживаемой микропроцессорной системы и во время записи информации в первой 12 и второй 13 . блоки памяти. Сигнал линии 60 вырабатывается во время эмуляции ПЗУ при

26. Для минимизации, аппаратных затрат блок I6 выполнен на программируемом ПЗУ, которое должно хранить карты распеределения памяти для случая 20 эмуляции ПЗУ отлаживаемой микропроцессорной системы и во время записи информации в первой 12 и второй 13 . блоки памяти. Сигнал линии 60 вырабатывается во время эмуляции ПЗУ при

При подаче сигнала 49 происходит за- 25 вьщачес входа 1 4 адреса, -принадлежащепись информации в запоминающее устройство 44 по адресу, поступающему по линиям 50. Запись производится словами по четыре бита. При считьгааго области ПЗУ. Кроме того, дешифратор 16 вырабатывает сигнал в линии 69, поступающий на элемент ИЛИ 17. Он выдается при эмуляции ПЗУ, если

го области ПЗУ. Кроме того, дешифратор 16 вырабатывает сигнал в линии 69, поступающий на элемент ИЛИ 17. Он выдается при эмуляции ПЗУ, если

НИИ информации адрес ячейки также за- зо адрес выборки команды не совпадает дается кодом, поступающим по линиям с областью эмулиру1с)щего ОЗУ.

50. По приходу сигнала 48 считывания информация поступает во внутреннюю магистраль. По старщим разрядам ад- .реса 51, поступающим на адресный вход мультиплексора 46, производится выбор одного бита, который передается в блок 2 останова по линии 40.

35

Триггеры 18 и 19 представляют собой I-K и D-триггеры соответственно. Триггер 18 взводится сигналом 61 блока 5 управления памятью, а триггер 19 срабатывает по сигналу с синхронизирующего Лсода 8 устройства, поступающего при операциях со стеком, при наличии активного уровня сигнала на поступлении сигнала по линии 59 в за- о выходы схемы 5 сравнения. Сброс триг- висимости от сигнала в линии 60 про- . . геров 18 и 9 происходит по сигналу в

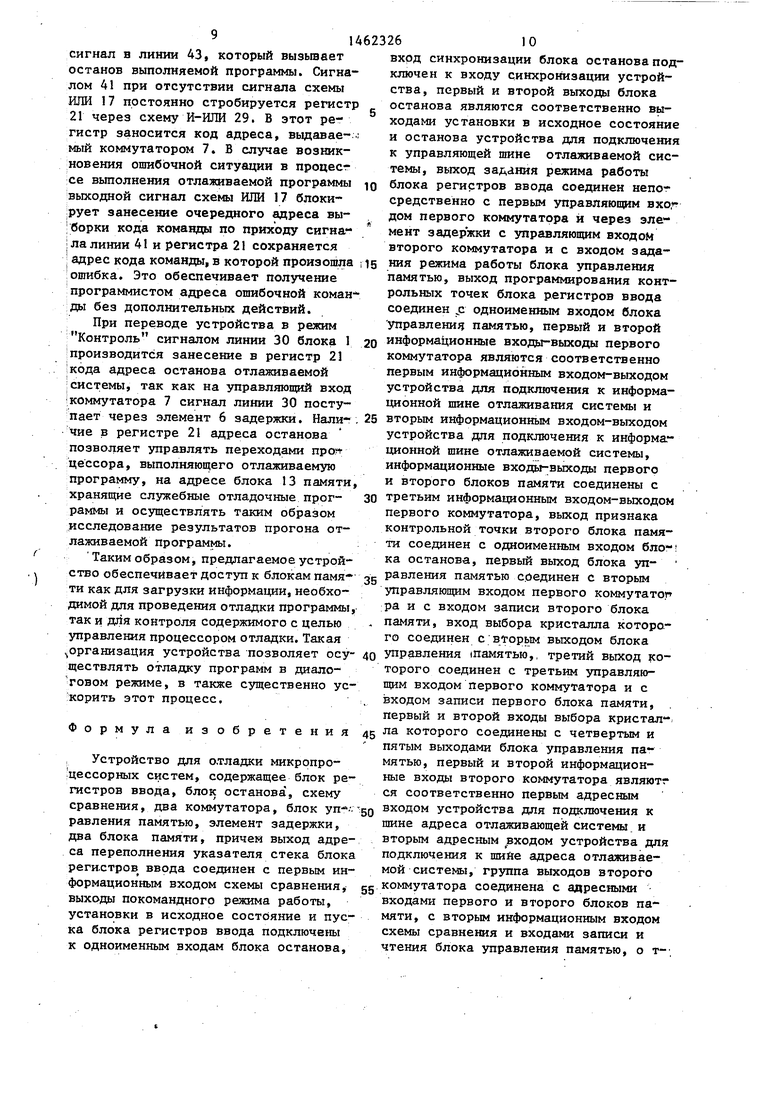

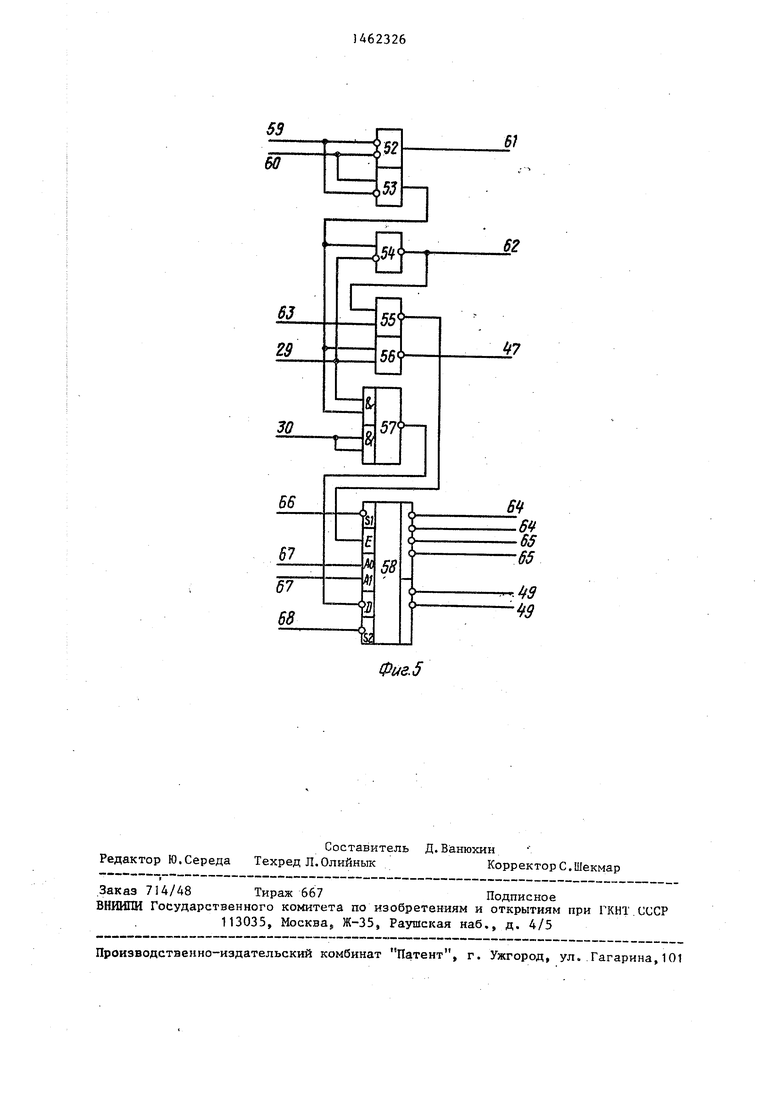

В блоке 5 управления памятью при

исходит либо выдача сигнала в линию 61 с выхода элемента И 52, либо с выхода элемента И 53 на первые входы элементов И-НЕ .54 и 56 и элемента 2И-ИЛИ-НЕ 57. Далее, если, сигнал в линии 29 имеет низкий уровень, то элемент И 54 выдает сигнал в линию 62, а в противном случае выдается сигнал в линию 47. Выходной сигнал элемента И 54 поступает на вход элемента И 55, который вырабатьшает сигнал разрешения работы дешифратора 58. Элемент 57 вырабатьтает разрешающий

линии 42.,

Схема И-ИЛИ 20 выполнена на микросхемах К555ЛР11, причем сигнал ли- g НИИ 30 поступает на входы И, а сигна- лы с синхронизирующего входа и выхода элемента ИЛИ I7 подаются на вторые два входа И.

Устройство работает в двух режимах: Эмуляция и Контроль.

В режиме Эмуляция может осуществляться выполнение команд отлаживаемых программ либо с максимальной скоростью работы процессора отлажива50

сигнал для второй половины дешифрато- емой системы, либо покомандно. В ре ра 58. При наличии единичного сигна- .т ,г,„„„™„,

жиме Эмуляция осуществляется контроль работы отлаживаемой программы: проверяются адреса, к которым происходит обращение при выборке кодов ко

ла в линию 30 разрешающий сигнал с выхода элемента 57 вьздается постоянно. Элемент И 55 вьщает сигнал также

блоком 1 сигналами в линиях 29, 30 и

26. Для минимизации, аппаратных затрат блок I6 выполнен на программируемом ПЗУ, которое должно хранить карты распеределения памяти для случая эмуляции ПЗУ отлаживаемой микропроцессорной системы и во время записи информации в первой 12 и второй 13 . блоки памяти. Сигнал линии 60 вырабатывается во время эмуляции ПЗУ при

вьщачес входа 1 4 адреса, -принадлежащего области ПЗУ. Кроме того, дешифратор 16 вырабатывает сигнал в линии 69, поступающий на элемент ИЛИ 17. Он выдается при эмуляции ПЗУ, если

адрес выборки команды не совпадает с областью эмулиру1с)щего ОЗУ.

линии 42.,

Схема И-ИЛИ 20 выполнена на микросхемах К555ЛР11, причем сигнал ли- g НИИ 30 поступает на входы И, а сигна- лы с синхронизирующего входа и выхода элемента ИЛИ I7 подаются на вторые два входа И.

Устройство работает в двух режимах: Эмуляция и Контроль.

В режиме Эмуляция может осуществляться выполнение команд отлаживаемых программ либо с максимальной скоростью работы процессора отлажива50

емой системы, либо покомандно. В ре .т ,г,„„„™„,

жиме Эмуляция осуществляется контроль работы отлаживаемой программы: проверяются адреса, к которым происходит обращение при выборке кодов ко14623266

адреса с учетом состояния сигналов линий 29 и 30 вырабатывает сигналы 66-68, причем в линиях 66 и 67 уровни сигналов активны, а сигнал в линии 68 пассивен. Уровень сигнала линии 60 имеет значение так как в режиме Контроль может производиться запись в область эмулирующего ОЗУ блока 12 памяти. При поступлении с коммутатора 7 активного сигнала линии 59 схема И 53 вырабатывает сигнал, который вызывает формирование схемой И-НЕ 54 активного уровня сиг10

манд; контролируются выполняемые

щиклы записи данных и блокируются поПытки записи в область .эмулирующего

ОЗУ; контролируется глубина стека в

Процессе работы программ; в случае

достижения программой одного из заданных адресов (контрольная точка)

выдается сигнал останова. .

I В случае возникновения ошибок или

1ри достижении контрольной точки в

регистр 21 заносится адрес команды,

1ри выполнении которой возникла ошиб-

ка. В режиме Контроль осуществляет1ся доступ к блоку 12 памяти для запи- 15 нала в линии 62, который переводит

СИ/считывания, запись контрольных то- ОЗУ блока 12 в режим записи информации. Одновременно сигнал схемы И-НЕ 54 поступает на вход схемы И-НЕ 55, которая вырабатывает стробирующий 20 сигнал, поступающий на дешифратор 58, разрешая выдачу одного из сигналов выборки в линиях 64. При поступлении этих сигналов в блок 12 памяти происходит запись информации. В случае 25 считывания информации из блока 12 памяти с коммутатора 7 по линии 63 поступает на схему 55 сигнал для выработки строба, разрешающего работу дешифратора 58, который формирует сигкирует работу схемы 57 по вторым вхо- ЗО нал в одной из линий 64. При поступдам и переключает первый и второй ком- лении этих сигналов в блок 12 памяти

происходит считьшание информации из выбранного банка. При программировании контрольных точек производится за- 2g пись информации в блок 12 памяти. При этом коды адресов и данных поступают с входов устройства 11 и 15 через коммутаторы 4 и 7, а запись происходит по приходу сигнала линии 59, 40 выдаваемого коммутатором 7.

Кроме того, должен быть переведен в единичное состояние сигнал линии 29 регистра 25 блока 1. Этот сигнал поступает в блоки 6 и 16, которые по 45 старшим разрядам адреса, поступающим с коммутатора 7, вырабатывает сигналы в линиях 60, 66-68, причем сигнал линии имеет единичное значение, разрешая работу схемы И 53, сигнал линии

чек в блок 13 памяти. Доступ к реги- jCTpy 21 может осуществляться в обоих режимах.

Устройство работает следующим об- |разом.

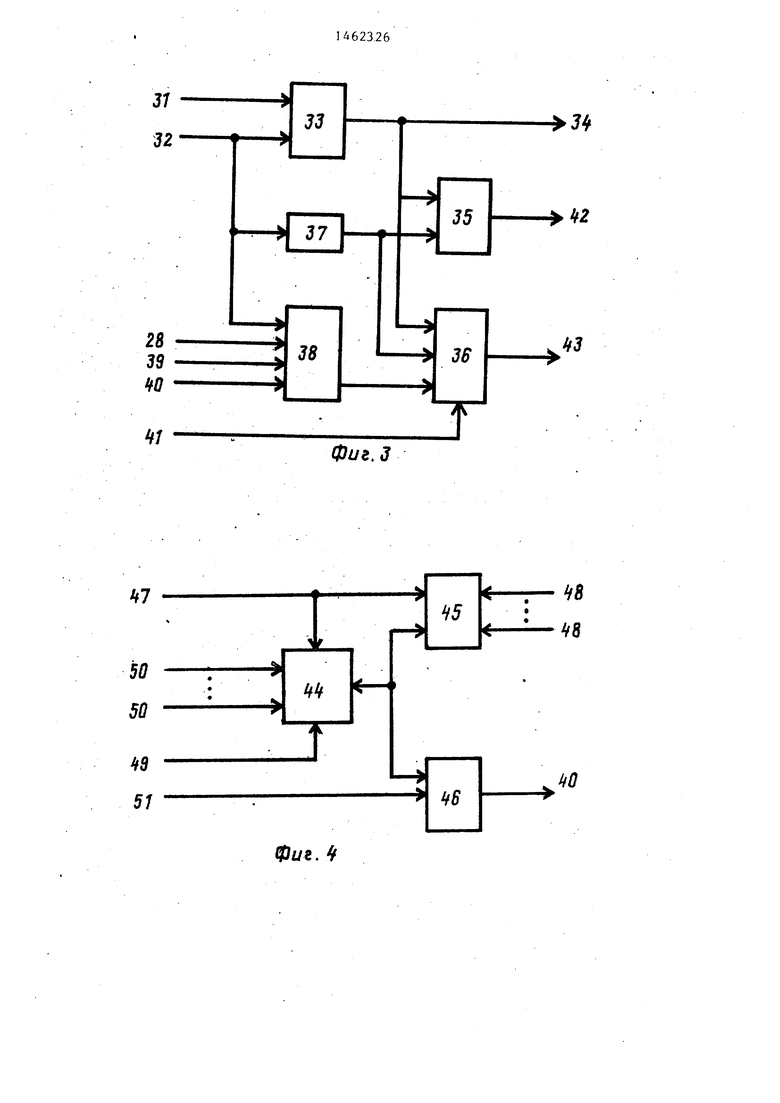

I В регистре 26 управления блока 1 (вначале набирается нулевая комбина- дйя, переводящая сигнал линий 29-32 в состояние логического нуля. При пос- :туплении сигнала 29 в блок 5 запре- щается работа логических схем 56 и 57 и разрешается работа схемы 54. Низкий уровень сигнала линии 30 бломутаторы 4 и 7 на передачу сигналов с входов 11 и 15 соответственно. Низкий уровень сигнала в линии 31 переводит триггер 33 блока 2 останова в единичное состояние. Выходной сигнал триггера 33 вызывает формирование низкого уровня сигнала схемой И 35 в линии 42, который переводит в нулевое состояние триггеры -18 и 19, а также устанавливает в нулевое состояние триггер 36, который снимает сигнал в линии 43. Наличие соответствующих уровней сигналов в линиях 34 и 43 вызьшает переход отлаживаемой системы в исходное состояние и блокирование ее работы в этом состоянии. Далее может быть произведена загрузка отлаживаемой программы в эмулирующее

| название | год | авторы | номер документа |

|---|---|---|---|

| ВНУТРИСХЕМНЫЙ ЭМУЛЯТОР | 1999 |

|

RU2214621C2 |

| Устройство для отладки микроЭВМ | 1985 |

|

SU1247877A1 |

| Устройство для отладки микроЭВМ | 1985 |

|

SU1410708A1 |

| Устройство для отладки программно-аппаратных блоков | 1984 |

|

SU1290329A1 |

| Устройство для отладки программ микроЭВМ | 1989 |

|

SU1815643A1 |

| ВНУТРИСХЕМНЫЙ ЭМУЛЯТОР | 1996 |

|

RU2110833C1 |

| МНОГОФУНКЦИОНАЛЬНОЕ ОТЛАДОЧНОЕ УСТРОЙСТВО ДЛЯ МИКРОПРОЦЕССОРНЫХ СИСТЕМ | 2016 |

|

RU2634197C1 |

| Устройство для отладки программ | 1982 |

|

SU1100627A1 |

| Устройство для отладки программ | 1988 |

|

SU1654827A1 |

| УСТРОЙСТВО ДЛЯ ПОИСКА ПЕРЕМЕЖАЮЩИХСЯ ОТКАЗОВ В МИКРОПРОЦЕССОРНЫХ СИСТЕМАХ | 1996 |

|

RU2099777C1 |

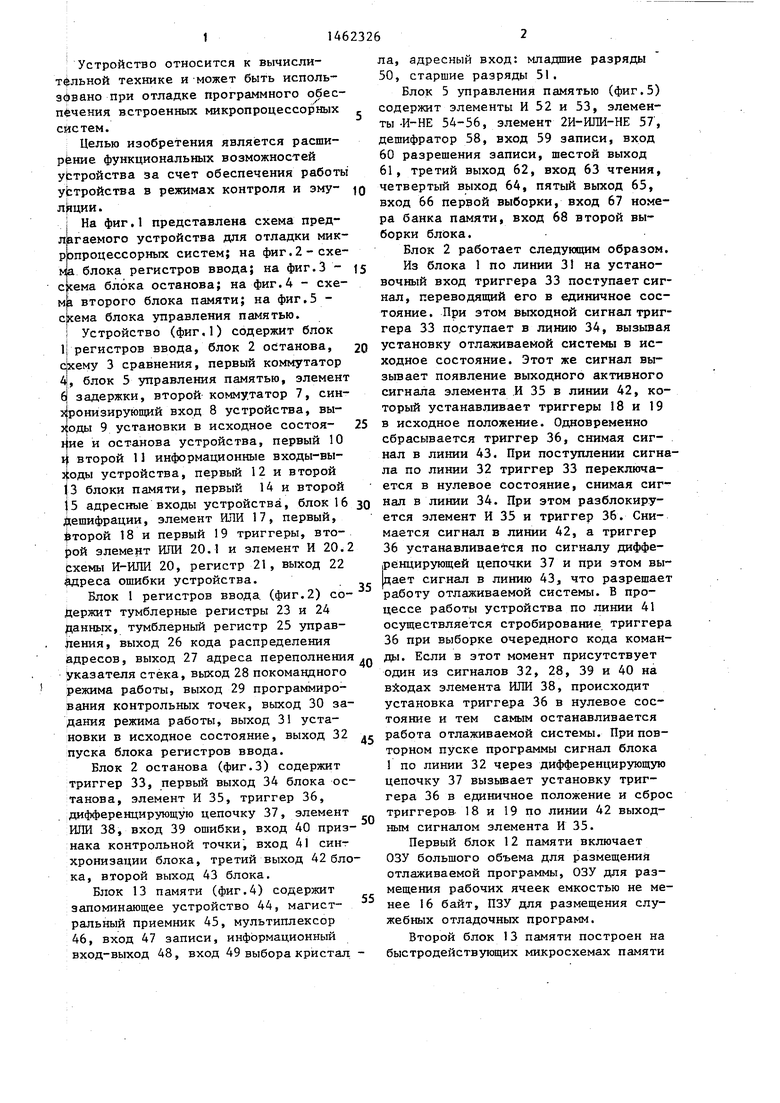

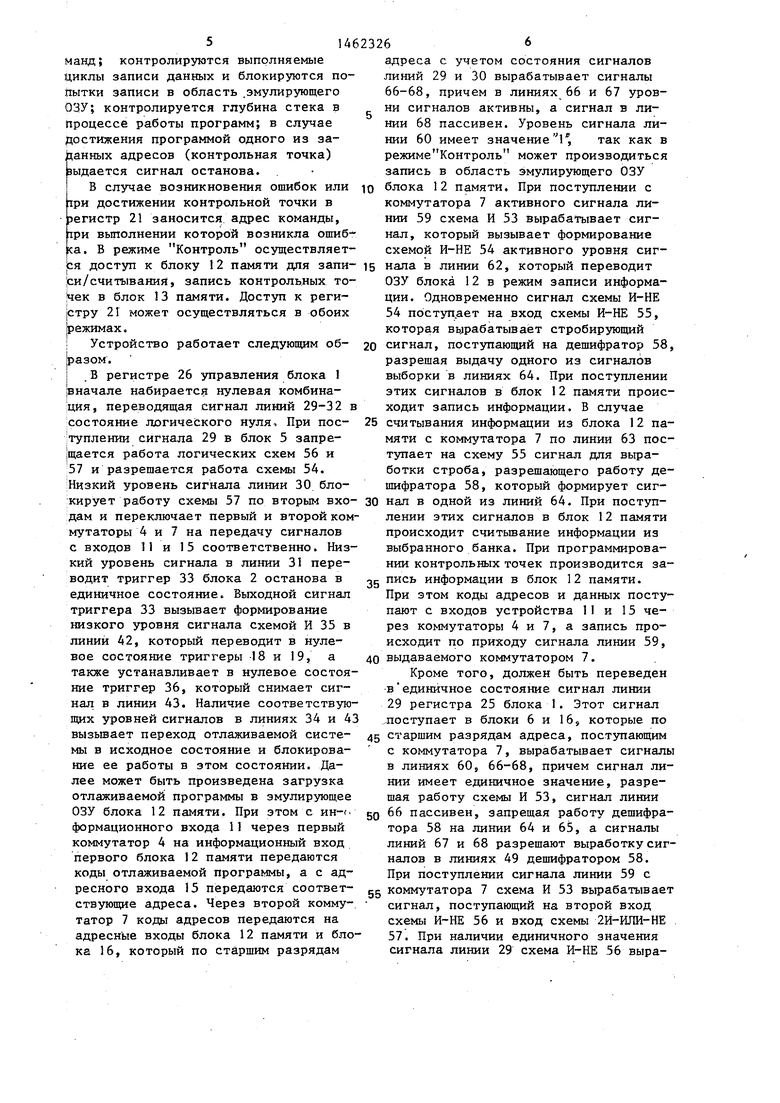

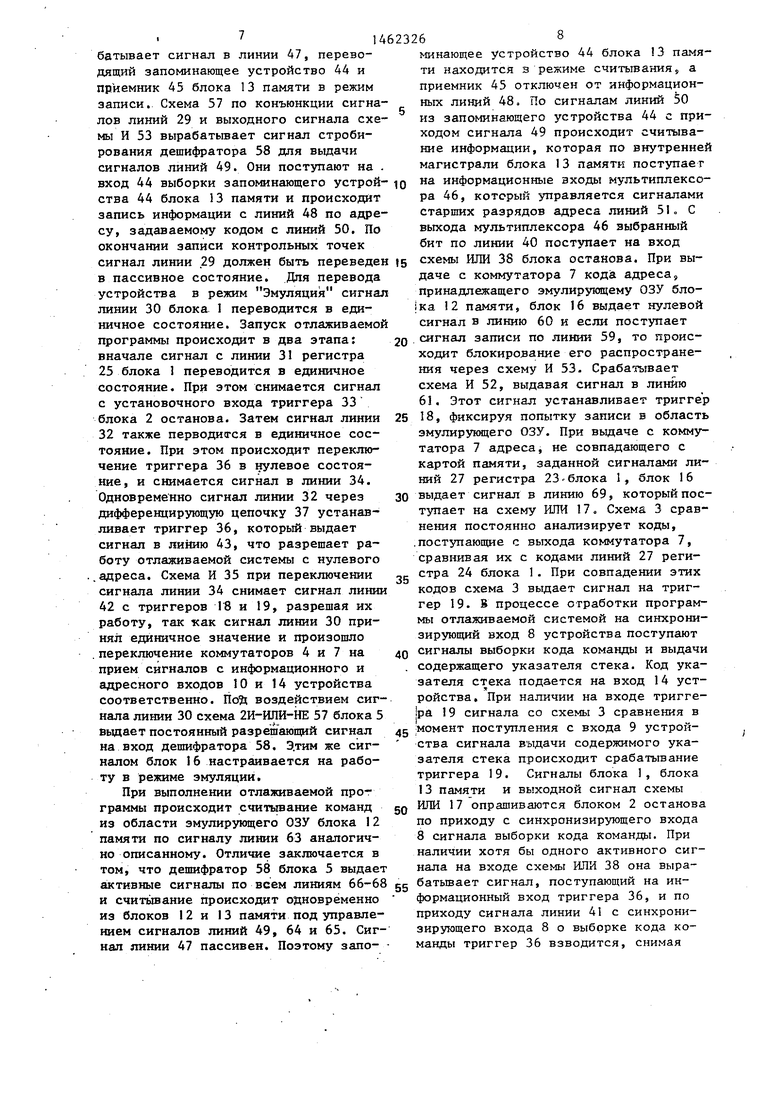

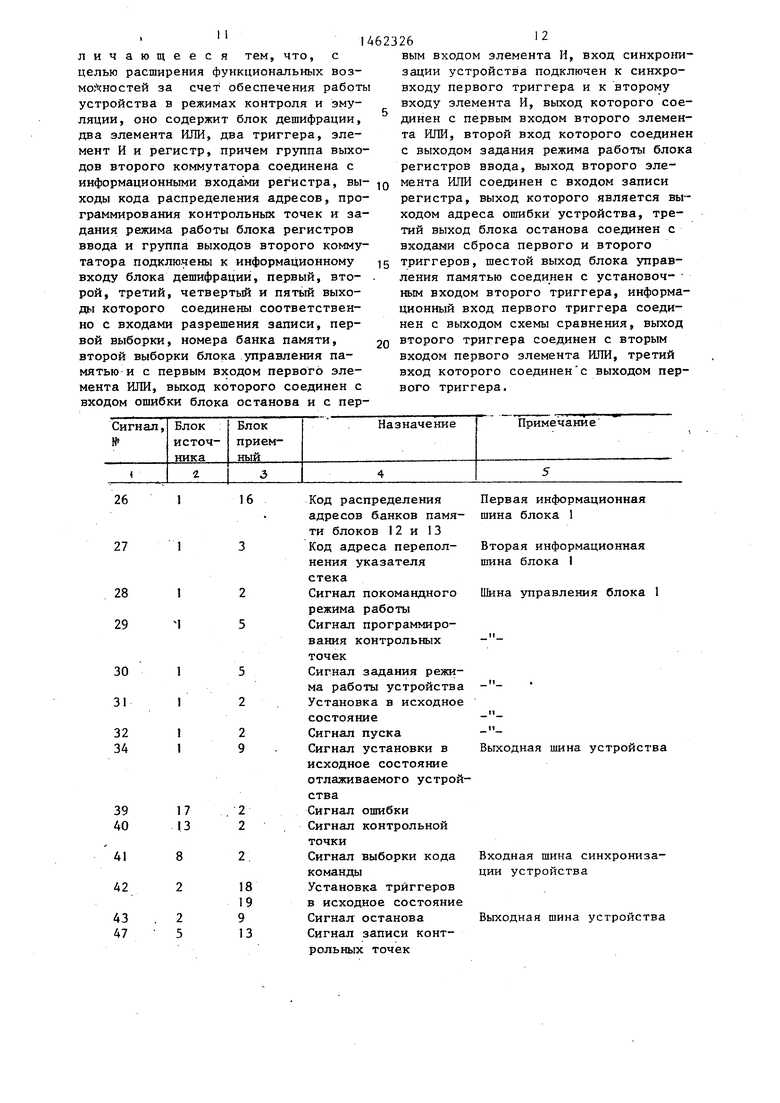

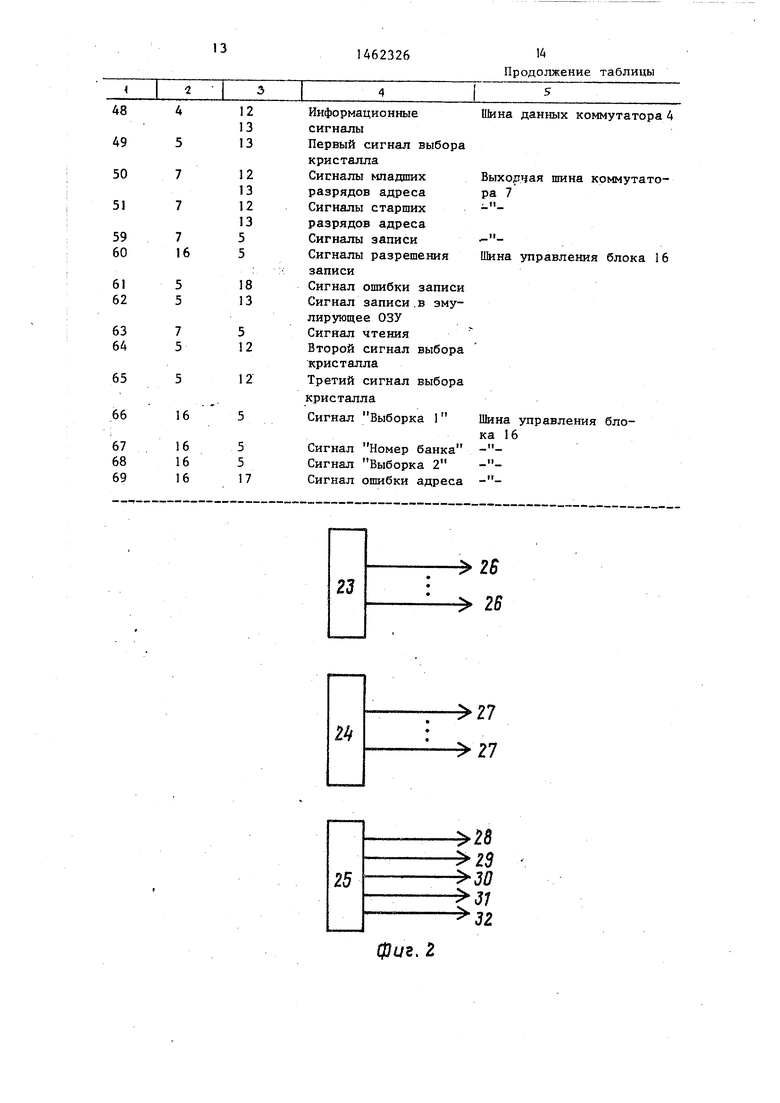

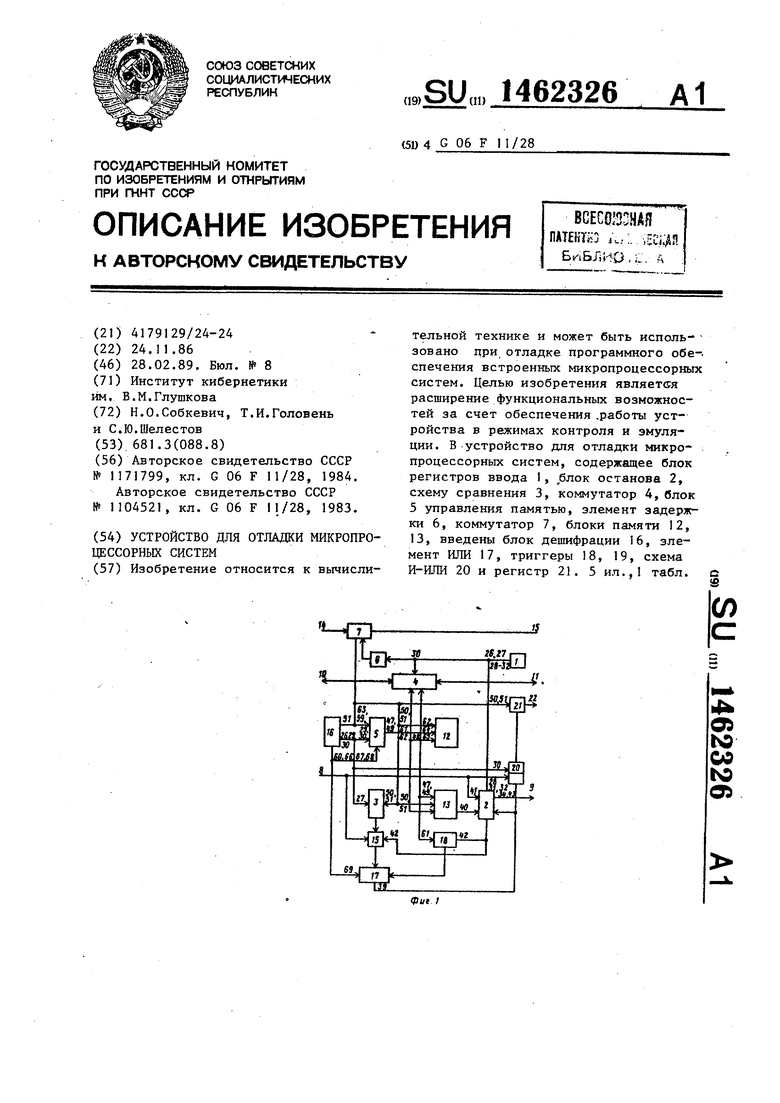

Изобретение относится к вычислительной технике и может быть исполь- - зовано при отладке программного обе-, спечения встроенных микропроцессорных систем. Целью изобретения является расширение функциональных возможностей за счет обеспечения .работы устройства в режимах контроля н эмуляции. В устройство для отладки микро- ; процессорньпс систем, содержащее блок регистров ввода 1 , блок останова 2, схему сравнения 3, коммутатор 4, блок 5 управления памятью, элемент задержки 6, коммутатор 7, блоки памяти 12, 13, введены блок дешифрации 16, элемент ИЛИ 17, триггеры 18, 19, схема И-ИЛИ 20 и регистр 21. 5 ил.,1 табл.

ОЗУ блока 12 памяти. При этом с ин-( gQ 66 пассивен, запрещая работу дешифраформационного входа 11 через первый коммутатор 4 на информационный вход первого блока 12 памяти передаются коды отлаживаемой программы, а с адресного входа 15 передаются соответствующие адреса. Через второй комму-, татор 7 коды адресов передаются на адресные входы блока 12 памяти и блока 16, который по старшим разрядам

тора 58 на линии 64 и 65, а сигналы линий 67 и 68 разрешают выработку сигналов в линиях 49 дешифратором 58. При поступлении сигнала линии 59 с 55 коммутатора 7 схема И 53 вырабатывает сигнал, поступающий на второй вход схемы И-НЕ 56 и вход схемы 2Й-ИЛИ-НЕ 57. При наличии единичного значения сигнала линии 29 схема И-НЕ 56 выратора 58 на линии 64 и 65, а сигналы линий 67 и 68 разрешают выработку сигналов в линиях 49 дешифратором 58. При поступлении сигнала линии 59 с 55 коммутатора 7 схема И 53 вырабатывает сигнал, поступающий на второй вход схемы И-НЕ 56 и вход схемы 2Й-ИЛИ-НЕ 57. При наличии единичного значения сигнала линии 29 схема И-НЕ 56 вырабатывает сигнал в линии 47, переводящий запоминающее устройство 44 и приемник 45 блока 13 памяти в режим записи. Схема 57 по конъюнкции сигналов линий 29 и выходного сигнала схемы И 53 вырабатьгоает сигнал строби- рования дешифратора 58 для выдачи сигналов линий 49. Они поступают на . вход 44 выборки запоминающего устрой- ю ства 44 блока 13 памяти и происходит запись информации с линий 48 по адресу, задаваемому кодом с линий 50. По окончании записи контрольных точек сигнал линии 29 должен быть переведен |5 в пассивное состояние. Для перевода устройства в режим Эмуляция сигнал линии 30 блока 1 переводится в единичное состояние. Запуск отлаживаемой программы происходит в два этапа; 20 вначале сигнал с линии 3 регистра 25 блока 1 переводится в единичное состояние. При этом снимается сигнал с установочного входа триггера 33 блока 2 останова. Затем сигнал линии 25 32 также перводится в единичное состояние. При этом происходит переключение триггера 36 в нулевое состояние, и снимается сигнал в линии 34. Одновременно сигнал линии 32 через 30 дифференцирующую цепочку 37 устанавливает триггер 36, который выдает сигнал в лийию 43, что разрешает работу отлаживаемой системы с нулевого адреса. Схема И 35 при переключении gg сигнала линии 34 снимает сигнал линии 42 с триггеров IB и 19, разрешая их работу, так как сигнал линии 30 принял единичное значение и произошло .переключение коммутаторов 4 и 7 на 40 прием сигналов с информационного и адресного входов 10 и 14 устройства соответственно. Пой воздействием сигнала линии 30 схема 2И-Ш1И-НЕ 57 блока 5 вьщает постоянный разреш ающий сигнал 45 на вход дешифратора 58. Э.тим же сигналом блок 16 настраивается на работу в режиме эмуляции.

При выполнении отлаживаемой программы происходит считьшание команд 50 из области эмулирующего ОЗУ блока 12 памяти по сигналу линии 63 аналогично описанному. Отличие заключается в том, что дешифратор 58 блока 5 выдает

минающее устройство 44 блока 13 памя ти находится 3 режиме считывания, а приемник 45 отключен от информационных линий 48. По сигналам линий 50 из запоминающего устройства 44 с при ходом сигнала 49 происходит считывание информации, которая по внутренне магистрали блока 13 памяти поступает на информационные входы мультиплексо ра 46, который управляется сигналами старших разрядов адреса линий 5 К С выхода мультиплексора 46 выбранный бит по линии 40 поступает на вход схемы ИЛИ 38 блока останова. При выдаче с коммутатора 7 кода адреса, принадлежащего эмулирующему ОЗУ бло- |ка 2 памяти, блок 16 выдает нулевой сигнал в линию 60 и если поступает сигнал записи по линии 59, то происходит блокирование его распространения через схему И 53. Срабатывает схема И 52, выдавая сигнал в линию 61. Этот сигнал устанавливает тригге 18, фиксируя попытку записи в област эмулирующего ОЗУ. При вьщаче с комму татора 7 адреса, не совпадающего с картой памяти, заданной сигналами ли ний 27 регистра 23-блока 1, блок 16 выдает сигнал в линию 69, который пос тупает на схему ИЛИ 17. Схема 3 срав нения постоянно анализирует коды, .поступающие с выхода коммутатора 7, сравнивая их с кодами линий 27 регистра 24 блока 1. При совпадении этих кодов схема 3 вьщает сигнал на триггер 19. В процессе отработки программы отлаживаемой системой на синхронизирующий вход 8 устройства поступают сигналы выборки кода команды и выдачи содержащего указателя стека. Код указателя стека подается на вход 14 устройства. При наличии на входе тригге- ра 19 сигнала со схемы 3 сравнения в момент поступления с входа 9 устройства сигнала выдачи содержимого указателя стека происходит срабатывание триггера 19. Сигналы блока 1, блока 13 памяти и выходной сигнал схемы ИЛИ 17 опрашиваются блоком 2 останова по приходу с синхронизирующего входа 8 сигнала выборки кода команды. При наличии хотя бы одного активного сигнала на входе схемы ИЛИ 38 она выраактивные сигналы по всем линиям 66-68 55 батьшает сигнал, поступающий на ин- и считывание происходит одновременно формационный вход триггера 36, и по из блоков 12 и 13 памяти под управле- приходу сигнала линии 41 с синхрони- нием сигналов линий 49, 64 и 65. Сиг- зирующего входа 8 о выборке кода ко- нал линии 47 пассивен. Поэтому запо- - манды триггер 36 взводится, снимая

минающее устройство 44 блока 13 памяти находится 3 режиме считывания, а приемник 45 отключен от информационных линий 48. По сигналам линий 50 из запоминающего устройства 44 с приходом сигнала 49 происходит считывание информации, которая по внутренне магистрали блока 13 памяти поступает на информационные входы мультиплексора 46, который управляется сигналами старших разрядов адреса линий 5 К С выхода мультиплексора 46 выбранный бит по линии 40 поступает на вход схемы ИЛИ 38 блока останова. При выдаче с коммутатора 7 кода адреса, принадлежащего эмулирующему ОЗУ бло- |ка 2 памяти, блок 16 выдает нулевой сигнал в линию 60 и если поступает сигнал записи по линии 59, то происходит блокирование его распространения через схему И 53. Срабатывает схема И 52, выдавая сигнал в линию 61. Этот сигнал устанавливает триггер 18, фиксируя попытку записи в область эмулирующего ОЗУ. При вьщаче с коммутатора 7 адреса, не совпадающего с картой памяти, заданной сигналами линий 27 регистра 23-блока 1, блок 16 выдает сигнал в линию 69, который поступает на схему ИЛИ 17. Схема 3 сравнения постоянно анализирует коды, .поступающие с выхода коммутатора 7, сравнивая их с кодами линий 27 регистра 24 блока 1. При совпадении этих кодов схема 3 вьщает сигнал на триггер 19. В процессе отработки программы отлаживаемой системой на синхронизирующий вход 8 устройства поступают сигналы выборки кода команды и выдачи содержащего указателя стека. Код указателя стека подается на вход 14 устройства. При наличии на входе тригге- ра 19 сигнала со схемы 3 сравнения в момент поступления с входа 9 устройства сигнала выдачи содержимого указателя стека происходит срабатывание триггера 19. Сигналы блока 1, блока 13 памяти и выходной сигнал схемы ИЛИ 17 опрашиваются блоком 2 останова по приходу с синхронизирующего входа 8 сигнала выборки кода команды. При наличии хотя бы одного активного сигнала на входе схемы ИЛИ 38 она вырасигнал в линии 43, который вызьшает останов выполняемой программы. Сигналом 41 при отсутствии сигнала схемы ИЛИ 17 постоянно стробируется регистр 21 через схему И-ИЛИ 29. В этот регистр заносится код адреса, вьщавае- .; мый коммутатором 7. В случае возникновения ошибочной ситуации в процесг- се выполнения отлаживаемой программы выходной сигнал схемы ИЛИ 17 блоки- :рует занесение очередного адреса вы- |борки кода команды по приходу сигна- ла линии 41 и регистра 21 сохраняется I адрес кода команды, в которой произошла ;ошибка. Это обеспечивает получение программистом адреса ошибочной коман- ды без дополнительных действий. При переводе устройства в режим

1462326

10

вход синхронизации блока останова подключен к входу синхронизации устройства, первый и второй выходы блока останова являются соответственно выходами установки в исходное состояние и останова устройства для подключения к управляющей шине отлаживаемой системы, выход задания режима работы

10 блока регистров ввода соединен непог средственно с первым управляющим вхог

. дом первого коммутатора и через элемент задержки с управляющим входом второго коммутатора и с входом зада15 ния режима работы блока управления памятью, выход программирования контрольных точек блока регистров ввода соединен .с одноименным входом блока управления памятью, первый и второй

- -.7 л-

Контроль сигналом линии 30 блока 1 20 информационные входы-выходы первого

:производится занесение в регистр 21 ;кода адреса останова отлаживаемой :системы, так как на управляющий вход : коммутатора 7 сигнал линии 30 постукоммутатора являются соответственно первым информационным входом-выходом устройства для подключения к информационной шине отлаживания системы и

пает через элемент 6 задержки. Нали-. 25 вторым информационным входом-выходом

чие в регистре 21 адреса останова позволяет управлять переходами проп цессора, выполняющего отлаживаемую программу, на адресе блока 13 памяти, хранящие служебные отладочные программы и осуществлять таким образом исследование результатов прогона отлаживаемой программы.

Таким образом, предлагаемое устройустройства для подключения к информационной шине отлаживаемой системы, информационные входы-выходы первого и второго блоков памяти соединены с 30 третьим информационным входом-выходом первого коммутатора, выход признака контрольной точки второго блока памяти соединен с одноименным входом бло- . . ка останова, первый выход блока уп- ство обеспечивает доступ к блокам памя- 35 Р ления памятью соединен с вторым ти как для загрузки информации, необхо- управляющим входом первого коммутатоп ДИМОЙ для проведения отладки программы, ра. и с входом записи второго блока так и для контроля содержимого с целью . памяти, вход выбора кристалла которо- управления процессором отладки. Такая го соединен с вторьм вьпсодом блока организация устройства позволяет осу- 40 управления (памятью,, третий выход ко- „ торого соединен с третьим управляющим входом первого коммутатора и с , входом записи первого блока памяти,

первый и второй входы выбора кристал-. 45 ла которого соединены с четвертым и пятым выходами блока управления памятью, первый и второй информационные входы второго коммутатора являютг

ществлять отладку программ в диало- товом режиме, в также существенно ус- -корить этот процесс.

Ф о

рмула изобретения

Устройство для о.тладки микропроцессорных систем, содержащее блок регистров ввода, блок останова , схему сравнения, два коммутатора, блок равления памятью, элемент задержки, два блока памяти, причем выход адреса переполнения указателя стека блока

ся соответственно первым адресным igg входом устройства для подключения к шине адреса отлаживающей системы и вторым адресным входом устройства для подключения к шийе адреса отлаживаемой системы, rpjTina выходов второго

ся соответственно первым адресным igg входом устройства для подключения к шине адреса отлаживающей системы и вторым адресным входом устройства для подключения к шийе адреса отлаживаемой системы, rpjTina выходов второго

реги.стров ввода соединен с первым ин-, .

формационным входом схемы сравнения, коимут& ора соединена с адресными выходы покомандного режима работы, входами первого и второго блоков па- установки в исходное состояние и пус- мяти, с вторым информационным входом ка блока регистров ввода подключены схемы сравнения и входами записи и к одноименньм входам блока останова, чтения блока управления памятью, о т10

вход синхронизации блока останова подключен к входу синхронизации устройства, первый и второй выходы блока останова являются соответственно выходами установки в исходное состояние и останова устройства для подключения к управляющей шине отлаживаемой системы, выход задания режима работы

блока регистров ввода соединен непог средственно с первым управляющим вхог

дом первого коммутатора и через элемент задержки с управляющим входом второго коммутатора и с входом задания режима работы блока управления памятью, выход программирования контрольных точек блока регистров ввода соединен .с одноименным входом блока управления памятью, первый и второй

- -.7 л-

информационные входы-выходы первого

информационные входы-выходы первого

коммутатора являются соответственно первым информационным входом-выходом устройства для подключения к информационной шине отлаживания системы и

вторым информационным входом-выходом

ся соответственно первым адресным igg входом устройства для подключения к шине адреса отлаживающей системы и вторым адресным входом устройства для подключения к шийе адреса отлаживаемой системы, rpjTina выходов второго

, .

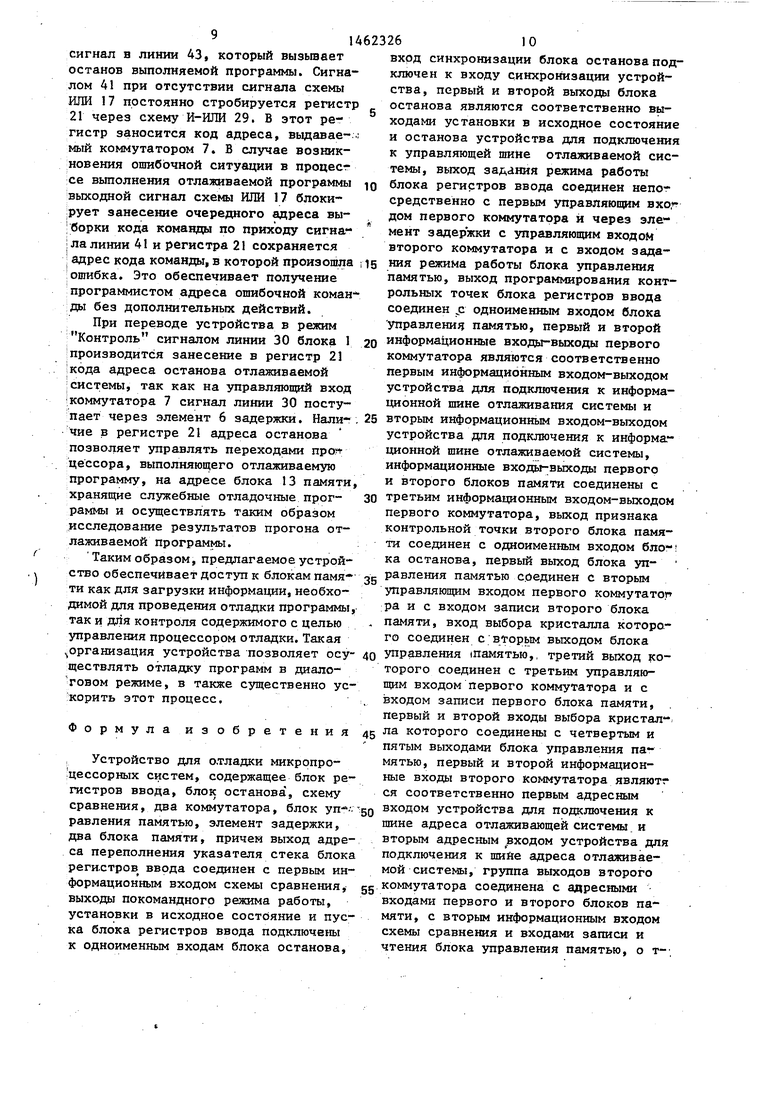

коимут& ора соединена с адресными входами первого и второго блоков па- мяти, с вторым информационным входом схемы сравнения и входами записи и чтения блока управления памятью, о тличающееся тем, что, с целью расширения функциональных воз- моЛностей за счет обеспечения работы устройства в режимах контроля и эмуляции, оно содержит блок дешифрации, два элемента ИЛИ, два триггера, элемент И и регистр, причем группа выходов второго коммутатора соединена с информационными входами регистра, вы- ходы кода распределения адресов, программирования контрольных точек и задания режима работы блока регистров ввода и группа выходов второго коммутатора подключены к информационному входу блока дешифрации, первый, второй, третий, четвертый и пятый выходы которого соединены соответственно с входами разрешения записи, первой выборки, номера банка памяти, второй выборки блока управления памятью и с первым входом первого элемента ШШ, выход которого соединен с входом ошибки блока останова и с пер

17 13

8 2

2 5

16 Код распределения

адресов банков памяти блоков 1 2 и 13

3 Код адреса переполнения указателя стека

2 Сигнал покомандного режима работы

5 Сигнал программирования контрольных точек

5 Сигнал задания режима работы устройства

2 Сигнал пуска

9 Сигнал установки в исходное состояние отлаживаемого устройства

2 Сигнал ошибки

2 Сигнал контрольной точки

18Установка триггеров

19в исходное состояние 9 Сигнал останова

1 3 Сигнал записи контрольных точек

мента

вым входом элемента И, вход синхро1т- зации устройства подключен к синхро- входу первого триггера и к второму входу элемента И, выход которого соединен с первым входом второго элемента ИЛИ, второй вход которого соединен с выходом задания режима работы блока регистров ввода, выход второго элеИЛИ соединен с входом записи регистра, выход которого является выходом адреса ошибки устройства, третий выход блока останова соединен с входами сброса первого и второго триггеров, шестой выход блока управления памятью соединен с установоч- ным входом второго триггера, информационный вход первого триггера соединен с выходом схемы сравнения, выход второго триггера соединен с вторым входом первого элемента ИЛИ, третий вход которого соединен с выходом первого триггера.

Первая информационная шина блока 1

Вторая информационная шина блока 1

Шина управления блока

Выходная шина устройства

Входная шина синхронизации устройства

Выходная шина устройства

13

U62326

lA Продолжение таблицы

фи. Z

Фиг. ff

Фиг. 5

| Устройство для прерывания при отладке программ | 1984 |

|

SU1171799A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для отладки программ | 1983 |

|

SU1104521A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-02-28—Публикация

1986-11-24—Подача