«

Изобретение относится к области автоматики и вычислительной техники и мол-гет найти применение, в частности, я гибридных вычислительных машинах и системах.

Известно цифроаналоговое множительное устройство, содержащее клгочи, элементы памяти, компаратор, генераторы тактовых и синхронизирующих импульсов, реверсивный счетчик и цифроаналоговый преобразователь.

Недостатками устройства являются пониженные быстродействие и точность у: ;ножения сомнолсителей, представленных в кодовой форме.

Прототипом изобретения является ди фроаналоговое млояоттельное устройство, содержап;ее два регистра, Вопсод лервого из которых соединен с цифровьм входом преобразователя кодток, подк,гяоченного аналоговым входом к выходу источника опорного напряжения, а выходом - к входу первого пробразователя ток-напря:кение5 соединенного выходом с аналоговым входом второго преобразователя код-ток, подключенного цифровым входом к выходу второго регистра, а выходом к входу второго преобразователя токнш1ря5 ;е:-гие, выход которого является выходом устройства, а входы регистров соединены с шинами ввода кодов сомножителей.

Недостатком прототипа является пониженная точность зтчножения при изменении значений кодов сомнож1-1телей в широком динамическом диапазоне .

Целью изобретения является повышение точности умножения в ип-гроком диапазоне изменения значен1-1и ссмиош-; те л ей.

Указанная цель достигается тем, что }3 цифройналоговое; мнозкительное устройство, содержащее два регистра выход первого из которых соединен с цифровьм входом первого преобразователя код-ток, подключенного аналоговым входом.к выходу источника опорного напряжения; а выходом к входупервого преобразователя ток-напряжение, соединенного выходом с анэлоговьм входом второго преобразователя код-ток, подключенного цифровьм входом к ВЫХОДУ второго регистра, а выходом - к входу второго преобразователя ток-напряжение, выход которого является выходом устройства,дополнительно введены ком утат,;р.блок

50502

сравнения, линии задержки, генератор тактовых импульсов и третий и четвертый регистры соединенные информационными входами с шинами ввода кодов

соответствующих сомножителей, а управляющими входами - с выходом генератора тактовых импульсов, причем выход третьего регистра подключен к первому информационному входу блока

0 сравнения и через первую линию задержки к первому информационному вхор,у коммутатора, соединенного первым и вторым выходами с входами первого и второго регистров Соответственно,

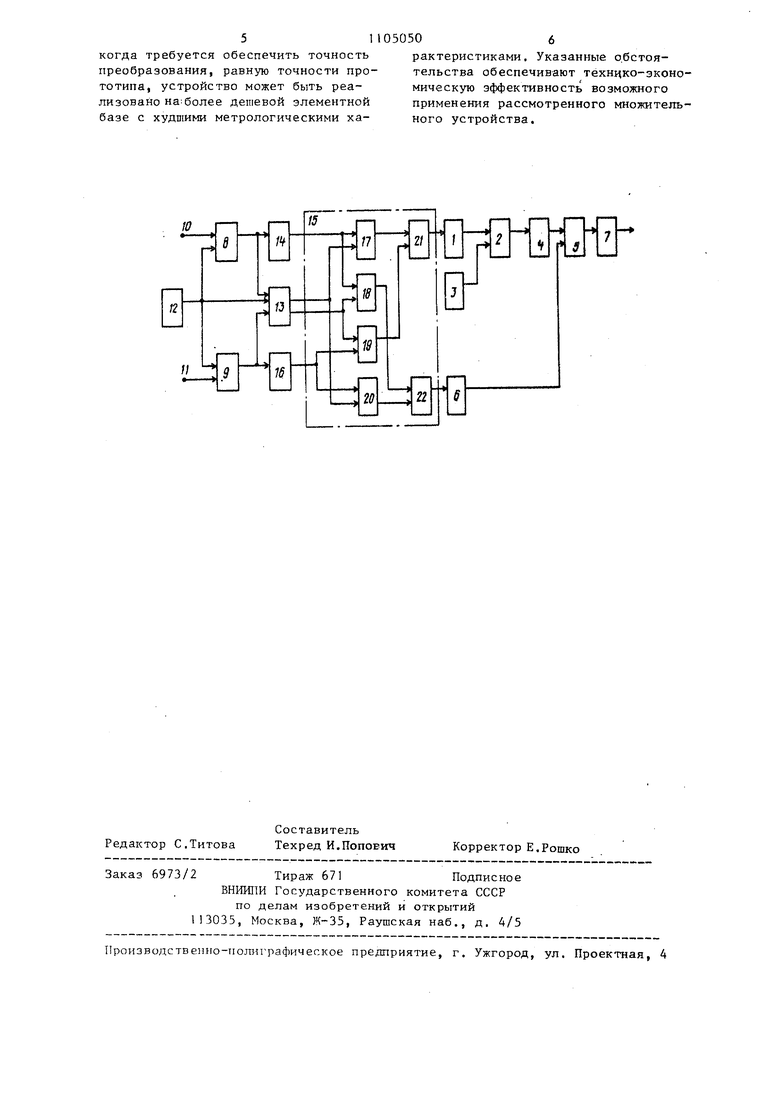

S управляющими входами - с прямым и инверсным выходами блока сравнения, а вторым информационньм входом - с выходом второй линии задержки, подключенной входом к вьгходу четвер.то0 го регистра и к второму информационному входу блока сравнения, соединернюго стробируюи им входом с выходом генератора тактовых импульсов. На чертеже изображена струк-турная

5 схема цифроаналогового множительного устройства.

Первый регистр 1 соединен выходом с цифровым входом первого преобразователя 2 код-ток, подключечтно30 О аналоговьп входом к выходу источника 3 опорного напряжения, а выходом - к входу первого преобразователя 4 ток-напряжение. Выход преобразователя 4 соединен о аналоговьм

3 входом второго преобразователя 5

код-ток, подключенного цифровые входом к выходу второго регистра б, а выходом - к входу второго преобразователя 7 ток-напряжение3 выход которого является выходом устройства„

Третий и четвертый регистры 8 и 9, соединеигл информационньмг входа.ми с ишнами IО и 11 ввода кодов соответствуюи ;их со пгожителей, а управляющими входами - с выходом генератора 12 тактовых импульсов. Выход третьего регистра 8 подключен к первому информационному входу блока 13.сравнения и через первую линию 14 задержки - к первому информационному входу ко мутатора 15. Коммутатор соединен первьи к вторым выходами с входами первого и второго регистров 1 и 6 соответственно, зттравляюП1ИМИ сходами - с. прямым и инверсным вьжодами блока 13 сравнения, а вторым информационным входом - с выходом второй линии 16 задержки. Линия задержки подключена входом к выходу четвертого регистра 9 и к второму информационному входу блока 13 сравнения, соединенного стробирующим вхо дом с выходом генератора 12. Коммутатор 15 выполнен на четырех группах 17, 18, 19-и 20 элементов И и двух группах 21 и 22 элементов ИЛИ, Устройство работает следующим образом. Коды множимого Nj и множителя N поступают в устройство по пшнам 10 и 11 на входы регистров 8 и 9 соответственно. Затем импульсами с генератора 12 тактовых импульсов коды из регистров 8 и 9 продвигаются в блок 13 сравнения поразрядно, начиная со старших разрядов, Блок 13 сравнения сравнивает коды потактно по мере их поступления на входы. Одновременно коды поступают на входы линий 14 и 16 задержки. Сигналы с выходов блока 13 сравнения управляют работой коммутатора 15 таким образом, что реали зуется следующий алгоритм работы уст ройства: больщий по величине из сомножителей направляется по тракту с меньшей погрешностью преобразования Перед началом продвижения кодов сомножителей блок 13 сравнения находится в исходном состоянии. Если ко- ды сомножителей одинаковы, состояние блока 13 сравнения не изменится. Поэтому .рассмотрим работу устройства в случае неравенства кодов, 1,и N.Состояние блока 13 срав негшя не изменится и сомножители пройдут преобразование по следующим трактам: код N-.- линия 14 задержки группа 17 элементов И и группа-21 элементов ИЛИ, регистр 1, преобразов тель 2 код-ток, преобразователь 4 ток-напряжение, преобразователь 5 код-ток и через преобразователь 7 ток-напряжение на вьпсод устройства, код N - линия 16 задержки, группа 20 элементов И и группа 22 элементов ИЛИ, регистр 6, преобразователь 5 код-ток и через преобразователь 7 ток-напряжение на выход устройства, 2,W,N, Блок 13 сравнения переходит в возбужденное состояние и перевслючает пути прохождения сомножителей в коммутаторе 15 на противоположные: Jкoд N --линия 14 задержки группа 18 элементов И и группа 22 элементов ИЛИ, регистр 6, преобразователь 5 код-ток и через преобразователь, 7 ток-напряжение на выход уст ройства; код N - линия 16 задержки группа 19 элементов И и группа 21 элементов ИЛИ, регистр I, преобразователь 2 код-ток, преобразователь 4ток-напряжение, преобразователь 5код-ток и через преобразователь 7 ток-напряжение на выход устройства. После окончания продвижения входных кодов коды, образовавшиеся в регистрах 1 и 6, поступают на преобразование в соответствующие преобразователи 2 и 5 код-ток, На аналоговый вход преобразователя 2 код-ток поступает dnopHoe напряжение с выхода источника 3 опорного напряжения. Ток с выхода преобразователя 2 поступает на вход преобразователя 4 ток-напряжение, где и преобразуется в напряжение, которое используется в качестве опорного напряжения в преобразова- . теле 5 код-ток; На цифровые входы преобразователя код-ток поступает код второго сомножителя, ив резуль тате преобразования на выходе преобразователя получаем ток, пропорциональный произведениюсомножителей, который поступает на вход преобразователя 7 ток-напряжение, Напряжение на выходе преобразователя 7 является выходным напряжением устройства. Когда, код и J проходит по первому преобразовательному тракту, а код и - по второму тракту, относительная погрешность произведения 1 .. . 2-1 . 2 M N; -N;-Y- i7 ;. где У - относительная погрешность каждого тракта, приведенная к весу младшего разряда цифроаналогового тракта преобразователя;п - количество разрядов по каждому тракту преобразования. Если же прохождение кодов сомножителей противоположное, то относительная погрешность .. Таким образом, направляя по первому тракту каждьй ряд код больпего из. вух сомножителей, можно уменьшить огрешность преобразования и тем самым повысить точность перемножения вух сомножителей, Рассмотренное устройство позволяет в среднем получить погрешность результата перемножения вдвое менье, чем в прототипе. Для случая.

когда требуется обеспечить точность преобразования, равную точности прототипа, устройство может быть реализовано наиболее дешевой элементной базе с худшими метрологическими характеристиками. Указанные о.бстоятельства обеспечивают тёхнцко-экономическую эффективность возможного применения рассмотренного множительного устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Функциональный генератор | 1979 |

|

SU781839A1 |

| Аналого-цифровое множительное устройство | 1983 |

|

SU1117655A1 |

| Инкрементный умножитель аналоговых сигналов | 1983 |

|

SU1113820A1 |

| Устройство для контроля аналоговых объектов | 1989 |

|

SU1718189A1 |

| Множительное устройство | 1980 |

|

SU900293A1 |

| Устройство для умножения двоичных чисел | 1980 |

|

SU981996A1 |

| Множительно-делительное устройство | 1980 |

|

SU902026A1 |

| Вычислительное устройство | 1986 |

|

SU1320819A1 |

| Функциональный генератор | 1984 |

|

SU1267395A1 |

| Множительно-делительное устройство | 1979 |

|

SU840942A1 |

ЦИФРОАНАЛОГОВОЕi МНОЖИТЕЛЬНОЕ УСТРОЙСТВО, содержащее два регистра, выход первого из которых соединен с цифровь(м входом первого преобразователя код-ток, подключенного аналоговым входом к вьгходу источника опорного напряжения, а выходом к входу первого преобразователя токнапряжение, соединенного выходом с аналоговым входом второго преобразователя код-ток, подключенного цифровым входом к выходу второго регистра, а выходом - к входу второго преобразователя ток-напряжение, выход которого является выходом-устройства, отличающееся тем, что, с целью повышения точности умножения р широком диапазоне изменения значе ий сомножителей, в него дополнительно введены коммутатор, блок сравнения, линии задержки, генератор тактовых импульсов и третий и четвёртый регистры, соединенные информационными входами с шинами ввода кодов соответствующих сомножителей, а управляющими входами - с выходом генератора тактовых импульсов, причем выход третьего регистра подключен к первому информационному входу блока сравнения и через первую линию задержки - к первому информационному входу коммутатора, соединенного пер(Л вым и вторым выходами с входами первого и второго регистров соответственно, управляющими входами - с прямым и инверсным выходами блока сравнения, а вторым информационным входом - с выходом второй линии задержки,- подключенной входом к выходу чет- вертого регистра и к второму информационному входу блока сравнения, Ol соединенного стробирующим входом с о ел выходом генератора тактовых импульсов.

| Множительно-делительное устройство | 1976 |

|

SU674042A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Шило В.Л. | |||

| Функциональные аналоговые интегральные микросхемы | |||

| М.: Радио и связь, 1982, с | |||

| Приспособление для плетения проволочного каркаса для железобетонных пустотелых камней | 1920 |

|

SU44A1 |

| Котел | 1921 |

|

SU246A1 |

Авторы

Даты

1986-12-15—Публикация

1983-01-11—Подача