1

Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислителях.

Известно множительное устройство, содержащее реверсивный счетчик, прямой и реверсивный входы которого связаны с соответствующими выходами переключателя, вход которого подключен к выходу элемента И, первый вход которого соединен с выходом тактового генератора, а второй вход - с соответствующим выходом генератора синхроимпульсов, управляющий вход переключателя подключен к выходу компаратора, выходы разрядов реверсивного счетчика соединены со входами цифроаналогового преобразователя, аналоговый вход которого через первый -и второй ключи связан соответственно с входамиопорного напряжения и второго сомножителя, выход цифроаналогового преобразователя связан с первым входом компаратора и через

третий ключ - со входом элемента памяти, управляющие входы ключей подключены к соответствующим выходэм генератора синхроимпульсов 1.

Недостатками этого устройства явпяются пониженное быстродействие и налоговая форма представления результата.

Наиболее близким по технической сущности к предлагаемому изобретению

10 является множительное устройство,содержащее дополнительно введенные четвертый и пятый ключи, при этом второй вход компаратора соединен через четвертый ключ с выходом элемен15та памяти, а через пятый ключ - с входом первого сомножителя, выходы реверсивного счетчика являются цифровыми выходами устройства С 21.

Однако в данном устройстве весь

20 цикл преобразования осуществляется в три последовательных такта: преобразование первого сомножителя в циф ровой код, перемножение второго сомножителя, представленного в аналоговой форме, на цифровой код второго сомножителя и запоминание результата перемножения в аналоговой форме в элементе памяти и преобразование ана; логовой .величины результата в цифровой код., Выполнение операций последовательно во времени снижает быстродействие устройства, что является его недостатком.

Цель изобретения - повышение быстродействия устройства.

Поставленная цель достигается тем, что в множительное устройство, содержащее первый реверсивный счетчик,пер вый цифроаналоговый преобразователь, первый компаратор, тактовый генератор и первый переключатель, выходы . которого соответственно подключены к прямому и реверсивному входам первого реверсивного счетчика; первая группа разрядных выходов которого подключена к разрядным входам первого цифроаналогового преобразователя, выход которого подключен к первому входу первого компаратора, второй вход первого компаратора является входом первого сомножителя устройства, выход первого компаратора подключен к информационному входу первого переключателя, дополнительно введены второй реверсивный счетчик, второй и третий цифроаналоговые преобразователи, второй компаратор, элемент задержки и второй переключатель, выходы которого соответственно подключены к прямому и реверсивному входам второго реверсивного счетчика, разрядные выходы которого являются выходом устройства и подключены к разрядным входам второго цифроаналогового преобразователя, аналоговые входы первого и второго цифроаналогового преобразователей объединены и являются входом опорного напряжения устройства, вторая группа разрядных выходов первого реверсивного счетчика подключена к разрядным входам третьего цифроаналогового преобразователя, аналоговый вход которого является входом второго сомножителя устройства, выходы второго и третьего цифроаналоговых преобразователей подключены соответственно к первому и второму входам второго компаратора,выход которого подключен к информационному входу второго переключателя, управляющий вход второго переключателя подключен к выходу элемента задержки.

ВХОД которого подключен к выходу тактового генератора и к управляющему входу первого переключателя.

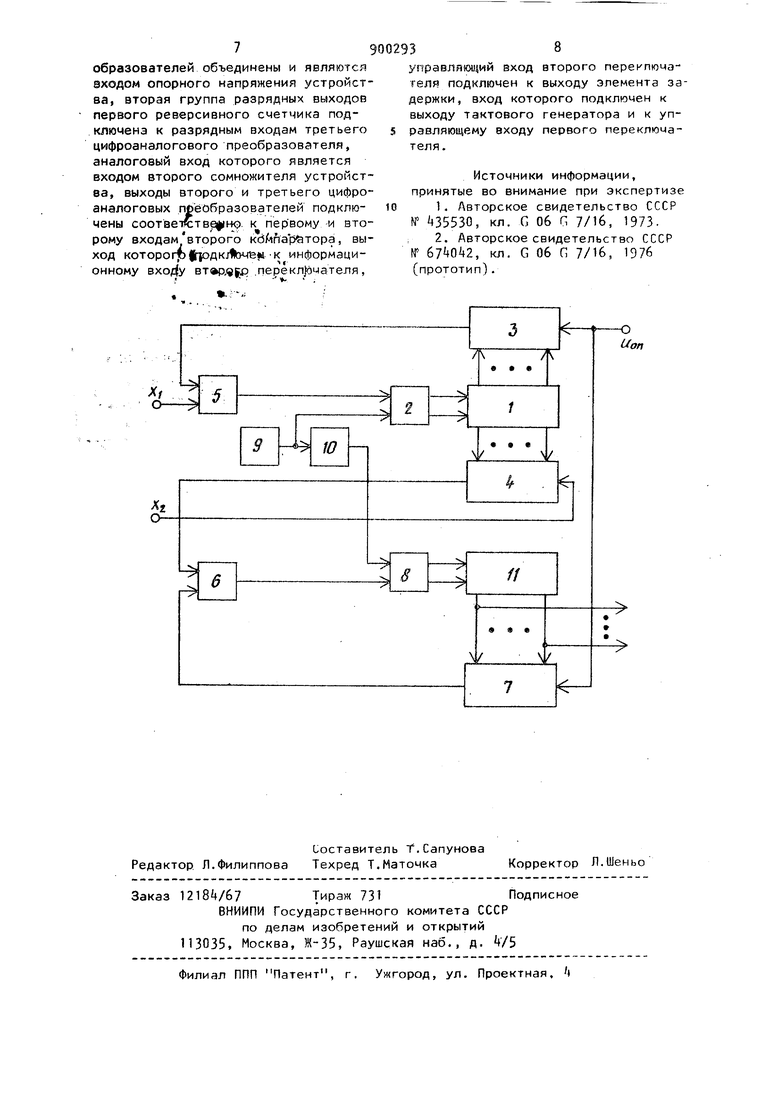

На чертеже представлена функциональная схема множительного устройства.

Множительное устройство содержит первый реверсивный счетчик 1, прямой и реверсивный входы которого связаны с соответствующими выходами первого переключателя 2, а группы разрядных выходов - с соответствующими входами первого и третьего цифроаналоговых преобразователей 3 и , аналоговые входы которых подключены ко входам опорного напряжения UODH второго сомножителя устройства, а выходы - к первым входам первого и второго компараторов 5 и 6, вторые входы которых подключены ко входу первого сомножителя X. устройства и выходу второго цифроаналогового преобразователя 7, а выходы - к информационным входам первого и второго переключателей 2 и 8, управляющие входы которых подключены к входу тактового генератора 9 непосредственно и через элемент задержки 10, второй реверсивный счетчик 11, прямой и реверсивный входы которого подключены к соответствующим выходам второго переключателя 8, а выходы разрядов к соответствующим входам второго циф роаналогового преобразователя 7, аналоговый вход которого связан со входом опорного напряжения UQ-, Разрядные выходы второго реверсивного счетчика 11 являются цифровыми выходами устройства.

Устройство может работать в двух режимах, устанавливаемых автоматически: начальной отработки и слежения.

В первый режим .устройство переходит в момент поступления перемножаемых сигналов X. и X,, на второй вход компаратора 5 и на аналоговый вход цифроаналогового преобразователя 4. При этом в зависимости от первоначального состояния компараторов 5 и 6, управлякицих переключателями 2 и 8, тактовые импульсы с генератора 9 поступают через переключатели 2 и 8 на прямые, либо реверсивные входы реверсивных счетчиков 1 и 11. Благодаря наличию петель обратной цифроаналоговой связи (элементы 3, 5 и 6, 7) коды реверсивных счетчиков изменяются тлк, что уменьшают разности между сигналами, поступающими на вторые входы компараторов и сигналами обратной связи, поступающими нэ их первые входы, до минимума. Каждый тактовый импульс изменяет ход в счетчике 1 на единицу младшего раз ряда, а н.апряжение на выУоде цифроаналогового преобразователя - на одну градацию, величина которой зависит от величины сигнала Х. При этом состояние компаратора может изменять ся или нет. Так как сигнал с выхода компаратора поступает на переключатель 8 с задержкой, вносимой элементами 2, 1, + и 6, то возникает необходимость задержки тактовых импульсов, поступающих на переключатель 8 на величину, несколько превышающую вносимую задержку. Для этой цели слу жит элемент задержки 10. Режим начальной отработки прекращается как только оба компаратора 5 и 6 .изменят свое состояние, т.е. когда разность между напряжениями на входах каждого из них станет меньше одной градации. Длительность этого режима определяется состоянием реверсивных счетчиков и величиной сигналов-сомно жителей в момент включения последних. Основным режимом работы устройства является режим слежения.Прин цип действия устройства в этом режиме остается . Отличие от первого режима проявляемся лишь в том, что разности сигналов на входах компараторов не превышают величины одной градации. При этом код в реверсивном счетчике 1 пропорционален отношению первого сомножителя и опорного напряжения, т.е. отображает относительную величину сигнала Х. Нап ряжение на выходе цифроаналогового преобразователя k является величиной пропорциональной произведению величин сигналов Х.( и У. в момент поступления тактового импульса. Код в реверсивном счетчике 11 является округленной до целого величиной произведения относительных величин сигналов-сомножителей. Этот код снимается с выходов разрядов реверсивного счет чика 11 и может быть использован для дальнейшей обработки. Можно показать, что по сравнению с известными устройствами в предлагаемом устройстве время перемножения (время получения первого результата, равное длительности режима начальной отработки) определяется только временем формирования кода N величины Х и величиной задержки, вносимой элементом задержки. Так как последняя величина меньше периода следования тактовых импульсов, то ею мох(но пренебречь. В таком случае при равных емкостях счетчиков и одинаковых периодах следования тактовых импульсов время перемножения в режиме начальной обработки в два раза меньше, чем в известных устройствах,Обычно сигналы перемножают многократно в дискретные моменты времени. Все остальные результаты перемножения получаются в режиме слежения с задержкой в один период следования тактовых импульсов. Таким образом, в режиме слежения время перемножения в предлагаемом устройстве в 2Q раз меньше по сравнению с известным. Формула изобретения Множительное устройство, содержащее первый реверсивный счетчик, первый цифроаналоговый преобразователь, первый компаратор, тактовый генератор и первый переключатель, выходы которого соответственно подключены к прямому и реверсивному входам первого реверсивного счетчика, первая группа разрядных выходов которого подключена к разрядным входам первого цифроаналогового преобразова- . теля, выход которого подключен к первому входу первого компаратора, второй вход первого компаратора является входом первого сомножителя устройства, выход первого компаратора подключен к информационному входу первого переключателя, отличающееся тем, что, с целью повышения быстродействия, в устройство дополнительно введены второй реверсивный счетчик, второй и третий цифроаналоговые преобразователи, второй компаратор, элемент задержки и второй переключатель, выходы которого соответственно подключены к прямому и реверсивному входам второго реверсивного счетчика, разрядные выходы которого являются выходом устройства и подключены к разрядным входам второго цифроаналогового преобразователя, аналоговые входы первого и второго цифроаналоговых преобразователей объединены и являются 8ХОДОМ опорного напряжения устройст ва, вторая группа разрядных выходов первого реверсивного счетчика подключена к разрядным входам третьего цифроаналогового преобразователя, аналоговый вход которого является входом второго сомножителя устройст ва, выходы второго и третьего цифро аналоговых преобразователей подключены cooTBeTCTBei iHO. к первому и вто рому входамвторого кййпарйтора, вы ход когорогр 13р,.--к информационному Bxorfy ,18|р .перёкл)дмателя,

002938

управлякнций входвторого переключателя подключен квыходу элемента задержки, вход которого подключен к выходу тактовогогенератора и к управляющему входупервого переключателя.

Источники информации, принятые во внимание при экспертизе to 1. Авторское свидетельство СССР № i 35530, кл. G Об С 7/16, 1973. I 2. Авторское свидетельство СССР № , кл. G 06 П 7/16, 1976 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Множительно-делительное устройство | 1976 |

|

SU674042A1 |

| АНАЛОГО-ЦИФРОВОЕ МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО | 1997 |

|

RU2121712C1 |

| Множительно-делительное устройство | 1980 |

|

SU883920A2 |

| Множительно-делительное устройство | 1980 |

|

SU902026A1 |

| АНАЛОГО-ЦИФРОВОЕ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО | 1997 |

|

RU2123720C1 |

| Цифроаналоговое множительное устройство | 1983 |

|

SU1105050A1 |

| Аналого-цифровое множительное устройство | 1980 |

|

SU883930A1 |

| Аналого-цифровое множительное устройство | 1983 |

|

SU1117655A1 |

| Множительно-делительное устройство | 1979 |

|

SU840942A1 |

| Вычислительное устройство | 1986 |

|

SU1320819A1 |

Авторы

Даты

1982-01-23—Публикация

1980-04-07—Подача