00

сх с с

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых узлов | 1981 |

|

SU978154A1 |

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| Сигнатурный анализатор | 1986 |

|

SU1386995A1 |

| Устройство для контроля цифровой аппаратуры | 1989 |

|

SU1735854A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1120338A1 |

| Микропрограммное устройство управления с контролем | 1989 |

|

SU1647565A1 |

| Устройство для контроля цифровых узлов | 1985 |

|

SU1269139A1 |

| Устройство для контроля цифровых блоков | 1989 |

|

SU1742753A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1343417A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано для контроля и диагностики дифровых блоков методом сигнатурного анализа. Целью изобретения является повышение достоверности контроля. Устройство содержит переключатель 1, генератор 2 тестов.

Фиг. 1

мультиплексор 3, элемент И 4, контролируемый блок 5, блок 6 переключения сигналов синхронизации, элемент ИЛИ 7, элемент И 8, триггер 9, мультиплексор 10, сигнатурный анализатор 11, узел 12 управления режимом, блок 13 постоянной памяти, триггер 14, блок 15 формирования адресов, узел 16 сравнения, индикатор 17. Контроль и диагностика цифровых блоков с помощью устройства осуществляются в три этапа. На первом этапе выявляются неисправные блоки визуальным сличением общих сигнатур блоков - реальных и эталонных. На втором эта1

Изобретение относится к цифровой вычислительной технике и может быть использовано для -контроля и диагностики цифровых бл,оков методом сигнатурного анализа.

Целью изобретения является повышение достоверности контроля.

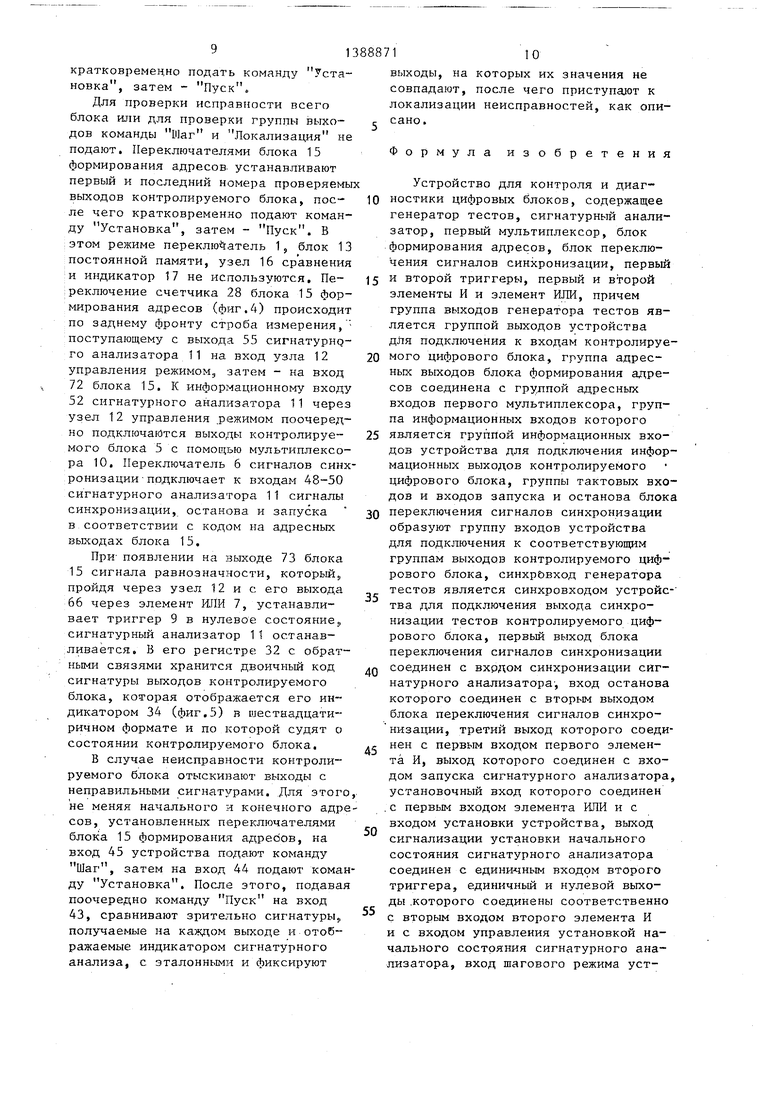

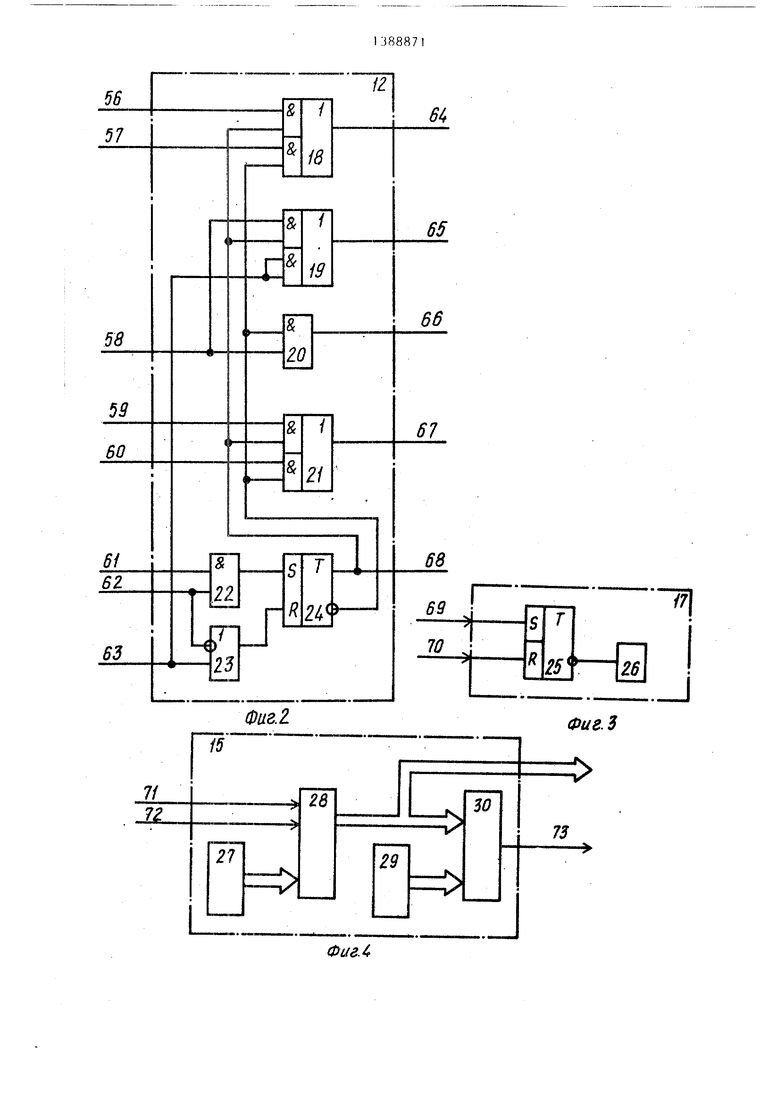

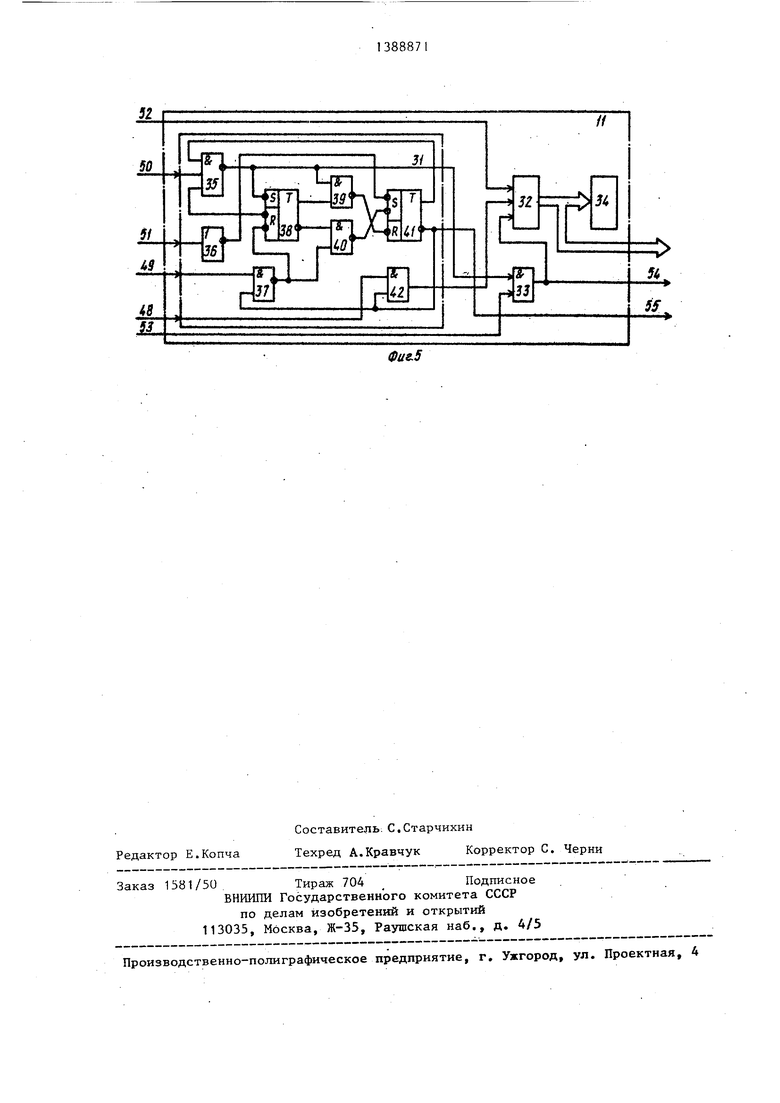

На фиг.1 приведена структурная схема устройства; на фиг.. - функциональная схема узла управления ре- жимом; на фиг.3 - функциональная схема индикатора; на фиг.4 - структурная схема блока, формирования адресов; на фиг.5 - структурная схема сигнатурного анализатора.

Устройство содержит переключатель 1, генератор 2 тестов, мультиплексор 3, элемент И 4, контролируемый блок 5, блок 6 переключения сигналов синхронизации, элемент ИЛИ 7, элемент И 8, триггер 9, мультиплексор 10, сигнатурный анализатор 11, узел 12 управления режимом блок 13 постоянной памяти, .триггер 14, блок 15 формирования адресов, узел 16 сравнения индикатор 17, элемент И-ИЛИ 18, элемент И-ШШ 19, элемент И 20, элемент И-ИЛИ 21, элемент И 22, элемент ИЛИ 23, триггер 24, триггер 25, элемент 26 индикации, переключатель 27, счёт чик 28, переключатель 29, узел 30 сравнения, формирователь 31 интервалов, регистр 32 сдвига с обратными связями, элемент И 33, индикатор

пе сличением сиг натур выявляются выходы и контрольные точки блоков, на которых реальные сигнатуры не соответствуют эталонным. На третьем этапе осуществляется локализация неисправностей в блоках автоматическим сравнением реальных сигнатур с эталонными, Устройство обеспечивает автоматическое сравнение реальных сигнатур любых внутренних точек блоков с эталонными, хранящимися в памяти устройства, с произвольным порядком их подключения, что, в конечном счете, повышает достоверность контроля. 5 ил.

34, элемент И 35, элемент ИЛИ 36, элемент И 37, триггер 38, элементы И 39 и 40, триггер 41, элемент И 42, вход 43 пуска, вход 44 установки, вход 45 шагового режима, вход 46 подключения пробника, вход 47 локализации неисправностей - входы устройства, вход 48 синхронизации, вход 49 установа, вход 50 запуска, вход 51 установки, информационньм вход 52, вход 53 управления - входы сигнатурного анализатора, управляющий выход 54, выход 55 строба изменения - выходы сигнатурного анализатора, входы 56-63 И, выходы 64-68 узла управления режимом, управляюп ий вход 69 и вход 70 установки индикатора, вход 71 установки и счетный вход 72 блока формирования адресов, управляющий выход 73 блока формирования адресов.

Переключатель 1 предназначен для выбора сигналов синхронизации при измерении двоичных последовательностей в точках блока выбранной группы при локализации неисправностей.

Генератор 2 тестов предназначен для генерирования стимулирующих сигналов в виде двоичных последовательностей, подаваемых на входы контролируемого блока.

Мультиплексор 3 предназначен для подключения адресных входов блока 6 переключения сигналов синхронизации к адресным выходам блока 15 фор- .мирования адресов или к выходам переключателя 1.

Элементы И k или ИЛИ 7 предназначены для управления триггером 9 по входу установки в нулевое состояние.

Блок 6 переключения сигналов сиш хронизации предназначен для подключения к входам синхронизации, останова и запуска сигнатурного анализатора соответствую1чих выходов контролируемого блока 5 сигналов синхронизации в зависимости от кода на адресных входах блока.

Элемент ИЛИ 7 предназначен для пропуска импульсов запуска на вход запуска сигнатурного анализатора 11.

Триггер 9 предназначен для управления прохождением импульсов запуска через элемент ИЛИ 7.

Мультиплексор 10 предназначен для поочередного подключения выходов контролируемого блока 5 к информационному входу сигнатурного анализатора 11 через узел 12 управления режимом.

Сигнатурный анализатор 11 предназначен для преобразования двоичных последовательностей на выходах контролируемого блока в короткие двоичные коды (сигнатуры)и для их отображения световым индикатором в шестнадцатиричном формате.

Узел 12 управления режимом подключает к информационнному входу сигнатурного анализатора 11 вход 46 подключения пробника или выход мультиплексора 10, управляет блоком переключения адресов по входам 71 и 72 установки и счета, управляет триггером 9 через элемент ИЛИ 7, управляет мультиплексором 3, блоком 13 постоянной памяти, узлом 16 сравнения, индикатором 17, обеспечивая работу устройства в соответствующих режимах, в зависимости от значения сигнала на входе 47 устройства.

Блок 13 постоянной памяти предназначен для хранения эталонных сигнатур точек цифровых блоков, проверяемых в режиме локализации неисправностей.

Триггер 14 обеспечивает работу устройства в шаговом режиме.

Блок 15 формирования адресов предназначен для формирования адресов в диапазоне, ограниченном его началь- Hbw и конечным адресами, задаваемыми

с помощью его переключателе 27 и 29, и поступающих на адресные пходы мультиплексоров 3 и 10 и блока 13. с Узел 16 сравнения служит для сраи- нения реальных сигнатур проверяемых точек блоков с эталонными сигнатурами групп точек.

Индикатор 17 предназначен для 0 индикации результата сравнения эталонных сигнатур группы точек с реальной сигнатурой проверяемой точки контролируемого блока.

Вход 43 предназначен для подачи 5 команды Пуск, вход 44 - команды

Установка, вход 45 - команды Шаг, вход 47 - команды Локализация, вход 46 служит для подключения пробника. Контроль и диагностика цифровых 0 блоков с помощью устройства осуп(ест- вляется в три этапа. На первом этапе выявляются неисправные блоки визуальным сличением общих сигнатур блоков - реальных и эталонных. На вто- 5 ром этапе сличением сигнатур выявляются выходы и контрольные точки блоков, на которых реальные сигнатуры не соответствуют эталонным. На третьем этапе.;осуществляется локализация 0 неисправностей в блоках с помощью пробника и автоматическим сравнением реальных сигнатур каждой точки в группе точек, причастных к формированию сигнала на выходе блока или в контрольной точке, с эталонными сигнатурами группы точек.

Устройство в режиме локализации неисправностей работает следующим образом,

0 На выбранные входы контролируемого блока 5 (фиг,1) от генератора 2 тестов поступают стимулирующие двоичные последовательности, синхронизируемые контролируемым бл оком, для 5 чего из последнего в генератор тестов поступает сигнал синхронизации в виде импульсной последовательности. При этом на выходах и внутренних точках контролируемого блока возникают Q соответствующие реакции, В соответствии с номером выхода или контрольной точки с неправильной сигнатурой, или номером группы микросхем .переключателем 1 устанавливают номер группы . сигналов синхронизации сигнатурного анализатора, а переключателями 27 и 29 (фиг,4) блока 15 формирования, адресов соответственно устанавливают начальный и конечный адреса поддиапазона адресного пространства блока 13 постоянной памяти, в котором хранятся эталонные сигнатуры точек конт ролируемого блока.

На вход 47 устройства подают команду Локализация, к входу 46 подключают пробник, на вход 45 подают команду Шаг, на вход 44 кратковременно подают команду Установка.

Команда Установка устанавливает триггер 9 в нулевое состояние, чем закрывает элемент И 8, запрещая поступление импульсов запуска на вход 50 сигнатурного анализатора 11, являющегося входом запуска его узла 31 (фиг.5) формирования интервалов измерения, устанавливает узел 31 в состояние ожидания запуска и блокирует прием импульса останова по входу 49, поступив на вход 63 узла 12 задания режимов, устанавливает его триггер 24 (фиг,2) в нулевое состояние и, пройдя через элемент И-ИПИ 19 на вход 65 блока 15 формирования адресов, задним фронтом записывает в его счетчик 28 (фиг.4) код начального адреса поддиагГазона, поступающий из переключателя 27.

Обеспечив контакт пробника с выбранной точкой, на вход 43 устройства подают команду Пуск, Команда Пуск устанавливает триггер 9 в единичное состояние, который открывает элемент И 8, разрешая прохождение импульсов запуска на вход 50 сигнатурного ана.лизатора 11 (фиг.5) и его формирователя 31 интервала измерения, устанавливает триггер 14 в нулевое состояние, который через вход 53 сигнатурного анализатора 11 открывает его элемент И 33 (фиг.5)„ поступив на вход 61 узла 12 и пройдя через эле мент И 22, устанавливает триггер 24 (фиг.2) в единичное состояние. При этом открывается первый элемент И элемента И-ИПИ 18 и закрывается его второй элемент И, открывается первый элемент И элемента И-ШШ 19, закрывается элемент И 20, открывается первый элемент И элемента И-ШШ 21 и закрывается его второй элемент И, .3 связи с чем к информационному вхо. ду 52 сигнатурного анализатора 11 подключается вход 46 подключения пробника, а вход 71 установки блока 15 формирования адресов, вход 70 установки триггера 17 и второй вход элемента ИЛИ 7 подключается к выходу

0

5

0

5

0

5

0

5

0

5

73 блока 15 формирования адресов, являющимся выходом его узла 3.0 сравнения (фи1.4), а к его счетному вход 72 подключается выход синхронизации тестов контролируемого блока 5.

Установившийся единичный уровень на выходе 68 узла 12 разрешает выборку эталонных сигнатзф из блока 13 и сравнение их с реальными сигнатурами узлом 16 сравнения, подключает выходы переключателя 1 с помощью мультиплексора 3 к адресным входам блока 6 переключения сигналов синхронизации, что приводит, в св ою очередь, к разрешению приема, его группой из трех входов, выбранной из многих групп информационных входов переключателем 1, сигналов синхронизации, останова и запуска сигнатурного анализатора 11, генерируемых контролируемым блоком 5,

Первый импульс запуска проходит через открытый элемент И 8 на вход 50 сигнатурного анализатора 11 и поступает на вход запуска его формирователя 31 интервалов измерения (фиг.5), который формирует по импульсу запуска импульс-установки, и после окончания импульса запуска переходит в состояние измерения. Импульс установки, пройдя через открытый элемент И 33, устанавливает ре- гистр 32 сдвига в единичное состояние и триггер 14 задним фронтом - в единичное состояние с выхода 54 сигнатурного анализатора 11. Единичный сигнал триггера 14 проходит через элементы И 4, ИЛИ 7 и устанавливает триггер 9 в нулевое состояние, что приводит к закрыванию элемента И 8 и прекращению прохождения последующих импульсов запуска.

В состоянии измерения в узле 32 (фиг.5) блокируется запуск сигнатурного анализатора по входу 50 и разрешается его останов по входу 49, формируется строб измерения двоичной последовательности проверяемой точки, начало которого определяется задним фронтом импульса запуска, а окончание - задним фронтом импульса останова. Строб измерения разрешает прохождение импульсов синхронизации с входа 48 сигнатурного анализатора 11 на соответствующий вход регистра 32 сдвига с обратными связями, проис ходит запись в него в сжатой форме

двоичной последовательности проверяемой точки - сигнатуры,

В конце измерения на вход 49 поступает 1шпульс останова, по окончании которого узел 31 (фиг.5) переходит в состояние ожидания импульса запуска, прекращается формирование строба измерения и прохождение импульсов синхронизации. Двоичное число, хрханящееся в регистре 32 сдвига, преобразуется в индикаторе 34 в шестнадцатиричную форму и отображается его световым индикатором. Одновременно код этого числа в параллельной форме поступает на вторую группу инг формационных входов узла 16 сравнения.

С выхода синхронизации тестов контролируемого блока 5 поступает непрерывная импульсная последовательность на вход синхронизации генератора 2 тестов, на вход синхронизации блока 13 постоянной памяти и на вход 59 узла 12 управления режимом, где она проходит через первый элемент И элемента И-ИЛИ 21 (фиг.2) и с выхода 67 поступает на счетный вход 72 блока 15 формирования адресов, в котором каждьй ее импульс задним фронтом переключает счетчик 28 (фиг.4) в следующее состояние. Когда на выхода счетчика 28 появится код, равньй установленному переключателем 29, на выходе узла 30 сравнения появится сигнал равнозначности, который с выхода 73 поступает на вход 58 узла 12 управления режимом и проходит через его открытый первый элемент И элемента И-ИЛИ 19 на выход 65, откуда поступает на вход 71 установки блока 15 формирования адресов, в котором записывает в счетчик 28 на- чальный адрес поддиапазона адресов эталонных сигнатур выбра нной группы точек контролируемого .блока, и на вход 70 индикатора 17, устанавливая его триггер 25 (фиг.З) в нулевое состояние. Эти циклы будут повторяться, пока на входе 47 устройства будет присутствовать команда Локализация.

Образующиеся на адресных выходах блока 15 формирования адресов коды адресов поступают на первую группу информационных входов мультиплексора 3, на адресные входы мультиплексора 10 и на адресные входы блока 13 постоянной памяти. Однако эти адресные

коды в режиме локализации неисправностей являются эффективными лишь для блока 13, из которого происходит. непрерывная циклическая выборка эталонных сигнатур в поддиапазоне адресов, ограниченном начальным и конечным адресами, заданными переключателями 27 и 29 блока 15 формирования

адресов, Двоичньм код эталонных сигнатур (например, шестнадцатиразрядный) с информационных выходов блока 13 поступает на первую группу информационных входов узла сравнения для

сравнения их с сигнатурой, образованной в регистре 32 сигнатурного анализатора 11 и хранящейся в нем до прихода следующей команды Пуск. Процесс сравнения стробирует.ся импульсами стробирования, которые

вырабатываются в блоке 13 постоянной памяти и поступают на вход стробирования узла 16 сравнения.

Для измерения двоичной последовательности в следующей точке, выбранной группы точек контролируемого блока необходимо подключить следующую точку к выходу 46 устройства, после .чего на вход 43 подать команДУ Пуск.

5

0

При равнозначности кодов одной из эталонных сигнатур и кода сигнатуры, хранящейся в регистре с обратными связями сигнатурного анализатора, на выходе узла 16 сравнения появляется сигнал равнозначности, который поступает на вход 69 индикатора 17 и устанавливает его три1- гер 25 (фиг.З) в единичное состояние, что приводит к срабатьшанию элемента 26 индикации, который сигнализирует о соответствии сигнатур - эталонной и проверяемой точки.

Переходя от точки к точке в выбранной группе точек контролируемого блока и осуществляя каждьй раз подачу команды Пуск на вход 43 устройства - после подключения проверяемой точки к входу 46 - производят поиск неисправностей,

Для исследования точек другой группы необходимо установить переключателем 1 другой номер группы си1- налов синхронизации, а переключателя- 5 ми 27 и 29 блока 15 формирования адресов - начальный и конечный адреса другого поддиапазона адресов эталонных сигнатур, после чего на вход 44

5

,0

91

кратковременно подать команду Установка, затем - Пуск.

Для проверки исправности всего блока или для проверки группы выходов команды Шаг и Локализация не подают. Переключателями блока 15 формирования адресов, устанавливают первый и последний номера проверяемы выходов контролируемого блока, после чего кратковременно подают команду Установка, затем - Пуск. В этом режиме переклю гатель 1, блок 13 постоянной памяти, узел 16 сравнения и индикатор 17 не используются. Переключение счетчика 28 блока 15 формирования адресов (фиг.4) происходит по заднему фронту строба измерения, поступающему с выхода 55 сигнатурнр- го анализатора 11 на вход узла 12 управления режимом., затем - на вход 72 блока 15, К информационному входу 52 сигнатурного анализатора 11 через узел 12 управления .режимом поочередно подключаются выходы контролируемого блока 5 с помосцью мультиплексора 10, Переключатель 6 сигналов синхронизации- подключает к входам 48-50 сигнатурного анализатора 11 сигналы синхронизации, останова и запуска в соответствии с кодом на адресных выходах блока 15,

При- появлении на выходе 73 блока 15 сигнала равнозначности, который,, пройдя через узел 12 и с его выхода 66 через элемент ИГШ 7, устанавливает триггер 9 в нулевое состояние,, сигнатурный анализатор 11 останавливается, В его регистре 32 с обратными связями хранится двоичный код сигнатуры выходов контролируемого блока, которая отображается его индикатором 34 (фиг,5) в шестнадцатиричном формате и по которой судят о состоянии контролируемого блока,

В случае неисправности контролируемого блока отыскивают выходы с неправильными сигнатурами, .Для этого не меняя начального и конечного адресов, установленных переключателями блока 15 формирования адресов, на вход 45 устройства подают команду Шаг, затем на вход 44 подают команду Установка, По(ше этого, подавая поочередно команду Пуск на вход 43, сравнивают зрительно сигнатуры,, получаемые на каждом выходе и отображаемые индикатором сигнатурного

анализа, с эталонными и фиксируют

1

10

выходы, на которых их значения не совпадают, после чего приступает к локализации неисправностей, как описано.

Формула изобретения

0

5

0

5

0

5

0

5

0

5

Устройство для контроля и диагностики цифровых блоков, содержащее генератор тестов, сигнатурный анализатор, первый мультиплексор, блок формирования адресов, блок переключения сигналов синхронизации, первый и второй триггеры, первый и второй элементы И и элемент ИЛИ, причем группа выходов генератора тестов является группой выходов устройства дЛя подключения к входам контролируемого цифрового блока, группа адресных выходов блока формирования адресов соединена с грулпой адресных входов первого мультиплексора, группа информационных входов которого является группой информационных входов устройства для подключения информационных выходов контролируемого цифрового блока, группы тактовых входов и входов запуска и останова блока переключения сигналов синхронизации образуют группу входов устройства для подключения к соответствующим группам выходов контролируемого цифрового блока, синхрОвход генератора тестов является синхровходом устройс-- тва для подключения выхода синхронизации тестов контролируемого цифрового блока, первый выход блока переключения сигналов синхронизации соединен с вхрдом синхронизации сигнатурного анализатора-, вход останова которого соединен с вторым выходом блока переключения сигналов синхро- низации, третий выход которого соединен с первым входом первого элемента И, выход которого соединен с входом запуска сигнатурного анализатора, установочный вход которого соединен . с первым входом элемента ИЛИ и с входом установки устройства, выход сигнализации установки начального состояния сигнатурного анализатора соединен с единичным входом второго триггера, единичный и нулевой выходы .которого соединены соответственно С вторым входом второго элемента И и с входом управления установкой начального состояния сигнатурного анализатора, вход шагового режима уст11

роиства соединен с первым входом второго элемента И, выход которого соединен с третьим входом элемента ИЛИ, выход которого соединен с нулевым входом первого триггера, единичный выход которого соединен с вторым входом перв ого элемента И, вход пуска устройства соединен с единичньм входом первого триггера и нулевым входом второго триггера, отличающееся тем, что, с целью повьше ния достоверности контроля, устройство дополнительно содержит второй мультиплексор, переключатель, блок постоянной памяти, узел сравнения, . индикатор и узел управления режимом, который содержит три элемента И-ИЛИ, третий и четвертьй элементы И, второ элемент ИЛИ и третий триггер, при- чем группа выходов переключателя соединена с первой, группой информационных входов второго мультиплексора, вторая группа информационных входов которого соединена с группой адресных входов блока постоянной памяти и группой адресных выходов блока формирования адресо в, группа выходов второго мультиплексора соединена с группой адресных входов блока переключения сигналов синх юнизации, группа информационных выходов блока постоянной памяти соединена с первой группой информационных входов узла .сравнения, вход стробирования которого соединен с выходом стробирования блока постоянной памяти, группа информационных выходов сигнатурного анализатора соединена с второй группой информационных входов узла сравнения, выход которого соединен с входом управления индикатора, первый вход первого элемента И-ИЛИ соединен с дополнительным информационным входом устройства, третий вход первого элемента И-ИЛИ соединен с выходом

10

15

20 8887112

первого мульт11 1лексора, второй вход третьего элемента И соединен с первым входом второго элемента И-ИЛИ и с выходом фиксации конечного адреса блока формирования адресов, первый вход третьего элемента И-ИЛИ соединен с синхровходами генератора тестов и блока постоянной памяти, третий вход третьего элемента И-ИЛИ соединен с выходом строба измерения сигнатурного анализатора, первый вход четвертого элемента И соединен с входом пуска устройства, второй вход четвертого элемента И соединен с первым входом второго элемента ИЛИ и с входом локализации неисправностей устройства, второй вход второго элемента ИЛИ соединен с третьим и четвертым входами второго элемента И-ИЛИ и с входом установки устройства, выход первого элемента И-ИЛИ соединен с информационным входом сигнатурного анализатора, вьгход второго элемента И-ИЛИ соединен с установочными входами блока формирования адресов и индикатора, выход третьего элемента И соединен с вторым входом

первого элемента ИЛИ, выход третьего 2Q элемента И-ИЛИ соединен с информационным входом блока формирования адресов, прямой выход третьего триггера соединен с вторыми входами пер- вого, второго и третьего элементов И-ИЛИ и с входами разрешения второго мультиплексора, блока постоянной памяти и узла сравнения, -инверсный выход третьего триггера соединен с четвертыми входами первого и третьего элементов И-ИЛИ и с первым .входом третьего элемента И, единичный и нулевой входы третьего триггера соединены соответственно с выходами четвертого элемента И второго элемента ИЛИ.

25

35

40

45

Фиг.

-17

.J

| Электроника, 1981, № 4, с.39-40, Авторское свидетельство СССР № 978154, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-04-15—Публикация

1986-03-03—Подача