СО

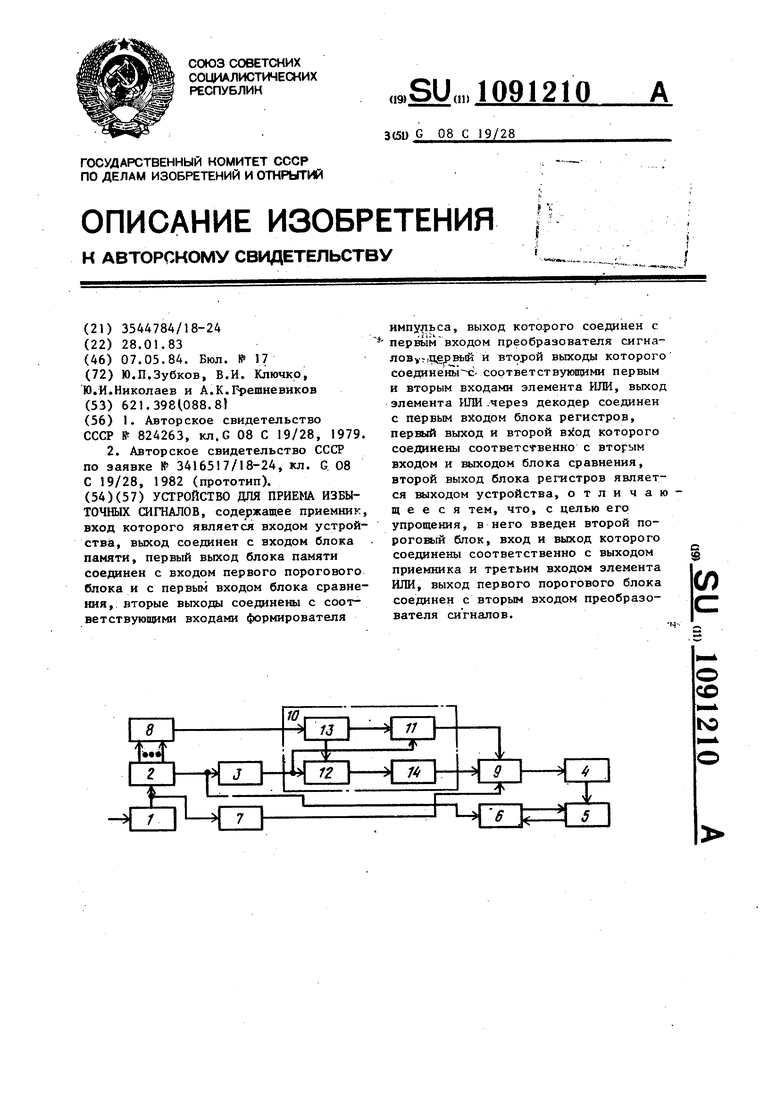

to i Изобретение относится к электросвязи и может быть использовано для приема составных дисв;ретных сигнало с избыточностью. Известно устройство д: приема избь точных сигналов, содержащее приемник, пороговые блоки, Бычитате блоки памяти, блок усилртелей, блок сумматоров, декодер 5 блок управлени и блоки ре.гистров С ID. Недостаток известного устройства сложность из-за наличия большого числа различных блоков. Наиболее близким по технической сущности к предлагаемому является устройство для приема избыточных сигналов, содержащее приемник, вход которого является входом устройства вьход соединен с входэм первого бло ка памяти, первый выход которого соединен с входом порогового блока с первым входом блока сравнения 5 вторые соедине:;в51 с соответствующими входами формирователя импульса s выход которого и выход вгор го блока памяти соединены соответственно с первыгл и вторым входами преобразователя сигналов (логичес™ кого блока l-s выход порогового блока сиединен с входом второго блока памяти к с первым вхоцом элемента 11Г1И первый и второй выходы преобразователя сигналов соединеьы с соответствующими вторым и третьим входами элемента 1ШИг выход ксторого через декодер соединен с первым входом блока регистровJ второй вход и первый выход блока регистров соединены соответственно с выходом и вторым вкодом блока сравнения, второй выхо является выходом устройства t2. Недостатком указанного устройства является сложность из-за наличия двух блоков большого объема. Цель изобретения - упрощение уст о „ роиства за счет устранегния одного .блока памяти. Указанная цель достигается тем„ что в устройство для приема избыточ ных сигналовg содержащее приег-шик,, вход которого является входом устройства, выход соединен с входом блока памяти, первый выход блока па мяти соединен с входом первого поро гового блока и с пврвыьг входом блок сравнения, вторые выходы соединены с соответствукшщми .ьш формирователя импульса, выход которого сое 102 динен с первым входом преобразователя сигналов, первый и второй выходь1 которого соединены с. соответствующими первым и вторым входами элемента ИЛИ., выход элемента ИЛИ через декодер соединен с первым входом блока регистров, первый выход и второй вход которого соединешз соответственно с вторым входом и выходом блока сравнения, второй блока регистров является выходом устройства, введен второй пороговый блок,, вход и выход которого соединен соответственно с выходом приемника и третьим входом элемента ИЛИ, выход первого порогового блока соединен с вторым входом преобразователя сигналов. На чертеже показана структурная схема устройства. Устройство для приема избыточных сигналов содержит приемник 1j блок 2 памяти,, пороговый блок 3, декодер 4э блок 5 регистров 5 блок 6 сравне -шЯэ пороговый блок 7, формирователь 8 импульса, элемент ИЛИ 9 и преобразователь 10 сигналов, который состоит из ключей 11,, 12, триггера 13 и элемента НЕ 14, Устройство работает следующим образом. Входная аналоговая комбинация двоичных символов принимается приемником 1 и поступает в блок 2 памяти « Эти же аналоговые сигналы поступают на вход порогового блока 7, где гфеобразуштся з двоичные сигналы. Двоичные сигналы через элемент ИЛИ 9 подшйтся на вход декодера 4, который ото,ждестш1яет принятую двоичную кодовую комбинацию с ближайшей выходной разрешенной двоичной кодовой комбина цией« Эта разрешенная комбинаи,ия записывается в блок 5 регистров По окончании записи в блок 5 ана- логовые сигналы из блока 2 памяти счигываются в формрфователь 8, Формирователь 8 может быть выполнен на генераторе ,линейно- изменяющегося напряжения,, элементе сравнения, элементе ИЛИ и двоичном регистре. Формирователь 8 определяет наименьший из анапого,вых сигналов, поступа ацих на его вход, и формирует двоичную кодовую ,комбинш1;ию5 в которой единичный симзол находится в разряде с тем же номером что и наименьшей аналоговый символ,, Другие разряда - нулевые. Эта двоичная кодовая комбинация 3 синхронно с кодовой комбинацией, записанной в блоке 2 памяти, поступает на входы преобразователя 10. На выходе преобразователя 10 формируется вторая грубая оценка ( двоичная кодовая комбинация ) избыточного сигнала. Эта комбинация отличается от комбинации первой грубой оценки в разряде, номер которого совпадает с номером наименьшего по амплитуде аналогового символа. Процесс преобразования первой оц ки во вторую следующий. С выхода порогового блока 3 комб нация последовательно поступает на информационные входы ключей II и 12 Управляются ключи двоичными символа ми, поступающими последовательно с выхода формирователя 8 на вход триггера 13. Если на вход триггера 13 поступает нулевой сигнал, то открыт ключ 11. Если на вход триггера подается единичный сигнал, то ключ 11 закрывается, ключ 12 открывается и соответствуииций информационньй си 104 нал изменяется на противоположный с помощью элемента НЕ 14. Выходные сигналы преобразователя 10 через злемент ИЛИ 9 поступают на вход декодера 4, в котором отождествляются с разрешенной двоичной кодовой комбинацией. Эта комбинация запоминается в блоке 5 регистров. В блок 6 сравнения поступают точная оценка избыточного сигнала, считываемая из блока 2, и двоичные разрешенные кодош 1е комбинации из блока 5 регистров,. В блоке 6 сравнения определяется, какая из двух разрешенных комбинаций больше соответствует сигналу точной оценки. Эта комбинация по управляющему сигналу, вырабатываемому в блоке 6, считывается из блока 5 на выход устройства. Таким образом, в предлагаемом устройстве в результате введения второго порогового блока и исключения блока памяти удалось упростить устройство.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема избыточных сигналов | 1989 |

|

SU1695353A1 |

| Устройство для приема избыточных сигналов | 1983 |

|

SU1107145A1 |

| Устройство для приема избыточной информации | 1982 |

|

SU1032470A1 |

| Устройство для приема избыточной информации | 1983 |

|

SU1107146A1 |

| Устройство для декодирования избыточных кодов | 1983 |

|

SU1105927A1 |

| Устройство для приема и обработки избыточной информации | 1983 |

|

SU1140141A1 |

| Устройство для приема и градиентного декодирования избыточных сигналов | 1983 |

|

SU1152016A1 |

| Адаптивное устройство для обработки избыточной информации | 1982 |

|

SU1062752A1 |

| Устройство для приема и обработки избыточных сигналов | 1984 |

|

SU1218415A1 |

| Устройство для приема и обработки избыточных сигналов | 1984 |

|

SU1233201A1 |

УСТРОЙСТВО ДЛЯ ПРИЕМА ИЗБЫТОЧНЫХ СИГНАЛОВ, содержащее приемник, вход которого является входом устройства, выход соедииеи с входом блока памяти, первый выход блока памяти соединен с входом первого порогового блока и с первым входом блока сравнения, вторые выхода соединены с соответствующими входами формирователя импульса, выход которого соединен с первым входом преобразователя сигналовуг1Ц§рвый и второй выходы которого соединёны ч - соответствующими первым и вторым входами элемента ИЛИ, выход элемента ИЛИ .через декодер соединен с первым входом блока регистров, первый выход и второй вход которого соединены соответсгвенно с вторым входом и выходом блока сравнения, второй выход блока регистров является нлходом устройства, отличаю щ е е с я тем, что, с целью его упрощения, в него введен второй пороговый блок, вход и выход которого с @ соединены соответственно с выходом приемника и третьим входом элемента О) ИЛИ, выход первого порогового блока соединен с вторым входом преобразователя сигналов. N

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для приема избыточнойиНфОРМАции | 1979 |

|

SU824263A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР по заявке № 3416517/18-24, кл | |||

| G | |||

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1984-05-07—Публикация

1983-01-28—Подача