Изобретение относится к импульс-, ной технике и может быть использовано в системах обработки аналоговой информации.

Цель изобретения - расширение об- ласти применения за счет обеспечения независимого управления величиной задержки в каждом из каналов устройства .

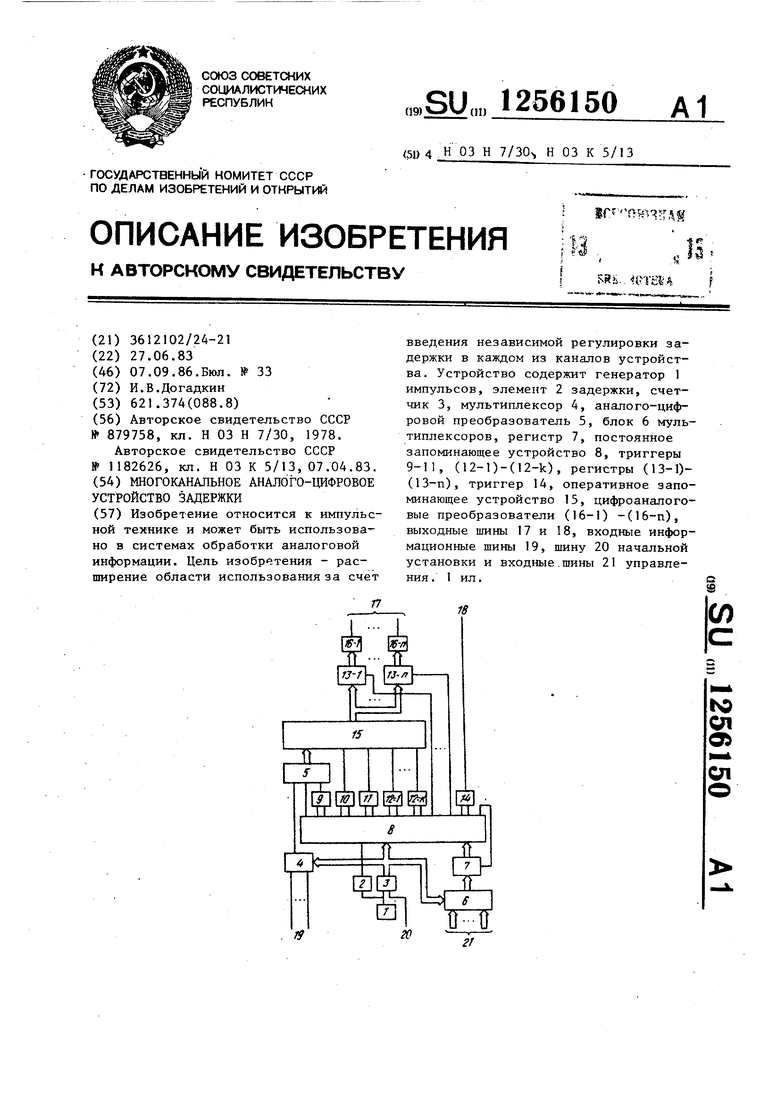

На чертеже представлена функцио- нальная схема устройства.

Многоканальное аналого-цифровое устройство задержки содержит генератор 1 импульсов, элемент 2 задержки, счетчик 3, мультиплексору, ана- лого-цифровой преобразователь 5, блок 6 мультиплексоров, регистр 7, постоянное запоминающее устройство .8, триггеры 9-П, (12-1) -(12-k), регистры (13-1) - (3-п), триггер 14, оперативное запоминающее устройство 15, цифроаналоговые преобразователи (16-1)-(16-п), выходные шины J7 и 18, входные информационные шины 19 шину 20 начальной установки и вуод- ные шины 21 управления.

Выход генератора 1 импульсов соединен с входом элемента 2 задержки .и счетным входом счетчика 3, установочный вход которого подключен к шине 20 начальной установки, а выходы соединены с соответствуюпщми входами управления мультиплексора 4, информационные входы которого соединены с соответствуюпщми входньми шинами 19, а выход подключен к информационному входу аналого-цифрового преобразователя 5. Кроме того, выходы счетчика 3 соединены с соответствующими входами управления блока 6 мультиплексоров, информационные входы которого подключены к соответствующим входным шинам 21 управления, а выходы соединены с соответствую- входами регистра 7, выходь ко- торого подключены к соответствующим адресным входам постоянного запоминающего устройства 8, остальные адресные входы которого соединены соответственно с соответствуюпшми вы- ходами счетчика 3 и элемента 2 задержки. Выходы постоянного запоминающего устройства 8 подключены соответственно к входу синхронизации аналого-цифрового преобразователя 5, к входам триггеров 9-11, (12-l)-(12-k) 14 и к входам синкронизации регистров 7, (13-1)-(13-п). Вход начальной

становки аналого-цифрового преобраователя 5 подключен к выходу тригера 9, а выходы - к соответствуюим информационным входам оперативного запоминающего устройства 15, вход синхронизации которого подключен к выходу триггера 10. Вход управления ежимом работы оперативного запоминащего устройства 15 соединен с выходом триггера 11, адресные входы - соответственно с выходами триггеров (12-l)-(12-k), а выходы подключены к соответствуюш 1м информационным входам регистров (13-1)-(13-п), выходы которых подключены к соответствующим входам соответствующих цифроаналого- вых преобрааователей (16-1)-(16-п), выходы которых -соединены с соответствующими выходными шинами 17. Выход триггера 14 подключен к дополнительной выходной шине 18.

Блок 6 мультиплексоров содержит п мультиплексоров, одноименные вхо- д)ы управления которых подключены к соответствующим выводам входов управления блока 6 мультиплексоров, информационные входы мультиплексоров являются информационными входами бло- ка 6 мультиплексоров, а выходы мультиплексоров являются соответствующими выходами блока 6 мультиплексоров . .

Устройство работает следующим образом.

В момент включения устройства импульс начальной установки поступает на установочный вход счетчика 3 и обнуляет его. Импульсный сигнал тактовой частоты с выхода генератора 1 поступает на счетный вход счетчика 3, который осуществляет пересчет импульсов, и на вход элемента 2 задержки, величина задержки которого равна времени переключения триггера младшего разряда счетчика 3. На входы мультиплексора- 4 поступают аналоговые сигналы, задержку которых необходимо осуществить в устройстве. Соответственно, на входы блока 6 ультиплексоров поступают коды величин задержек аналоговых сигналов. Согласованное управление мультиплексо- ром 4 и блоком 6 мультиплексоров осуществляется импульсными сигналами на соответствующих выходах счетчика 3. ,

Таким образом, код величины задержки, поступивший на информационные входы регистра 7 с выходов блока

3

6 мультиплексоров, соответствует аналоговому сигналу « поступившему на информационный вход аналого-цифрового преобразователя 5 с выхода мультиплексора А. Управление работо устройства задержки и согласование сигналов управления во времени осуществляется с помощью постоянного запоминающего устройства 8, каждой комбинации импульсных сигналов на адресных входах которого однозначно соответствует заранее определенная комбинация импульсных сигналов на его выходах, а также с помощью первого 9, второго 10, третьего 11 допел- нительных триггеров, k дополнительных триггеров 12 и триггера. 14, управляемых импульсами на соответствующих выходах постоянного запоминающего устройства 8 и предназначенных для формирования импульсных сигналов с периодом, кратным периоду импульсного сигнала на выходе генератора 1

Запись кода величины задержки в регистр 7 происходит по фронту им- пульса, поступившего на его вход синхронизации с соответствующего выхода постоянного запоминающего устройства 8. С целью исключения неопределенности при записи кода в регистр 7 на выходе триггера 14- формируется сигнал запрета изменения кодов величин задержек аналоговых сигналов на входных шинах 21 управления устройства, длительность которого t , выбирается из условия

. о Ч + 3

где t - время отклика внешнего устройства, формирующего коды величин задержек, на указан ный сигнал;

t - время задержки кода при прохождении через блок 6 мультиплексоров;tj - время записи кода в ре-

гистр 7.

После осуществления записи кода величины задержки в регистр 7 сигнал запрета с выхода триггера 14 снимается .

Аналого-цифровой преобразователь 5 осуществляет преобразование уров- ня аналогового сигнала на его информационном входе в цифровой код. Начальная установка аналого-цифрового преобразователя 5 осуществляется импульсным сигналом на выходе первого дополнительного триггера 9. На

s Ю 520

25 30

Q

5

0

5

5

504

вход синхронизации аналого-цифровогоi преобразователя 5 поступает импульсный сигнал тактовой частоты с соответствующего выхода постоянного запоминающего устройства 8. Запись кода, сформированного на выходах аналого-цифрового преобразователя 5, в оперативное запоминающее устройство 15 осуществляется по адресу, код которого сформирован на выходах k дополнительных триггеров 12. Логический уровень импульсного сигнала на выходе третьего дополнительного триггера., 11 определяет режим работы оперативного запоминающего устройства 15, а импульсным сигналом на выходе второго дополнительного триггера 10 осуществляется выборка оперативного запоминающего устройства 15 в режимах записи и считывания информации.

Код адреса записи информации в оперативное запоминающее устройство 15 формируется с учетом содержимого счетчика 3. Таким образом, каждому аналоговому сигналу на входных информационных шинах 19 устройства задержки соответствуют определенные - ячейки памяти оперативного запоминающего з стройства 15, Б которые последовательно записываются коды уровней соответствующего аналогового сигнала в определенные моменты времени.

Считывание информации из оперативного запоминающего устройства 15 в соответствующий из п регистров 13 осуществляется по адресу, сформированному на выходах k дополнительных триггеров 12, во время формирования кода на выходах аналого-цифрового преобразователя 5. Код адреса считывания информации из оперативного запоминающего устройства 15 формируется с содержимого счетчика 3 и регистра 7. Таким образом, цикл обращения к оперативному запоминающему устройству 15 в каждом канале состоит из считывания и записи информации по соответствующим адресам ячеек памяти, относительное расположение которых определяет величину задержки аналогового сигнала в соответствующем канале устройства.

Между каналами устройства задержки и п регистрами 13 существует взаимно однозначное соответствие. В каждый из п регистров 13 по фронту импульса, поступившего на его вход синхронизации с соответствующего вы+т,

S1256150

ода постоянного запоминающего устойства 8, записывается информация з ячеек памяти оперативного запомиающего устройства 15, соответствуюая одному из каналов устройства заержки. С помощью п цифроаналоговых реобразователей 16, осуществляющих реобразование кодов на выходах п егистров 13 в соответствующие урови сигналов, входные аналоговые сиг- JQ алы воспроизводятся на соответстующих выходных шинах 17 устройства задержками., величины которых, t , аданы кодами на соответствующих ходных шинах 21 управления устрой- ij тва и определяются выражением Р k - Ak

, t :. f

де P - целое положительное число,

определяемое взаимным распо- 20 ложением ячеек памяти для записи и считывания информации в пределах цикла обращения к оперативному запоминающему устройству 15; 25 f - тактовая частота импульсного сигнала на выходе генератора 1 ;

k - количество тактов в цикле

обращения к оперативному за- jo поминающему устройству 15; Ak - количество тактов в интервале между выборками оперативного запоминающего устройства 15 в пределах цикла обращения;

t- время преобразования кода в уровень сигнала в цифроаналоговых преобразователях 16. Величина Р в случае выполнения не- 40 равенства

АЗП А,, где А,п - десятичный код адреса за35

зп

писи информации в оперативное запоминающее устройство 15; Ajy - десятичный код адреса считывания информации из оперативного запоминающего устрой- . ства 15, определяется с помощью выражения

Р А JJ, - А, а в случае выполнения неравенства

А, с помощью выражения

Р N + А,„ - А,,

45

50

55

Ф

ус ти зо ус ци сч по ки ву пл ро вх хо ан вы ве оп ст от ми ка со ще ля ра ми щ ре сп ли ус им му ги ро ст не ме те ве ан вх ро ро хр пр тр вх ци си жи ре

где N - количество ячеек памяти, зарезервированных в оперативQj

0 5

o

0

5

5

0

5

ном запоминающем устройстве 15 под информацию в каналах устройстра задержки.

Формула изобретения

ъ .

Многоканальное аналого-цифровое устройство задержки, содержащее мультиплексор, аналого-цифровой преобразователь, оперативное запоминаю цее устройство, триггер, п регистров, п цифроаналоговых преобразователей и счетчик, установочный вход которого подключен к шине начальной установки, а выхода соединены с соответствующими входами управления мультиплексора, информационные входы которого, подключены к соответствующим входным информационным шинам, а выход соединен с информационным входом аналого-цифрового преобразователя, выходы которого подключены к соответствующим информационным входам оперативного запоминающего устройства, выходы которого соединены с соответствующими информациоины1«1 входами каждого из п регистров, выходы каждого из п регистров подключены к соответствующим входам соответствующего цифроаналогового преобразователя, а п цифроаналоговых преобразователей являются соответствующими выходными пшнами, отличающееся тем, что, с целью расширения области применения за счет обеспечения независимого управления величиной задержки в каждом из каналов устройства, в него введены генератор импульсов, элемент задержки, блок мультиплексоров, дополнительный регистр, (k+S) дополнительных триггеров и постоянное запоминающее устройство, адресные входы которого соединены соответственно с выходами элемента задержки, счетчика и дополнительного регистра, а выходы - соответственно с входом синхронизации аналого-цифрового преобразователя, входами (k+3) дополнительных триггеров, вxoдa ян синхронизации п регистров, входами триггера и входом син- хронизаци т дополнительного регистра, причем выходы (k+3) дополнительных триггеров соединены соответственно с входом начальной установки .аналого- цифрового преобразователя, с входом синхронизации, входом управления режимом работы и соответствующими адресными входами оперативного запоми712561508

нающего устройства, выход триггера ния блока мультиплексоров, выходы является дополнительной выходной ши- которого соединены с информационны- ной, а выход генератора импульсов ми входами регистра, а входы блока подключен к входу элемента задержки мультиплексоров подключены к сооти счетному входу счетчика, выходы ко-5 ветствзпощим входным шинам управления торого подключены к входам управле- задержкой.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровое устройство задержки | 1983 |

|

SU1182626A1 |

| Параллельно-последовательный п-разрядный аналого-цифровой преобразователь с автоматической коррекцией функции преобразования | 1988 |

|

SU1732471A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1988 |

|

SU1594699A1 |

| Формирователь сложной функции | 1982 |

|

SU1107293A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1989 |

|

SU1709526A1 |

| Устройство для воспроизведения аналогового сигнала | 1988 |

|

SU1524175A1 |

| Устройство для воспроизведения запаздывающих функций | 1983 |

|

SU1157552A1 |

| Многоканальное устройство для ввода информации | 1989 |

|

SU1633383A1 |

| Цифровой регистратор повторяющихся сигналов | 1987 |

|

SU1610279A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1985 |

|

SU1305851A1 |

Изобретение относится к импульсной технике и может быть использовано в системах обработки аналоговой информации. Цель изобретения - расширение области использования за счет введения независимой регулировки задержки в каждом из каналов устройства. Устройство содержит генератор 1 импульсов, элемент 2 задержки, счетчик 3, мультиплексор 4, аналого-цифровой преобразователь 5, блок 6 мультиплексоров, регистр 7, постоянное запоминающее устройство 8, триггеры 9-11, (12-l)-(2-k), регистры (13-1)-

| Дискретно-аналоговое устройство задержки | 1979 |

|

SU879758A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аналого-цифровое устройство задержки | 1983 |

|

SU1182626A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-09-07—Публикация

1983-06-27—Подача