1107315

чем третий выход дешифратора подсое- которых подключены к выходам первого динен к первый входам третьего и и второго перемножителей соответственчетв ертого интеграторов, вторые входы но.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для тактовой синхронизации | 1984 |

|

SU1305885A1 |

| Устройство для квазикогерентного приема фазоманипулированных сигналов | 1984 |

|

SU1239885A1 |

| Устройство для тактовой синхронизации | 1989 |

|

SU1642591A1 |

| Устройство тактовой синхронизации | 1988 |

|

SU1589414A2 |

| Устройство синхронизации шумоподобных сигналов | 1979 |

|

SU879802A2 |

| Частотный дискриминатор | 1988 |

|

SU1676078A2 |

| ДВУХПРОВОДНАЯ ДУПЛЕКСНАЯ ЦИФРОВАЯ СИСТЕМА ПЕРЕДАЧИ С ВРЕМЕННЫМ РАЗДЕЛЕНИЕМ | 1991 |

|

RU2037966C1 |

| Следящий приемник асинхронных шумоподобных сигналов | 1986 |

|

SU1403381A1 |

| Устройство синхронизации псевдослучайных сигналов | 1988 |

|

SU1596476A1 |

| Анализатор сигнала тактовой синхронизации | 1988 |

|

SU1587656A1 |

УСТРОЙСТВО ТАКТОВОЙ СИНХРОНИЗАЦИИ, содержаш.ее последовательно соединенные генератор тактовых импульсов, блок управления, делитель частоты и дешифратор, первый выход которого подсоединен к первым входам перЕОГо и второго интеграторов, вторые входы которых подключены к выходам первого и второго перемножителей соответственно, первые входы которых объединены и являются информационным входом устройства, а вторые входы подключены к соответствующим выходам генератора гармонических колебаний, выход первого интегратора через последовательно соединенные первый блок памяти и первый квадрагор подсоединен к первому входу первого сумматора, к второму входу которого подсоединен выход второго интегратора через последовательно соединенные второй блок памяти и второй квадратор, выход первого интегратора через третий квадратор пoдcoJeдииен к первому входу второго сумматора, к второму входу которого подсоединен выход второго интегратора через четвертый квадратор, при этом выход второго сумматора через последовательно соединенные первый инвертор и третий сумматор подсоединен к первому входу первого блока определения знака, к второму входу которого подключен второй выход дешифратора, а к второму входу третьего сумматора - зыход первого сумматора, отличаю щеся тем, что, с целью повьпиения точности синхронизации, в него введены последовательно соединенные четвертый сумматор, второй блок определения знака, элемент g И и элемент ИЛИ, последовательно соединенные второй инвертор, пятый (Л сумматор и третий блок определения знака, последовательно соединенные третий интегратор, третий блок памяти, пятый квадратор и шестой сумматор, и последовательно соединенные четвертый интегратор, четвертый блок памяти и шестой квадратор, выход которого подсоединен к второму входу шестого сумматора, выход которого 10 подсоединен к второму входу пятого сумматора и первому входу четвертого :л сумматора, к второму входу которого подключен выход первого инвертора, при этом, выход первого сумматора подсоединен к входу второго инвертора, выход первого блока определения знака через элемент ИЛИ - к второму входу блока управления, а второй выход дешифратора - к второму входу второго блока определения знака и второму входу третьего блока определения знака, выход которого подсоеди.иен к второму входу элемента И, при

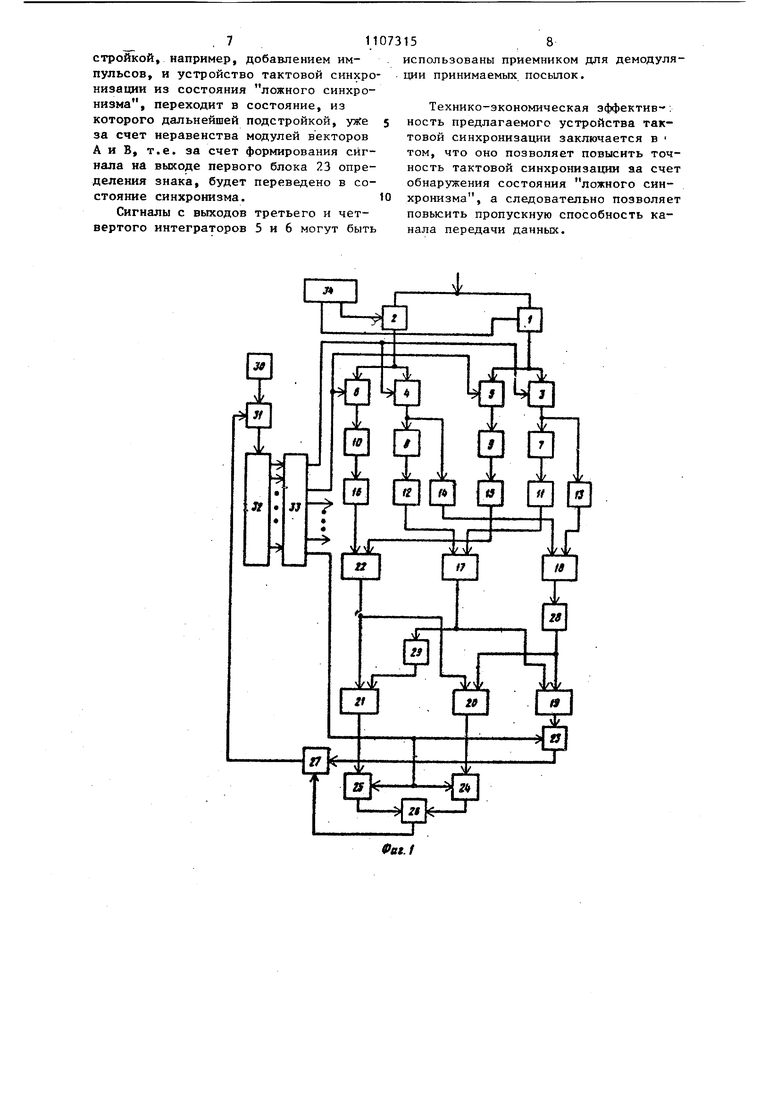

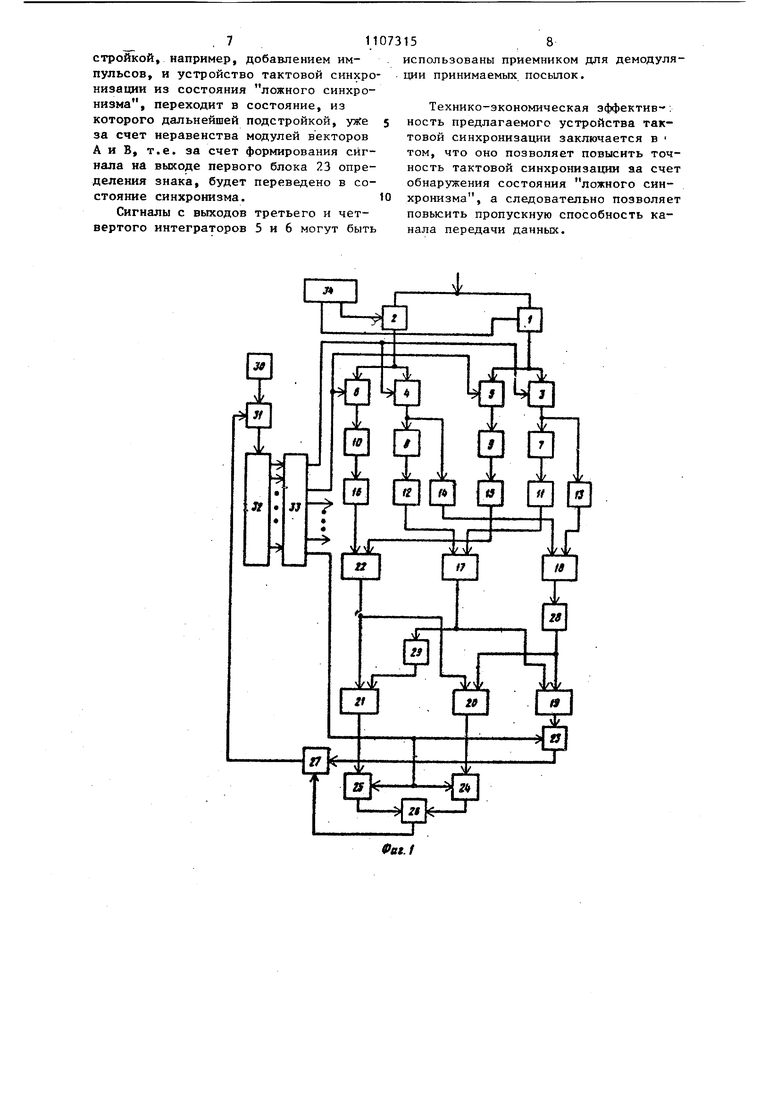

Изобретение относится к технике связи и может быть использовано для синхронизации передаваемой дискретИой информации по дискретньгм каналам Известно устройство тактовой синхронизации, содержащее две цепи, каж дая из которых содержит последовательно соединенные коммутируемьп фильтр и амплитудный детектор, выход каждого из которых подсоединен к соответствукяцему входу первого блока вычитания, выход которого через последовательно соединенные бло добавления - вычитания, делитель ча тоты и блок формирования синхросигнала подключены к первым входам ком мутируемых фильтров обеих цепей, вт рые входы которых объединены и подключены к выходу второго вычитателя к первому входу которого подключен выход блока вьщеления служебного сигнала, вход которого объединен с вторым входом второго вычитателя и является входом устройства. С11. Устройство тактовой синхронизации осуществляет непосредственно ми мизацию переходных помех, чем и обе печивается тактовая синхронизация. Недостатком устройства является то, что оно допускает состояние лож ного синхронизма, при котором границы посыпок располагаются точно посередине между моментами времени предполагаемых границ посыпок. Наиболее близким к предлагаемому является устройство тактовой синхронизации, содержащее последователь но соединенные генератор тактовых им пульсов, блок управления, делитель частоты и дешифратор, первый выход которого подсоединен к первым входам первого и второго интегратора, вторы входы которых подключены к выходам первого и второго перемножителей соответственно, первые входы КОТОРЫХ объединены и являются информационным входом устройства, а вторые входы подключены к соответствуклцим выходам генератора гармонических колебаний, выход первого интегратора через последовательно соединенные первый блок памяти и первый квадратор подсоединен к первому входу первого сумматора, к второму входу которого подсоединен вькод второго интегратора через последовательно соединенные второй блок памяти и второй квадратор, выход первого интегратора через третий квадратор подсоединен к первому входу второго сумматора, к второму входу которого подсоединен выход второго интегратора через четвертый квадратор, при зтом выход второго сумматора через последовательно соединенные первый инвертор и третий сумматор подсоединен к первому входу первого блока определения знака, к второму входу которого подключен второй выход дешифратора, а к второму входу третьего сумматора подключен выход первого сумматора, причем выход первого блока определения знака подсоединен к второму входу блока управления Г23. Недостатком известного устройства тактовой синхрониза1даи является то, что оно допускает состояние ложного синхронизма, которое характеризуется равенством усредненных значений напряжений, снимаемых с выходов первого и второго интеграторов при расположении границ посылок посередине между тактами, отмечакяцими границы посыпок в приемнике, т.е. при отсуствии синхронизма. Равенство указанных значений напряжений определяется в устрой стве тактовой синхронизации как состояние синхронизма и сигнал на подстройку тактов не формируется. Состояние ложного синхронизма вляется неустойчивым, но поснольку правляющее воздействие для подстройи тактов формируется с усреднением, лабые случайные воздействия с нулевым средним значением могут и не вывести систему из ложного синхронизма. Достаточно сильное помеховое воздействие или же разность тактовых частот передатчика и приемника в ито re выводит систему из состояния лож ного синхронизма. Однако и помеха и разность тактовых частот - параметры случайные, поэтому время пребывания системы в состоянии ложного син хронизма случайно и в принципе может длиться неопределенно долго. Чем лучше условия (слабая помеха, расхождение тактовых частот очень мало) тем более вероятно продолжительное пребьтание системы в состоянии ложного синхронизма. Оказаться в этом состоянии система может при вхождений в связь (увеличивается время вхождения в связь) или при перерывах в каналах связи (увеличивается время пер рьгаов передачи). Цель изобретения - повышение точности синхронизации. Для достижения поставленной цели в устройство тактовой синхронизации, содержащее последовательно соединенные генератор тактовых импульсов, бл управления, делитель частоты и депшф paTot, первый выход которого подсоединен к первым входам первого и втор го интеграторов, вторые входы которы подключены к выходам первого и второго перемножителей соответственно, первые входы которых объединены и являются информационным входом устройства, а вторые входы подключены к соответствующим выходам генератора гармонических колебаний, выход первого интегратора через последовательно соединенные первый блок памят и первый квадратор подсоединен к пер вому входу первого сумматора, к второму входу которого подсоединен выход второго интегратора через последовательно соединенные второй блок памяти и второй квадратор, выход пер вого интегратора через третий квадратор подсоединен к первому входу второго сумматора, к второму входу которого подсоединен выход второго интегратора через четвертый квадратор, при этом выход второго сумматора через последовательно соединенные первый инвертор и третий сумматор подсоединен к первому входу первого блока определения знака, к второму входу которого подключен второй выход дешифратора, а к второму входу третьего сумматора подключен выход первого сумматора, введены последовательно соединенные четвертый сумматор, второй блок определения знака, элемент И и элемент ИЛИ, последовательно соединенные второй инвертор, пятый сумматор и третий блок определения знака, последовательно соединенные третий интегратор, третий блок памяти, пятый квадратор и шестой сумматор, и последовательно соединенные четвертый интегратор, четвертый блок памяти и шестой квадратор, выход которого подсоединен к второму входу шестого сумматора, выход которого подсоединен к вторюму входу пятого сумматора и первому входу четвертого сумматора, к второму входу которого подключен выход первого инвертора, при этом вькод первого сумматора подсоединен к входу второго инвертора, выход первого блока определения знака через элемент ИЛИ к второму входу блока управления, а второй выход дешифратора - к второму входу второго блока определения знака и второму входу третьего блока определения знака, выход которого подсоединен к второму входу элемента И, причем третий выход дешифратора подсоединен к первым входам третьего и четвертого интегратора, вторые входы которых подключены к выходам первого и второго перемножителей соответственно. На фиг. 1 представлена структурноэлектрическая схема устройства тактовой синхронизации, на фиг. 2 - диаграмма расположения интервалов интегрирования для вычисления квадраторов модулей векторов соседних посыпок. I Устройство тактовой синхронизации содержит первый и второй перемножители 1 и 2, первый, второй, третий и четвертый интеграторы 3-6, первый, второй, третий, четвертый блоки 7-10 памяти, первый, второй, третий, четвертый,- пятый и шестой квадраторы 11-16, первый, второй, третий, четвертый, пятый и шестой сумматора 17-22, первый, второй и третий блоки 23-25 определения знака,- элемент И 26, элемент ИЛИ 27, первый и второй инверторы 28 и 29, генератор 30 тактовых импульсов, блок 31 управления, делитель 32 частоты, дешн5фратор 33 и генератор 34 гармоничес ких колебаний. Устройство тактовой синхронизации работает следуюгцим образом. Сигнал подается на информационH} ie входы первого и второго перемно жителей 1 и 2, на вторые входы которых подаются гармонические колебания с генератора 3 гармонических колебаний. Перемноженные сигналы по ступают на первый, второй, третий и четвертый интеграторы 3-6, причем начало и окончание интегрирования сигналов определяется поступлением с дешифратора 33 тактов Т (фиг. 2 на первый и второй интеграторы 3 и 4 и тактов Т (фиг. 2cf) на третий и четвертый интеграторы 5 и 6. Такты Тц соответствуют в состоянии синхронизма границе посьшок, а Т середи не посылок. В моменты поступления тактов Т с выходов третьего и четвертого интеграторов 5 и 6 снимаются отсчеты постоянных напряжений, соответствующие величинам (фиг. 2 ) X с. Js(t) 5.1П «о tcH ) ,. j-s()tcH и поступают в третий и четьертый бл ки 9 и 10 памяти. В моменты поступления тактов Т с выходов первого и второго интеграторов 3 и 4 снимаю ся отсчеты постоянных напряжений, c ответствующие величинам (фиг. 2б) f-Vf/i .Js6.)sln(fi)tof-(: i 1 tvz (:t)cos ui)t di.. В эти же моменты времени (в моменты тактов Т) на выходе первого и второго, блоков 7 и 8 памяти присутству ют напряжения отсчетов, соответству щие величинам (фиг. 2г) .Vi s(i)sinuirtcH. i Д/2. ., j8)cosaJtaH Т.е. снятые с выходов первого и вто рого интеграторов 3 и А на время Т ранее, а на выходе третьего и четвертого блоков 9 и 10 памяти - напряжения, соответствующие величинам Lj, . 156 Затем с помощью первого, второго, третьего, четвертого, пятого и шестого квадраторов 11-16 и первого, второго и третьего сумматоров 17-18 в соответствии с формулами xl+yi , ci xj+4l вычисляются квадраты модулей векторов С, Аи В. Разности квадратов векторов (В А-) (С2- в2-) и (С А2) определяются четвертым,, пятым и шестым сумматорами 20-22. Для получения разностей квадратов -вектором первый и второй инверторы 28 и 29 инвертируют квадраты векторов . Знак разности квадратов (В А), определяемый первым блоком определения знака 23, характеризует направление подстройки фазы синхроимпульсов. В зависимости от знака величины (в А) блок 31 управления либо вычитает один импульс из последовательности, поступающей на вход делителя 32 частоты, уменьшая фазу, либо прибавляет один импульс, увелич1 з.-п фазу. Знаки разностей квадратов ( ) , ( ) определяемые вторым и третьим блоками 24 и 25 определения знака при условии /С - А О, Ic - В О,(5) характеризуют состояние синхронизма. При одновременном выполнении неравенств 5 условия элементы И 26 ИЛИ 27 пропускают импульс однонаправленной постоянной подстройки в блок 31 управления. Кевьшолнение условия 5 характеризует состояние ложного синхронизма и знаки разностей квадратов усредненных значений модулей векторов С А В определяют направление подстройки фазы блока 31 управления. Усреднение во времени в предлагаемой схеме достигается за счет малого шага подстройки. Случайные вьшолнены неравенств 5, например, при импульсной помехе, приведут лишь к незначительному сдвигу фазы тактовых импульсов и вслед за этим сдвиг будет компенсирован устройством тактовой синхронизации. Относительная величина шага подстройки определяется коэффициентом деления делителя 32. Постоянное вьтолнение неравенств 5 сопрововдается однонаправленной постоянной подстройкой, например, добавлением импульсов, и устройство тактовой синхро низации из состояния ложного синхронизма, переходит в состояние, из которого дальнейшей подстройкой, уже за счет неравенства модулей векторов А и В, т.е. за счет формирования сигнала на выходе первого блока 23 определения знака, будет переведено в состояние синхронизма. Сигналы с выходов третьего и четвертого интеграторов 5 и 6 могут быть спользованы приемником для демодуляии принимаемых посылок. Технико-экономическая зффектив : ность предлагаемого устройства тактовой синхронизации заключается в том, что оно позволяет повысить точность тактовой синхронизации аа счет обнаружения состояния ложного синхронизма, а следовательно позволяет повьюить пропускную способность канала передачи данных.

-% О rl2 Г зт1г

ut.2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Гинзбург В.В., Каяцкас А.А | |||

| Теория синхронизации демодуляторов | |||

| М., Связь, 1974, с | |||

| Способ применения резонанс конденсатора, подключенного известным уже образом параллельно к обмотке трансформатора, дающего напряжение на анод генераторных ламп | 1922 |

|

SU129A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Заездный A.M., Окунев Ю.Б., Рахович Л.М | |||

| Фазоразностная модуляция | |||

| М., Связь, 1967, с | |||

| Тепловой измеритель силы тока | 1921 |

|

SU267A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-08-07—Публикация

1983-01-10—Подача