pa 11-14, три сумматора 15-17, инвертор 18, блок 19 определения злака, блоки 20 и 21 совпадения знаков, эл-т 3 ИЛИ 22J г-р 23 тактовых импуль15

1

Изобретение относится к технике связи и может быть использовано для синхронизации передаваемой дискретной информации по дискретным каналам.

Цель изобретения - упрощение уст- 5 ройства путем исключения двух блоков памяти, двух квадраторов, трех сумматоров, инвертора,двух блоков определения знака и элемента И.

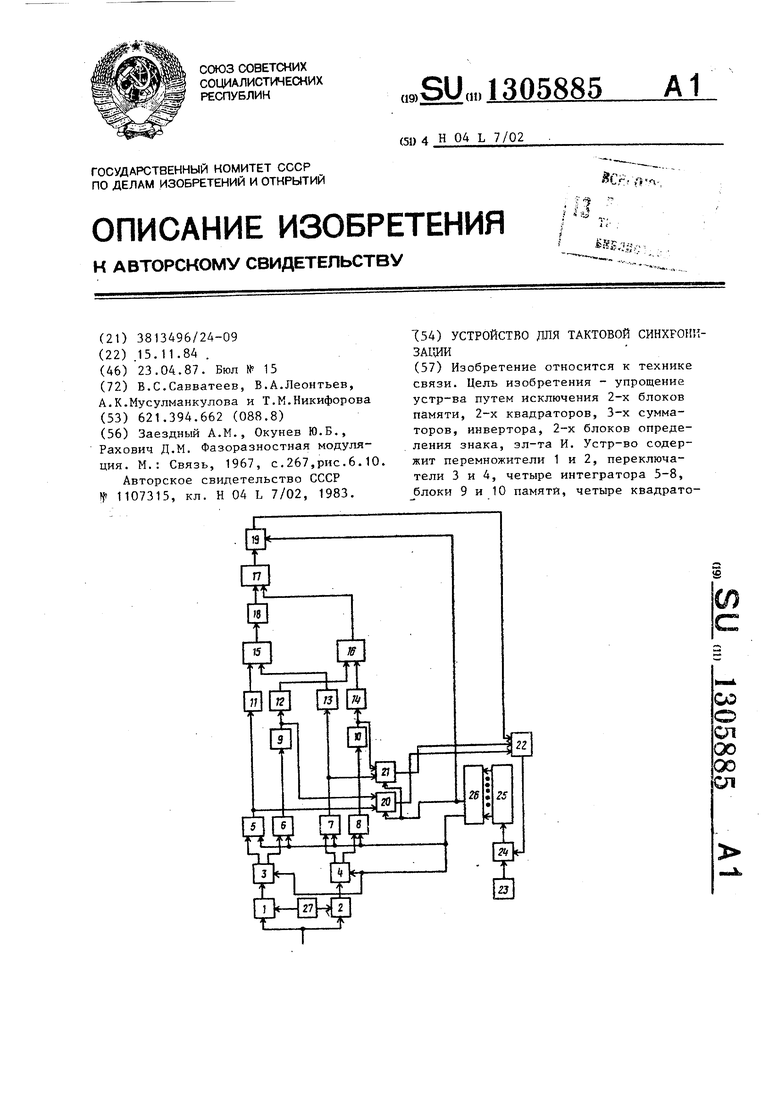

На чертеже изображена схема пред- лагаемого устройства.

Устройство для тактовой синхронизации содержит первый 1 и второй 2 перемножители, первый 3 и второй 4 переключатели, первый 5, второй 6, третий 7 и четвертый 8 интеграторы, первый 9 и второй 10 блоки памяти, первый 11, второй 12, третий 1.3 и четвертый 14 квадраторы, первый 15,второй 16 и. третий 17 сумматоры, инвер- , тор 18, блок 19 определения знака, первый 20 и второй 21 блоки совпадения знаков,элемент ЗИЛИ 22, генератор 23 тактовых импульсов, блок 24 добавления и вычитания импульсов, делитель 25 частоты, дешифратор 26 и генератор 27 гармонического колебания.

Устройство для тактовой синхронизации работает следующим образом.

30

Сигнал подается на первые входы

(информационные) первого 1 и второго 2 перемножителей, на вторые входы которых поступают соответственно синфазный и квадратурный гармонические сигналы с выходов генератора 27 гар- 5 монических колебаний. Полученные та- ким образом на выходах первого 1 и второго 2 перемножителей сигналы поступают на сигнальные входы первого 3 и второго 4 переключетелей, ко- торые по тактовьп-1 сигналам с дешифратора 26 коммутируют их на второй 6 и четвертый 8 или на первый 5 и тре- тир1 7 интеграторы соответственно. Причем, коммутация на второй 6 и четвер-

сов, блок 2Д добавления и вычитания импульсов, делитель 25 частоты, дешифратор 26, г-р 27 гармонического колебания. 1 ил.

5

,

0

5

тый 8 интеграторы осуществляется во время первой половины посылки, т.е. от О до , а на первый 5 и третий 7 интеграторы - во время второй половины посылки, т.е. от до Т . Сброс напряжения, накопленного интеграторами, осуществляется также тактовыми сигналами с дешифратора 26. При этом накопленные значения напряжения перед моментом сброса на выходах второго 6 и четвертого 8 интеграторов соответствуют проекциям первой половины посылки на координатные оси:

Хр Зд S(t) sincO t dt, Y (t) cos ( dt,

FV О

Ha выходах первого 5 и третьего 7 интеграторов напряжения соответствуют проекциям второй половины посылки на координатные оси

Тп

s rnt i ) si t-dt, Уд S(t:) cosoJ t dt.

Сигналы с выходов второго 6 и четвертого 8 интеграторов задерживаются . на t Thiz в первом 9 и втором 10 блоках памяти, и в момент t Т одновременно с сигналами с выходов первого 5 и третьего 7 интеграторов поступают на входы квадраторов 12, 14, 11 и 13 соответственно. После возведения этих сигналов в квадрат первым 15 и вторым 16 сумматорами формируются сигналы, пропорциональные квадратам модулей векторов половин посылок, на выходе первого сумматора 15 сигнал соответствует

В Х| ч- У|, и на выходе второго сумматора 16

А - У1.

Сигнал с выхода первого сумматора 15 инвертируется инвертором 18

и на выходе третьего сумматора 17 образуется сигнал рассогласования, определяемый как разность квадратов векторов половин посылки

R А - В ,

Знак полученного рассогласования характеризует направление подстрой- |ки, он анализируется в момент окончания посылки блоком 19 определения знака. Сигнал, соответствующий тому или иному знаку рассогласования, поступает через элемент ЗИЛИ 22 на второй вход блока 24 добавления и вычитания импульсов, при этом из последовательности импульсов генератора 23 тактовых импульсов, поступающих на первый вход блока добавления и вычитания импульсов, вычтется-. один импульс или в нее добавится один импульс, в зависимости от сигнала рассогласования. При этом на выходах делителя 25 частоты возникает комбинация, соответствующая смещению границ интегрирования, которая дешифрируется дешифратором 26, на соответствующих выходах которого изменяется время формирования тактовых импульсов.

Если же система находится в состоянии ложного синхронизма, то на выходе блока 19 определения знака не вырабатывается сигнал рассогласования. В этом случае, сигналы пропорциональные проекциям модулей половин посылок Х, У, Х, Y , поступающие на первый 20 и второй 21 блоки совпадения знаков, на выходах хотя бы одного из блоков не совпадут по знаку, несовпадение также может произойт и на входах обоих блоков 20 и 21 совпадения знака одновременно. При этом на выходе одного из блоков 20 и 21 совпадения знаков или на выходах обоих блоков одновременно сформируется единичный импульс, который пройдет через элемент ЗИЛИ 22 на второй вход блока добавления и вычитания импульсов, вызывая подстройку, нап

ример, добавлением импульса, выводя тем самым систему из состояния ложного синхронизма.

Формула изобретения

Устройство для тактовой синхронизации, содержащее два перемножителя, первые входы которых объединены и яв5

О

25

0

5

ляются информационным входом устройства, а вторые входь; подключены соответственно к квадратурным выходам генератора гармонического колебания, а также первый, второй, третий и четвертый интеграторы, первый блок совпадения знаков, первый и второй блоки памяти, первьм, второй, третий и четвертый квадраторы, первый, второй и третий сумматоры, инвертор, блок определения знака и последовательно Соединенные генератор тактовых импульсов, блок добавления и вычитания импульсов, делитель частоты и дешифратор, первый выход которого Iподключен к первым входам первого и второго интеграторов, при этом выходы второго и четвертого интеграторов соответственно черев первьй и второй блоки памяти подключены к входам второго и четвертого квадраторов, выходы которых подключены к входам второго сумматора, а выходы первого и третьего квадраторов подключены к входам первого сумматора, выход которого через инвертор подключен к первому входу третьего сумматора, к второму входу которог о подключен выход второго сумматора, при этом выход третьего сумматора подключен к первому входу блока определения знака, к второму входу которого подключен второй выход дешифратора, отличающее-- с я тем, что, с целью упрощения устройства путем исключения двух блоков памяти, двух квадарторов трех сумматоров, инвертора, двух блоков определения знака и элемента И, введены два переключателя, второй блок совпадения знаков и элемент 3: ЗИЛИ выход которого подключен к второму входу блока добавления и вычитания импульсов, при этом выходы первого и второго перемножителей подключены к сигнальным входам первого и второго переключателей, к управляющим входам которых и первым входам третьего и четвертого интеграторов подключен первый вь;ход дешифратора, второй выход которого подключен к первым входам первого и второго блоков совпадения знаков, выходы которых подключены к первому и второму входам элемента , к третьему входу которого подключен выход блока определения знака, причем первый и второй выходы первого

5 13058856

л второго переключателей подсоедине-первого блока совпадения знаков, к

ны к вторым входам соответственнотретьему входу которого подключен

первого и второго интеграторов, авыход первого блока памяти, а выход

первый и второй выходы второго пере-третьего интегратора подключен к

ключателя подсоединены к вторым вхо- 5входу третьего квадратора и второму

дам соответственно третьего и чет-входу второго блока совпадения знавертого интеграторов, при этом выходков, к третьему входу которого

первого интегратора подключен к входуподключен выход второго блока

первого квадратора и второму входупамяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство тактовой синхронизации | 1983 |

|

SU1107315A1 |

| Устройство тактовой синхронизации | 1988 |

|

SU1589414A2 |

| Устройство для тактовой синхронизации | 1989 |

|

SU1642591A1 |

| Устройство тактовой синхронизации | 1978 |

|

SU771897A2 |

| Устройство для квазикогерентного приема фазоманипулированных сигналов | 1984 |

|

SU1239885A1 |

| Устройство тактовой синхронизации | 1982 |

|

SU1172046A1 |

| Устройство контроля каналов связи | 1988 |

|

SU1578820A1 |

| Устройство тактовой синхронизации | 1985 |

|

SU1332552A1 |

| Анализатор сигнала тактовой синхронизации | 1988 |

|

SU1587656A1 |

| Устройство для когерентной обработки фазоманипулированных сигналов | 1983 |

|

SU1131037A1 |

Изобретение относится к технике связи. Цель изобретения - упрощение устр-ва путем исключения 2-х блоков памяти, 2-х квадраторов, 3-х сумматоров, инвертора, 2-х блоков определения знака, зл-та И. Устр-во содержит перемножители 1 и 2, переключатели 3 и 4, четыре интегратора 5-8, Jблoки 9 и 10 памяти, четыре квадрато

| Заездный A.M., Окунев Ю.Б., Рахович Д.М | |||

| Фазоразностная модуляция | |||

| М | |||

| : Связь, 1967, с.267,рнс.6.10 | |||

| Устройство тактовой синхронизации | 1983 |

|

SU1107315A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1987-04-23—Публикация

1984-11-15—Подача