00 4:: 00

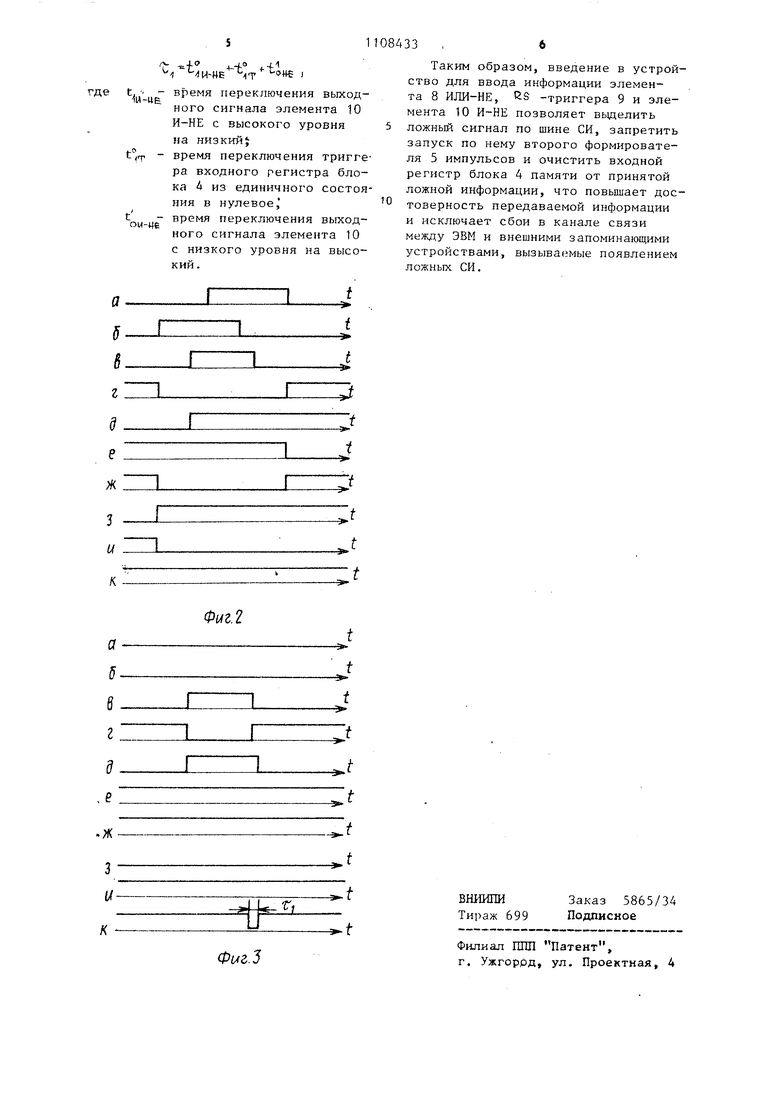

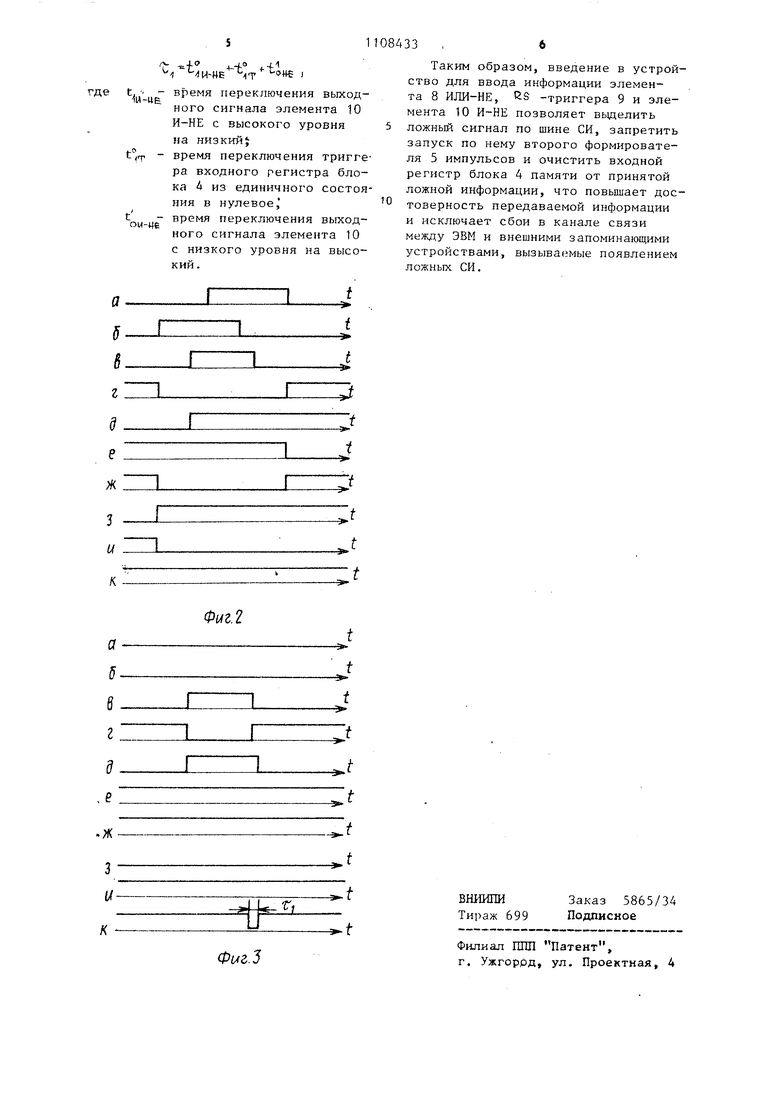

00 Изобре7чм И« огнос;11гс.я к цифровой вычислк тег г. и Nfo/Kt T быть использов;и1О ,ц.чя прода с внешних -ianoMJinaionu ;-; устройств в электроилую иьрптсли елыгую fviauiHHy, По основному ajT.cn. N 1032446 известно ycTpijfiCTFK для ввода информации, со;.г, последоват ельио coiUuiiieifHiiie блок считыпапня, блок уси.чптелсй, йо1)мировлтел з импульсов и б.чок буфериспт памяти, входы блока сч1г.гюгк-)ня янляются входами устройства, ПТОР1.1Й фи-ормирователт, импульсов, Н1ЛХОД к«тор(,1г-о соединен с другим входе -; бу.ф(:рной , одни выходы которого яиляются ныходами устройства, эле;м.н Г, ИЛИ-НЕ и , выход которогО coeJ.uiHeH с зу. второго фсрмирспатсля импульсов, пер пый вход элеглента li-FtE соединен с выходом элемента ИЛИ-НЕ, второй вход соединен с другим Р,ЫХОЛ, блока буферной пам;;ти, входы э.аемента И.Г1И-1 Е соединеиь с пг,1хол,а.г-1И нем лого фо1)миро вателя импульсог II. Недостатком ишим:- гпого устройства является то, что и с.луч.с появления ложного сигнала на пмне синхроимпуль са (СН) устройство выгтолн)гт очередной рабочий л,икл. Так как при иноде информации каналс)М свя-.И вел,ется нод счет количества )зг(л,е,нл1,Х сггси, ложный рабочий н.икл1 н. измел е1п-ге состояния счетч1 ка ,епных слон. Это приведет к . что ка.чал связи прекратит прием ил()ормаци11 раны1:е, чем внеплгее уСтг-.oihrHO .м. ткло информа н.ию, Цель )е11:л(я - повьипенио надежности усПюГч.тг, iiyif -- устра1 ен1 я в;н-1ялия ло),;х сп)иа;гон по входу синх эопмпульг;а. 1оставле;; ая цель /uCTHj-aeio; тем что в уг,1;5оГ1сГ5Н1 ;.. чвол,Г inKJiopMa- ции введегг, ИГС,Ч1)| 1лемент , триггер и BTopoff эле.меш . которого сое/инен с л.ополиите.чьнллм управля1оп1им входоь блока na-ryiTu, а первый BXOji cotviMiCii с пергл.гм гл-лходом триггера, -нх1)п, которого соеди неп с выходом второго |Ьорми1эователя импул1,сов, вход которого сое и::ен с вторым вход,ом iijoporo )леме1гга И-If третий вход Koioporo C(ie, с выходом первого );-1емен -а вертый вход uTopoio -тле с третьим входом rreijBoro элемента И11Е, а и -пход соединен с выходом второге; э.лемента ИЛИ-11Е, входы которого соединены с соответствую1щ-1ми выходами первого формирователя импульсов . На фиг. 1 представлена структурная схема устройсчва, на фиг. 2,3 IjpeMeinuiie диаграммы, поясняющие работу уст)ойстпа. Устройство содержит последовательно соединенные блок 1 считывания, блок 2 ус1-иП1те.лей, блок 3 - первый (Ьормирователь импульсов, блок 4 памяти, В1лполнсм(ньш на обычных регистрах, единичный выход триггера входного регистра блока 4, храня 11его СИ, соединен с другим выходом блока 4, входы блока 1 являются входами устройс1л а, блок 5 - гггорой формироваIe.in, пмпу.ггьсов, выход которого соеЛ, с другим входом блока 4, одни ВЫХОД -; которого ЯВЛЯЮТСЯ выходами устройства, первьй элемент 6 ИЛИ-НЕ, члемепт И-ПЕ 7, второй злеMeiiT 8 ИЛИ-НЕ, триггер 9, К. -вход кото)ого соеди 1е с гилходом блока 5, S-иход - с В1ЛХОДОМ элемента 8 ИЛИ-НЕ ; (п-1)-й вход которого соеди 1е 1 с соответствующими входами элеме а 6 ИЛИ-fIE, прямой выход триггера 9 соеди 1еп с третьим входом элеме та 7 И-11Е, второй элеме {Т 10 И-НЕ. На фиг. 2 представлена врс метнтая диаграмма работы устройства при ввод,е по, 1-1ифо :)мации J на фиг. 3 - (;ниая (иаграмма работь устройства при появ. ложного СИ, На фиг. 2 1 3 приняты следу П1ци(. обозначе {ия: а - кодовый импульс, максимально отстакмдий от CHj б - кодов)Й импульс, максим;шь о опере. СИ в - Cli; г - выход элемента 6 ИЛИ-Н ; /, - j,pyroi , блока 4 памят1-г; с - выход элемента 7 , ж - выход г) 8 ИЛИ-НЕ з - 1рямоГ( в)1ход триггера 9 и - инвepc ь й выход триггера 9; - элемента 10 И-НЕ. Устройство работает следу ои1им образом. Для удобства изложения примем, что из г ходов устройства п-1 явяются кодовь мп, т.е. по ним поступает И формап,ия вместе с контрольным разрядом. На вход с номером h посту 1ает СИ. , счпта П1 1 е блоком 1 , по VT шинам поступа от через б.чок 2 ус гителей на вход) первого формирователя 3. TlepBbtjj формирователь 3 формирует прямоугольные сигна лы, длительность которых выбирается таким образом, чтобы кодовый импульс (фиг. 2сГ) , максимально опередающий СИ, сопровохсдаюгций информацию (фиг.25), своим задним фронтом надеж но перекрывал передний фронт кодового импульса, максимально отстающего от СИ (фиг, 2ci) . С выходов формирова теля 3 кодовые сигналы и СИ поступают на входы установки в единичное состояние триггеров входного регистра (не показан) блока 4 памяти и запоминаются в них. Одновременно сигналы с выхода формирователя 3 поступают на п входов элемента 6 ИЛИ-НЕ и на п -1 вход элемента 8 ИЛИ-НЕ. На входы элемента 8 поступают только кодовые сигналы вместе с контрольным разрядом. До появпечия хотя бы одного импульса на входах элементов 6 и 8 на их выходах поддерживается сигнал высокого уровня. С приходом на выходы элементов 6 и 8 хотя бы одного сигнала уровень сигналов на их выходах станет низким и останется в этом состоянии до окончания входного сигнала. Таким образом, как видно из временной диаграммы (фиг. 22- ,Ж) в течение времени от переднего фронта кодового импульса (фиг. 2ЕГ)до заднего (фиг. 2 ) сигнал на выходах элементов 6 и 8 ИЖ-Н остается низким (фиг. 2г ,w). С появ лением на выходе формирователя 3 СИ устанавливается в единичное состояние триггер входного регистра блока памяти, храняиип СИ. Сигнал с единичного выхода триггера входного регистра, хранящего СИ в блоке 4 памят поступает на другой выход блока 4 па мяти, соединенный с входом элемента 7 И-НЕ (фиг. 2о). Отрицательный перепад с выхода элемента 8 ИЛИ-НЕ поступает на 3 -вход триггера 9 и устанавливает этот триггер в единичное состояние (фиг. 2). Положительный сигнал с прямого выхода триг гера 9 поступает на вход элемента 7 И-НЕ. После окончания кодового сигнала, максимально отстающего от СИ, уровень сигнала на выходе элемента 6 ИЛИ-НЕ снова становится выс ким. Д момент совпадения высоких уро ней на входах элемента 7 И-НЕ сигнал на его выходе низкий. Отрицательный перепад с выхода элемента 7 поступа ет на вход формирователя 5, который по отрицательному перепаду начинает свою работу, т.е. формирует импульсы, которые поступают на первый вход блока 4 памяти, R -вход триггера 9 и обеспечивают перепись информации с входного регистра блока 4 на другие регистры этого блока, обнуление входного регистра блока 4 и триггера 9 и т.д. Как видно из временной диаграммы (фиг. 2), на входах элемента 10 И-НЕ совпадения высоких уровней сигнала не происходит, поэтому на его выходе сохраняется высокий уровень сигнала. При появлении на шине ложного СИ (фиг. 3) устройство работает следующим образом. Сигнал на выходе элемента 6 ИЛИ-НЕ низкий и сохраняется на этом уровне до окончания СИ. СИ запоминается на триггере входного регистра блока 4, и на другом выходе этого блока появляется сигнал (фиг. Зс: . На входы элемента 8 ИЛИ-НЕ СИ не поступает, поэтому триггер 9 остается в нулевом -состоянии. На вход элемента 7 И-НЕ с прямого выхода триггера поступает сигнал низкого уровня, поэтому независимо от изменений сигналов на входах на выходе элемента 7 И-НЕ сигнал имеет высокий уровень (фиг. Зе). Следовательно, при кзличии только одного СИ формирователь 5 не начинает свою работу. К моменту окончания ложного СИ на входах элемента 10 И-НЕ уже присутствуют сигналы с высоким уровнем (фиг. Зс,е,и). С окончанием СИ на выходе элемента 6 ИЛИ НЕ уровень сигнала высокий (фиг. Зг). Этот уровень поступает на вход элемента 10 И-НЕ. С этого момента на всех входах элемента 10 И-НЕ уровень сигналов высокий и сигнал на его выходе становится низким (фиг. 3t). Отрицательный перепад с выхода элемента 10 поступает на третий вход блока 4 и устанавливает входной регистр этого блока в исходное состояние. Сигнал на другом выходе блока 4 становится низким (фиг. . Этот уровень поступает на вход элемента 10 И-НЕ, после чего сигнал на выходе элемента 10 И-НЕ становится высоким (фиг. 3k:). На фиг. Зк показано вре- . мя t,, в течение которого сигнал на выходе элемента 10 И-НЕ остается низким

.f 4--f° 4.-г

-, -/iM-HE ST tte

е время переключения выходin-ц Б ного сигнала элемента 10 И-НЕ с высокого уровня на низкий

(-0

время переключения триггеL (ф ра входного регистра блока А из единичного состояния в нулевое,

Таким образом, введение в устройство для ввода информации элемента 8 ИЛИ-НЕ, (JS -триггера 9 и элемента 10 позволяет вьщелить ложный сигнал по шине СИ, запретить запуск по нему второго формирователя 5 импульсов и очистить входной регистр блока 4 памяти от принятой ложной информации, что повышает достоверность передаваемой информации и исключает сбои в канале связи между ЭВМ и внешними запоминающими устройствами, вызываемые появлением ложных СИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ввода информации | 1984 |

|

SU1166094A1 |

| Устройство для ввода информации | 1985 |

|

SU1260937A1 |

| Устройство для ввода информации | 1981 |

|

SU1032446A1 |

| Устройство для контроля серий импульсов | 1989 |

|

SU1676076A1 |

| ОБНАРУЖИТЕЛЬ ПАУЗ РЕЧИ В СИСТЕМЕ С ИМПУЛЬСНО-КОДОВОЙ МОДУЛЯЦИЕЙ | 1992 |

|

RU2103826C1 |

| Устройство для ввода информации | 1988 |

|

SU1615696A1 |

| СПОСОБ СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2812335C1 |

| Устройство для вероятностного моделирования | 1979 |

|

SU857985A1 |

| Стартстопное приемное устройство | 1984 |

|

SU1205315A1 |

| Устройство для приема избыточной информации | 1983 |

|

SU1107146A1 |

УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ по авт.св. № 1032446, отличающееся тем, что, с целью повышения надежности устройства путем устранения влияния ложных сигналов по входу синхроимпульса, в него введены второй элемент ИЛИ-НЕ, триггер и второй элемент И-НЕ, выход которого соединен с дополнительным управляющим входом блока памяти, а первый вход соединен с первым выходом триггера, 2--ВХОД которого соединен с выходом второго формирователя импульсов, вход которого соединен с вторым входом второго элемента И-НЕ, третий вход которого соединен с выходом первого элемента ИЛИ-НЕ, четвертый вход второго элемента И-НЕ соединен с другим выходом блока памяти, второй выход триггера соединен с третьим входом первого элемента И-НЕ, а S -вход соединен с выходом второго элемента ИЛИ-НЕ, входы которого соединены с соответствующими выходами (Л первого формирователя импульсов. с

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для ввода информации | 1981 |

|

SU1032446A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-08-15—Публикация

1982-12-21—Подача