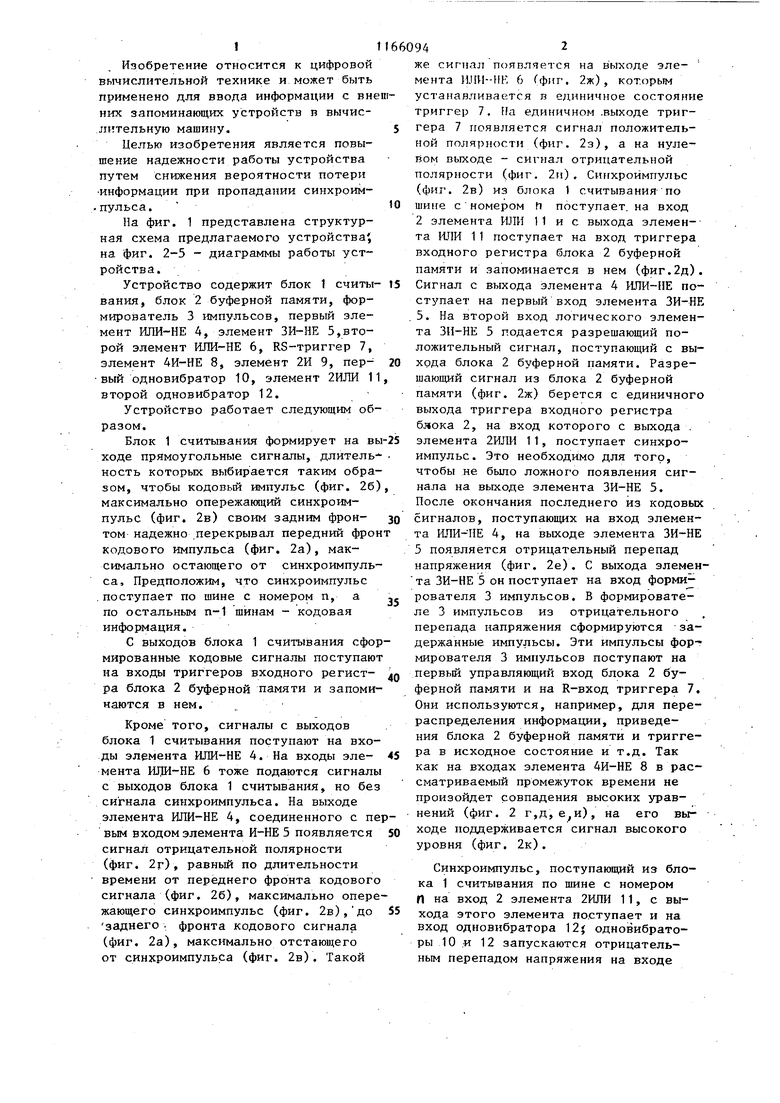

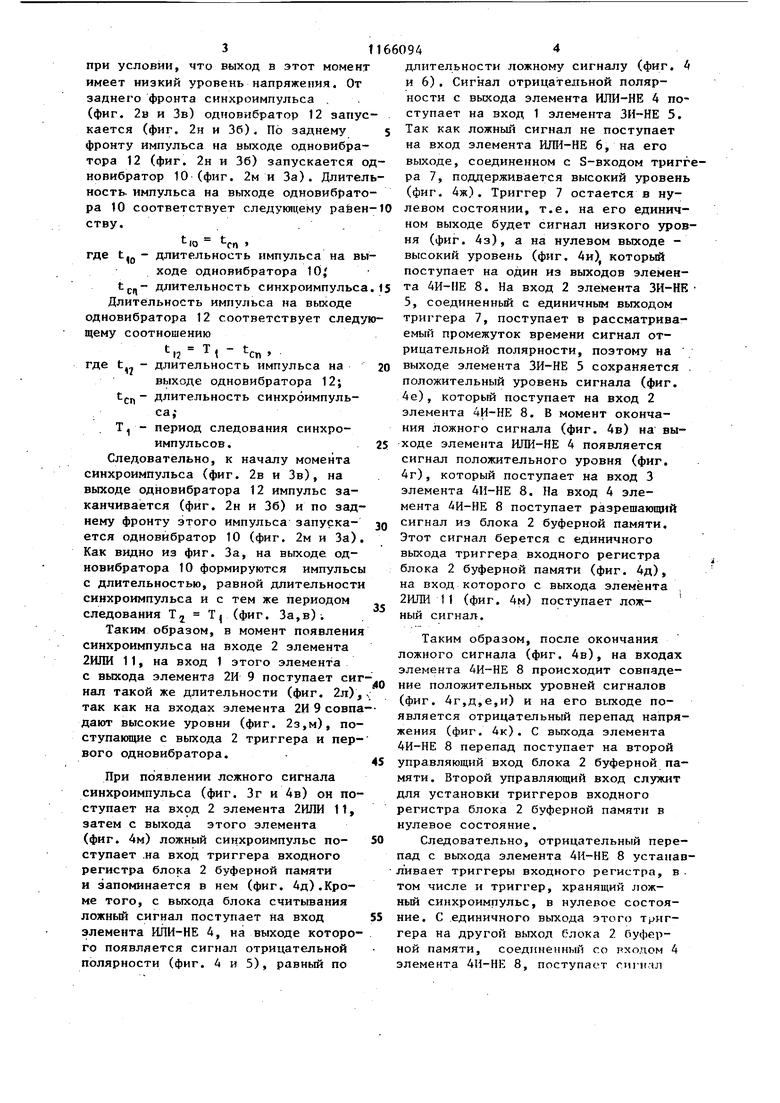

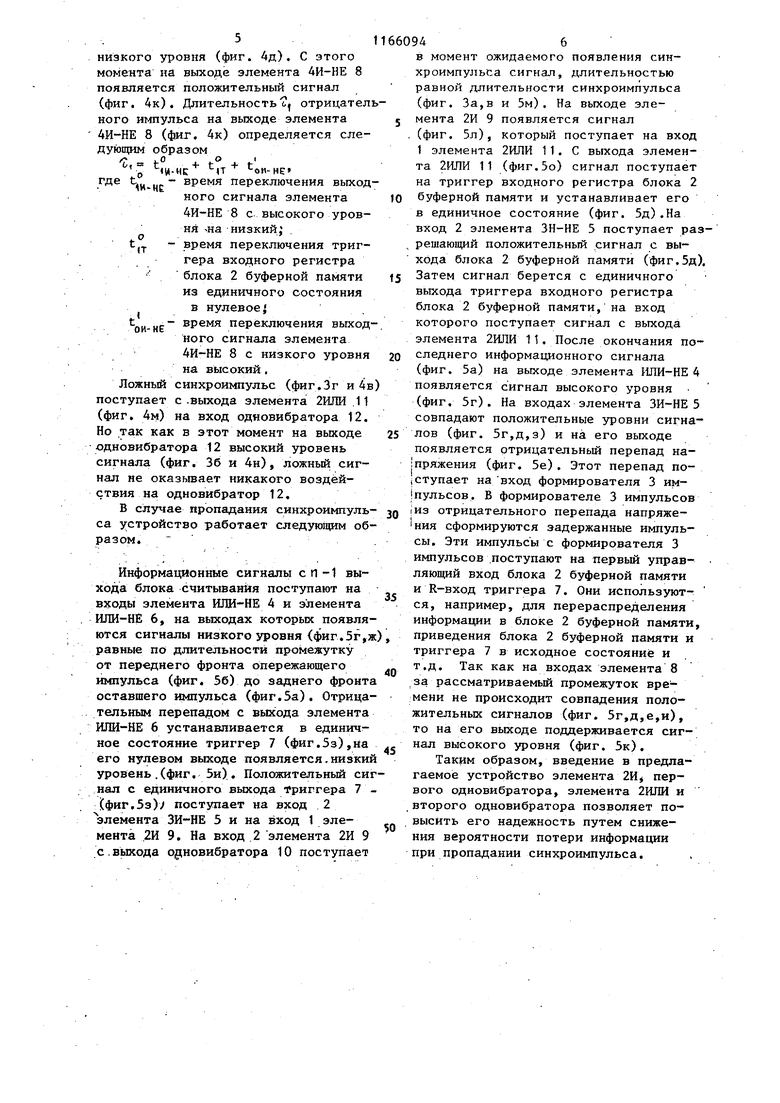

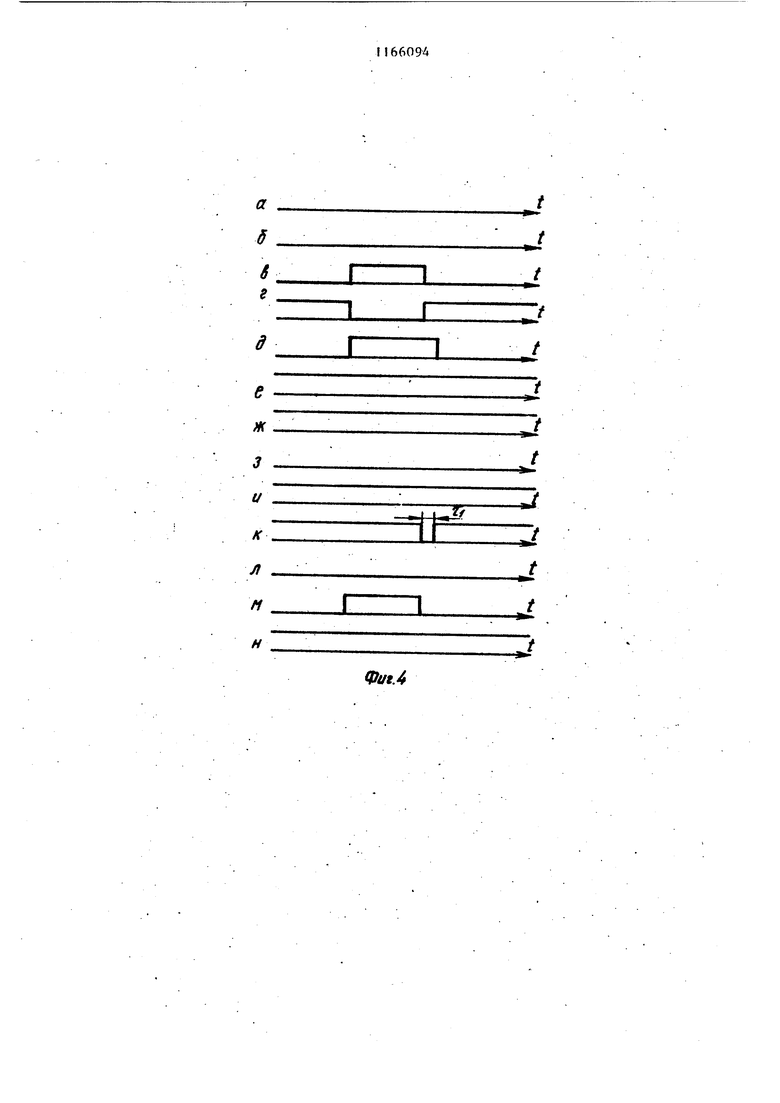

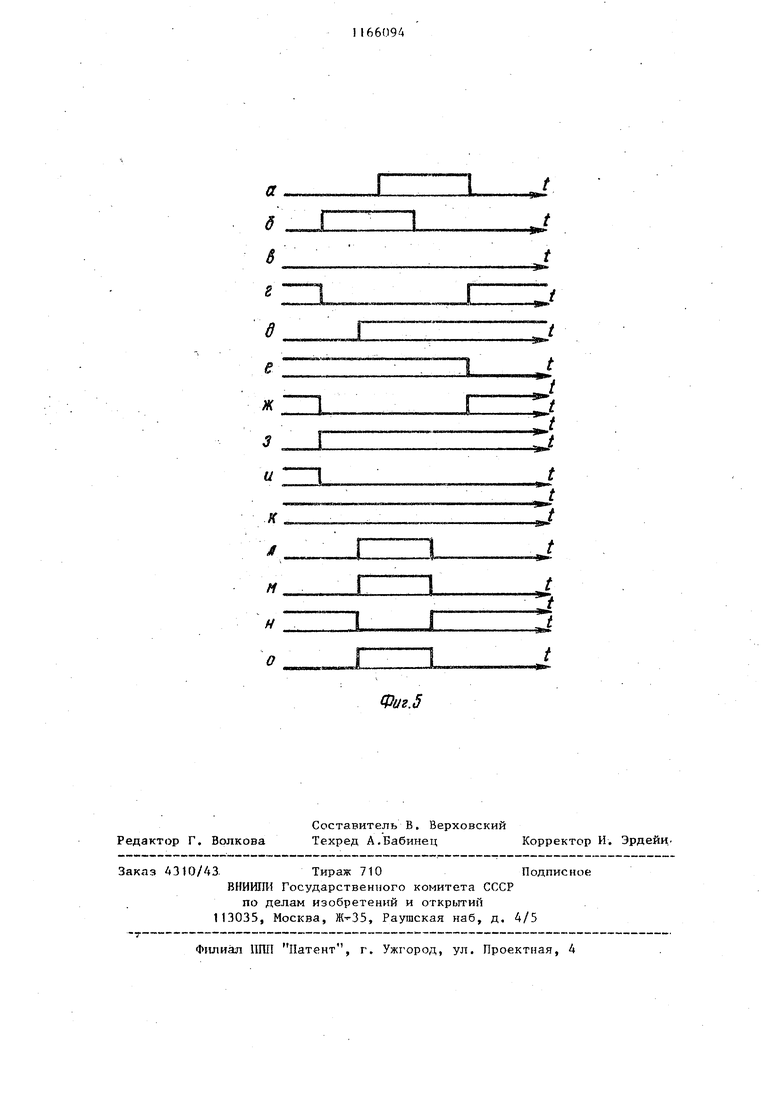

Изобретение относится к цифровой вычислительной технике и может быть применено для ввода информации с вне них запоминающих устройств в вычислительную машину. Целью изобретения является повышение надежности работы устройства путем снижения вероятности потери информации при пропадании синхроим,пульса. На фиг. 1 представлена структурная схема предлагаемого устройства , на фиг. 2-5 - диаграммы работы устройства. Устройство содержит блок 1 считывания, блок 2 буферной памяти, формирователь 3 импульсов, первый элемент ИЛИ-НЕ 4, элемент ЗИ-НЕ 5,второй элемент ИЛИ-НЕ 6, RS-триггер 7, элемент 4И-НЕ 8, элемент 2И 9, первый одновибратор 10, элемент 2ИЛИ 1 второй одновибратор 12. Устройство работает следующим образом. Блок 1 считывания формирует на в ходе прямоугольные сигналы, длитель кость которых выбирается таким обра зом, чтобы кодовый импульс (фиг. 2б максимально опережающий синхроимпульс (фиг. 2в) своим задним фронтом надежно перекрывал передний фро кодового импульса (фиг. 2а), максимально остающего от синхроимпуль са. Предположим, что синхроимпульс .поступает по шине с номером п, а по остальным п-1 шинам - кодовая информация. С выходов блока 1 считывания сфо мированные кодовые сигналы поступаю на входы триггеров входного регистра блока 2 буферной памяти и запоми наются в нем. Кроме того, сигналы с выходов блока 1 считывания поступают на входы элемента ИЛИ-НЕ 4. На входы элемента ИЛИ-НЕ 6 тоже подаются сигналы с выходов блока 1 считывания, но без сигнала синхроимпульса. На выходе элемента ИЛИ-НЕ 4, соединенного с пе вым в ходом элемента И-НЕ 5 появляется сигнал отрицательной полярности (фиг. 2г), равный по длительности времени от переднего фронта кодового сигнала (фиг. 26), максимально опере жающего синхроимпульс (фиг. 2в),до заднего . фронта кодового сигнала (фиг. 2а), максимально отстающего от синхроимпульса (фиг. 2в). Такой же сигиал появляется на выходе элемента И.ИИ-НЕ 6 Гфиг. 2ж), которым устанавливается в единичное состояние триггер 7, Ffa единичном .выходе триггера 7 появляется сигнал положительной полярности (фиг. 2з), а на нулевом выходе - сигнал отрицательной полярности (фиг. 2м). Синхроимпульс (фиг. 2в) из блока 1 считывания по шине с номером ti поступает, на вход 2 элемента ИЛИ 11 и с выхода элемента ИПИ 11 поступает на вход триггера входного регистра блока 2 буферной памяти и запоминается в нем (фиг.2д). Сигнал с выхода элемента 4 поступает на первый вход элемента ЗИ-НЕ 5. На второй вход логического элемента ЗИ-НЕ 5 подается разрешающий положительный сигнал, поступающий с выхода блока 2 буферной памяти. Разрешающий сигнал из блока 2 буферной памяти (фиг. 2ж) берется с единичного выхода триггера входного регистра блока 2, на вход которого с выхода . элемента 2ИЛИ 11, поступает синхроимпульс. Это необходимо для того, чтобы не было ложного появления сигнала на выходе элемента ЗИ-НЕ 5. После окончания последнего из кодовых сигналов, поступающих на вход элемента ИЛИ-НЕ 4, на выходе элемента ЗИ-НЕ 5 появляется отрицательный перепад напряжения (фиг. 2е). С выхода элемента ЗИ-НЕ 5 он поступает на вход формирователя 3 импульсов. В формирователе 3 импульсов из отрицательного перепада напряжения сформируются задержанные импульсы. Эти импульсы формирователя 3 импульсов поступают на первьй управляющий вход блока 2 буферной памяти и на R-вход триггера 7. Они используются, например, для перераспределения информации, приведения блока 2 буферной памяти и триггера в исходное состояние и т.д. Так как на входах элемента 4И-НЕ 8 в рассматриваемый промежуток времени не произойдет совпадения высоких уравнений (фиг. 2 г,д, ), на его выходе поддерживается сигнал высокого уровня (фиг. 2к). Синхроимпульс, поступающий из блока 1 считывания по шине с номером П на вход 2 элемента 2ИЛИ 11, с выхода этого элемента поступает и на вход одновибратора 12 одновибраторы 10 и 12 запускаются отрицательным перепадом напряжения на входе при условии, что выход в этот момен имеет низкий уровень напряжения. От заднего фронта синхроимпульса , (фиг. 2в и Зв) одновибратор 12 запу кается (фиг. 2н и 36). По заднему фронту импульса на выходе одновибра тора 12 (фиг. 2н и 36) запускается новибратор 10 (фиг. 2м и За). Длител ность, импульса на выходе одновибрат ра 10 соответствует следукицему райе ству.. . -ю Чп где t,- - длительность импульса на вы ходе одновибратора 10, длительность синхроимпульса Длительность импульса на выходе одновибратора 12 соответствует следу щему соотношению 112 сп где t, - длительность импульса на выходе одновибратора 12; длительность синхроимпульса;Т - период следования синхроимпульсов. Следовательно, к началу момента синхроимпульса (фиг. 2в и Зв), на выходе одновибратора 12 импульс заканчивается (фиг. 2н и 36) и по заднему фронту этого импульса запускается одновибратор 10 (фиг. 2м и За) Как видно из фиг. За, на выходе одновибратора 10 формируются импульсы с длительностью, равной длительности синхроимпульса и с тем же периодом следования Т Т (фиг. За,в). Таким образом, в момент появления синхроимпульса на входе 2 элемента 2Ш1И 11, на вход 1 этого элемента С выхода элемента 2И 9 поступает сиг нал такой же длительности (фиг. 2л), так как на входах элемента 2И 9 совпа дают высокие уровни (фиг. 2з,м), поступающие с выхода 2 триггера и первого одновибратора. При появлении ложного сигнала синхроимпульса (фиг. Зг и 4в) он поступает на вход 2 элемента 2ИЛИ 11, затем с выхода этого элемента (фиг. 4м) ложный синхроимпульс поступает .на вход триггера входного регистра блока 2 буферной памяти и запоминается в нем (фиг. 4д).Кроме того, с выхода блока считывания ложный сигнал поступает на вход элемента ИЛИ-НЕ 4, на выходе которого появляется сигнал отрицательной полярности (фиг. 4 и 5), равный по длительности ложному сигналу (фиг. 4 и 6). Сигнал отрицательной полярности с выхода элемента ИЛИ-НЕ 4 поступает на вход 1 элемента ЗИ-НЕ 5. Так как ложньш сигнал не поступает на вход элемента ИЛИ-НЕ 6, на его выходе, соединенном с S-входом триггера 7, поддерживается высокий уровень (фиг. 4ж). Триггер 7 остается в нулевом состоянии, т.е. на его единичном выходе будет сигнал низкого уровня (фиг. 4э), а на нулевом выходе высокий уровень (фиг. 4и) который поступает на один из выходов элемента 4И-ПЕ 8. На вход 2 элемента ЗИ-НЕ 5, соединенный с единичным выходом триггера 7, поступает в рассматриваемый промежуток времени сигнал отрицательной полярности, поэтому на выходе элемента ЗИ-НЕ 5 сохраняется , положительный уровень сигнала (фиг. 4е), который поступает на вход 2 элемента 4И-НЕ 8. В момент окончания ложного сигнала (фиг. 4в) на выходе элемента ИЛИ-НЕ 4 появляется сигнал положительного уровня (фиг. 4г), который поступает на вход 3 элемента 4И-НЕ 8. На вход 4 элемента 4И-НЕ 8 поступает разрешающий сигнал из блока 2 буферной памяти. Этот сигнал берется с единичного выхода триггера входного регистра блока 2 буферной памяти (фиг. 4д), на вход которого с выхода элемента , 2ИЛИ 11 (фиг. 4м) поступает ложный сигнал. Таким образом, после окончания ложного сигнала (фиг. 4в), на входах элемента 4И-НЕ 8 происходит совпадение положительных уровней сигналов (фиг. 4г,д,е,и) и на его вьгходе появляется отрицательньш перепад напряжения (фиг. 4к). С выхода элемента 4И-НЕ 8 перепад поступает на второй управляющий вход блока 2 буферной памяти. Второй управляющий вход служит для установки триггеров входного регистра блока 2 буферной памяти в нулевое состояние. Следовательно, отрицательный перепад с выхода элемента 4И-НЕ 8 устанавливает триггеры входного регистра, в. том числе и триггер, хранящий ложный синхроимпульс, в нулелое состояние. С единичного выхода этого триггера на другой выход Рлока 2 буферной памяти, соединенный со РХОДОМ 4 элемента 4И-НЕ 8, поступает г.мгичл низкого уровня (фиг. 4д). с этого момента на выходе элемента ДИ-НЕ 8 появляется положительный сигнал (фиг, 4к). Длительноеть, отрицател ного иг пульса на выходе элемента 4И-НЕ 8 (фиг. 4к) определяется следующим образом о о I «И-ЧС -ОИ-НЕ где t - время переключения выход ного сигнала элемента 4И-НЕ 8 с высокого уровня -на низкий; t| - время переключения триггера входного регистра блока 2 буферной памяти из единичного состояния в нулевое{ „„ ur время переключения выход On Не НОГО сигнала элемента 4И-НЕ 8 с низкого уровня на высокий , Ложный синхроимпульс (фиг.Зг и4в поступает с .выхода элемента 2ИЛИ .11 (фиг. 4м) на вход одновибратора 12. Но так как в этот момент на выходе одновибратора 12 высокий уровень сигнала (фиг. 36 и 4н), ложный сигнал не оказьюает никакого воздействия на одновибратор 12. В случае пропадания синхроимпуль са устройство работает следующим об разом. Информационные сигналы с П-1 выхода блока считывания поступают на входы элемента ИЛИ-НЕ 4 и элемента ИЛИ-НЁ 6, на выходах которых появля ются сигналы низкого уровня (фиг.5г, равные по длительности промежутку от переднего фронта опережающего 1 шульса (фиг. 56) до заднего фронт оставшего импульса (фиг.За). Отрица тельным перепадом с вьссода элемента ИЛИ-НЕ 6 устанавливается в единичное состояние триггер 7 (фиг.5з),на его нулевом выходе появляется.низки уровень.(фиг. 5и). Положительньй си нал с единичного выхода Триггера 7 (фиг.5з); поступает на вход 2 Ълемента ЗИ-НЕ 5 и на вход 1 элемента .2И 9. На вход 2 элемента 2И 9 с.выхода о новибратора 10 поступает в момент ожидаемого появления синхроимпульса сигнал, длительностью равной длительности синхроимпульса (фиг. За,в и 5м), На выходе элемента 2И 9 появляется сигнал (фиг, 5л), который поступает на вход 1 элемента 2ИЛИ 11, С выхода элемента 2ИЛИ 11 (фиг,5о) сигнал поступает на триггер входного регистра блока 2 буферной памяти и устанавливает его в единичное состояние (фиг, 5д),На вход 2 элемента ЗН-НЕ 5 поступает разрешающий положительный сигнал с выхода блока 2 буферной памяти (фиг,5дХ Затем сигнал берется с единичного выхода триггера входного регистра блока 2 буферной памяти, на вход которого поступает сигнал с выхода элемента 2ИЛИ 11, После окончания последнего информационного сигнала (фиг, 5а) на выходе элемента ИЛИ-НЕ4 появляется сигнал высокого уровня (фиг. 5г), На входах элемента ЗИ-НЕ 5 совпадают положительные уровни сигналов (фиг, 5г,д,з) и на его выходе появляется отрицательный перепад на- пряжения (фиг. 5е), Этот перепад поСтупает навход формирователя 3 импульсов, В формирователе 3 импульсов ИЗ отрицательного перепада напряжения сформируются задержанные импульсы. Эти импульсы с формирователя 3 импульсов поступают на первый управляющий вход блока 2 буферной памяти и R-вход триггера 7, Они используются, например, для перераспределения информации в блоке 2 буферной памяти, приведения блока 2 буферной памяти и триггера 7 в исходное состояние и т,д. Так как на входах элемента 8 за рассматриваемый промежуток времени не происходит совпадения положительных сигналов (фиг, 5г,д,е,и), то на его выходе поддерживается сигнал высокого уровня (фиг, Зк). Таким образом, введение в предлагаемое устройство элемента 2И первого одновибратора, элемента 2Ш1И и второго одновибратора позволяет повысить его надежность путем снижения вероятности потери информации при пропадании синхроимпульса.

Фиг.1

ф1/г.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ввода информации | 1985 |

|

SU1260937A1 |

| Устройство для ввода информации | 1981 |

|

SU1032446A1 |

| Мажоритарное декодирующее устройство | 1986 |

|

SU1372627A1 |

| Устройство для измерения нелинейности пилообразного напряжения | 1990 |

|

SU1777101A1 |

| Устройство для отладки и контроля хода программ | 1989 |

|

SU1691843A2 |

| УСТРОЙСТВО ДИАГНОСТИЧЕСКОГО КОНТРОЛЯ КАНАЛА ВОСПРОИЗВЕДЕНИЯ АППАРАТУРЫ ЦИФРОВОЙ МАГНИТНОЙ ЗАПИСИ | 1991 |

|

RU2024968C1 |

| Устройство для ретрансляции речевых сигналов | 1990 |

|

SU1830627A1 |

| Устройство для ввода информации | 1982 |

|

SU1108433A2 |

| Цифровой измеритель центра тяжести видеосигналов | 1990 |

|

SU1723559A1 |

| Буферное динамическое оперативное запоминающее устройство | 1989 |

|

SU1695388A1 |

УСТРОЙСТВО. Д.Т1Я ВВОДА-ИНФОРМАЦИИ, содержащее блок считывания, блок памяти, два элемента ИЛИ-НЕ, RS-триггер, элемент , элемент 4И-НЕ, формирователь импульсов, выходы блока считывания подключены к входам первого элемента ИЛИ-НЕ, выход которого подключен к первому входу элемента ЗИ-11Е и к третьему входу элемента 4И-НЕ, выход элемента ЗИ-ИЕ подключен к второму входу элемента 4И-НЕ и к входу формирователя импульсов, выход которого подключен к первому управляющему входу блока памяти и R-входу RS-триггера, S-вход которого подключен к выходу второго элемента ИЛИ-НЕ, прямой выход RS-триггера подключен к третьему вхрду элемента ЗИ-НЕ, а его И 1версный выход 1 первому входу элемента 4И-НЕ, выходы блока считывания, кроме одного, подключены к входам второго элемента Ш1И-ИЕ и к информационным входам, кроме одного, блока памяти, один из выходов блока памяти подключен к входу элемента ЗИ-НЕ и к четвер1ому входу элемента 4И-НЕ, остальныа выходы блока памяти являются выходами устройства, второй управляющий вход блока памяти подключен к выходу элемента 4И-НЕ, о т л и ч агю щ е е с я тем, что, с целью повыг-. шения надежности устройства путем снижения вероятности потери информации (Л при пропадании синхроимпульса, оно содержит элемент 2И, элемент 211Г1И и два последовательно соединенные одновибраторы, входы элемента 2И подключены к прямоьгу выходу RS-триггера и к выходу второго одновибратора соответственно, а его выход - к первому входу элемента 2ИПИ, второй вход коО5 торого подключен к одному из выходов 05 блока считьгаания, а выход - к одному О из информационных входов блока памясо ти и к входу первого одновибратора. 4:аь

.J

Фиг.5

| Каган Б,М | |||

| и др | |||

| Запоминающие устройства большой емкости, М., Энергия, 1968 | |||

| Устройство для ввода информации | 1982 |

|

SU1108433A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-07-07—Публикация

1984-01-05—Подача