I 1

Изобретение относится к вычислительной технике и может быть испольэовано для контроля узлов ЭВМ, в частности регистров сдвига.

Известно устройство для контроля регистра сдвига, содержащее контролируемый регистр, элементы И, формирователь импульсов, триггер

Недостатком указанного устройства является необходимость вьщелевия дополнительного времени на диагностику регистра.

Наиболее близким по технической сущности к предлагаемому устройству является устройство для койтроля регистра сдвига;, содержащее контродшруемый регистр сдвига, формирователь строба, триггер, элементы И и сумматоры ио модулю два.

Принцип работы устройства заключается в контроле регистра сдвига путем сравнения i-ro бита входной последовательности после того, когда он запишется в последний разряд регистра сдвига со значением этого же бита входной последовательности, которое было зафиксированое триггером в момент записи его в первый разряд регистра сдвига Г2.

Недостатком указанного устройства является его низкое быстродействие, .обусловленное большим временем обнаружения отказа. Поясним это на примере, когда контролируемый регистр имеет неисправность типа постоянного нуля на выходе регистра. Если формирователь строба сформирует строб на своем выходе в момент времени, когда на входе контролируемого регистра присутствует нулевой бит информации, то устройство запомнит его и при появлении следующего строба произойдет сравнение нулевого бита информации с нулевым состоянием последнего разряда регистра. Поэтому указанный отказ не обнаружен в этом цикле контроля.

Появление в информационной послеовательности нулей и единиц носит случайный характер. Поэтому вполне вероятно, что в момент появления слеующего строба на выходе формироватея, на входе регистра снова имеется нулевой бит информации, который запомнится устройством. Следовательно, в этом цикле контроля указанный ьше отказ не обнаружен. Так продолается до тех пор, пока в момент повления строба на выходе формировате085102

ля на входе регистра не появится единичный бит информации. Только в этом случае устройство зафиксирует отказ. Но из-за случайного характера появле5 НИН нулей и единиц в информационной последовательности может пройти несколько циклов контроля, пока обнаружится отказ регистра. Несвоевременно обнаруженный отказ в устройст10 ве может привести к нежелательным последствиям для системы в целом.

Цель изобретения - повьпиение быстродействия за счет уменьшения времени обнаружения отказа в контролируе15 мом регистре сдвига.

Поставленная цель достигается тем, что в устройство для контроля регистра сдвига:, содержащее управляемый .сумматор по модулю два, выход кото20 рого является выходом устройства, первый и второй элементы И, первый триггер и формирователь строба, введены второй и третий триггеры, элемент НЕ, третий элемент И и элемент

25 ИЛИ, причем выход элемента ЦПИ соединен с входом установки в единицу первого триггера, вход установки в ноль которого соединен с выходом формирователя строба и управляющим

3Q входом сумматора по модулю два, инверсный выход - с первыми входами второго и третьего элементов И а прямой вьвсод - с первым входом первого элемента И, выход которого соединен с входом формирователя строба, второй вход второго элемента И через элемент НЕ соединен с вторым входом третьего элемента И и является первым информационным входом устройства, выход второго элемента И соединен с первым входом элемента ИЛИ, с входом установки в единицу второго триггера и с входом установки в ноль третьего триггера, выход третьего элемента И соединен с вторым входом элемента ИЖ, с входом установки в ноль второго триггера и с входом установки в единицу третьего триггера, инверсные выходы второго и третьего триггеров соединены с третьими входами сооветствующих элементов И, прямой выход второго триггера соедине.н с первым входом сумматора по модулю два, второй вход которого является вторым информационным входом

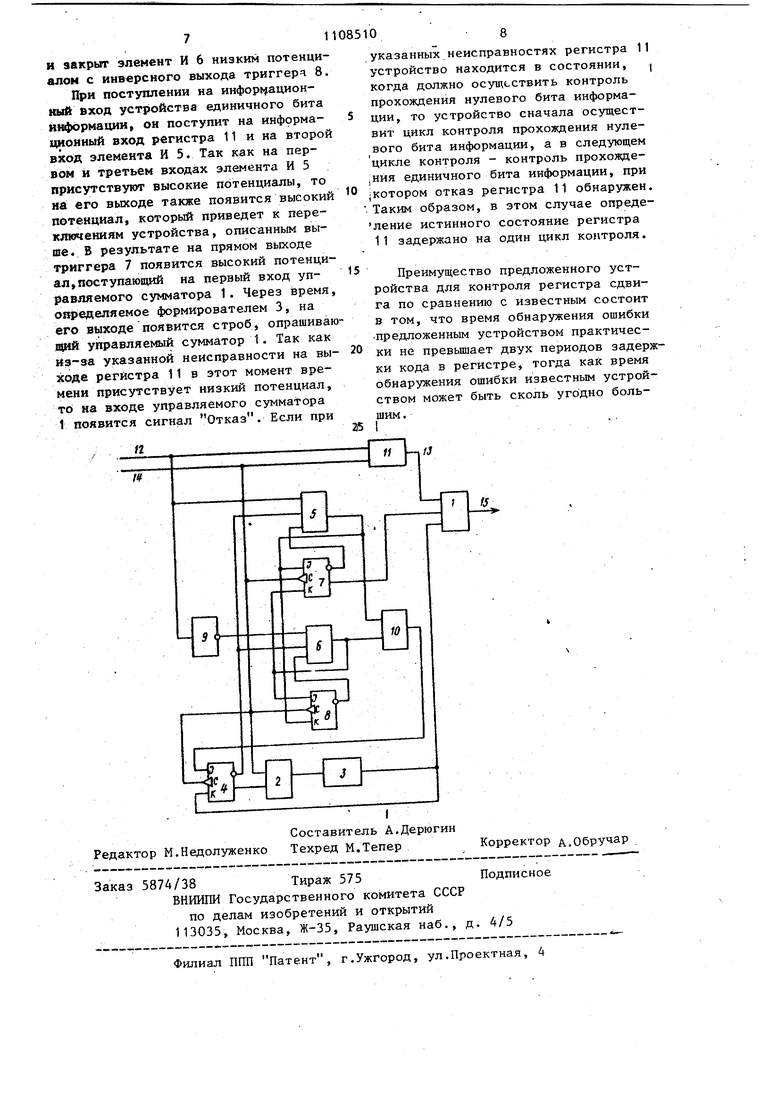

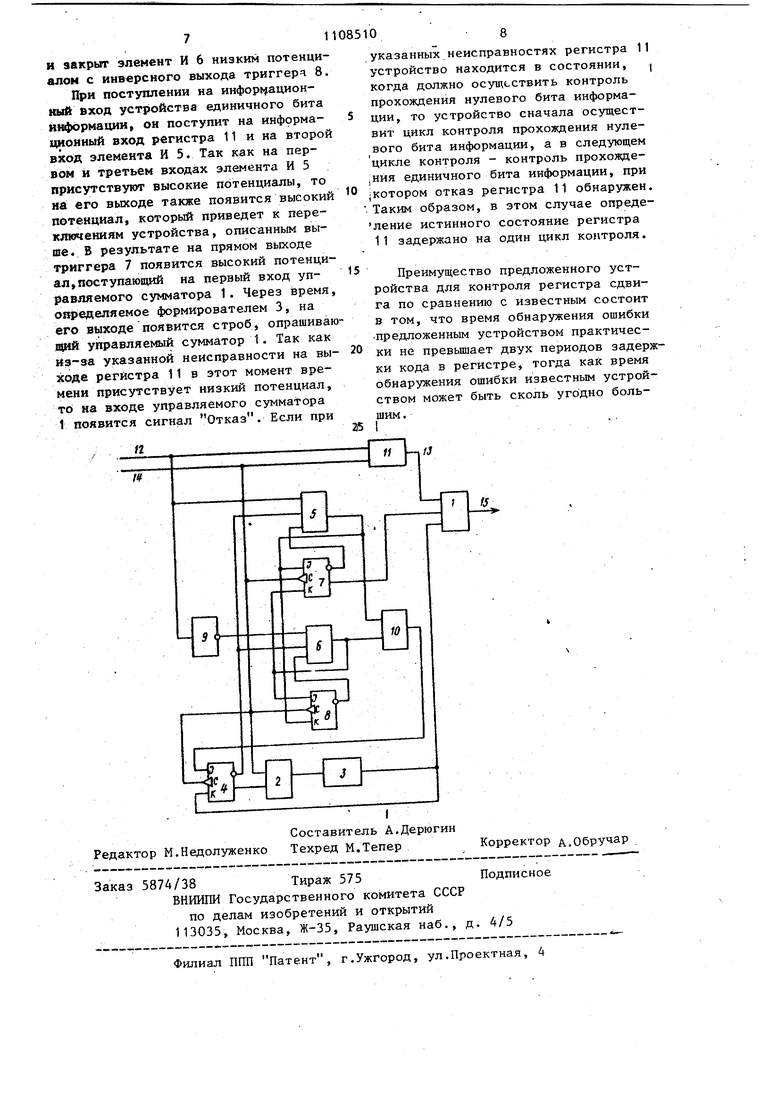

устройства, второй вход первого элемента И соединен с тактовыми входами первого, второго и третьего триггеров и является тактовым входом устройства. На чертеже приведена функциональная схема устройства для контроля регистра сдвига. Предлагаемое устройство для контроля регистра сдвига содержит управляемый сумматор 1 по модулю два, пер вый элемент И 2, формирователь 3 строба, первый триггер 4, второй и третий элементы И 5 и 6 второй и тре тий триггеры 7 и 8, элемент НЕ 9, элемент ИЛИ 10. На черетеже показан также контролируемый регистр 11 сдви га (последний в предлагаемое устройство не входит) . Регистр 11 имеет информационный вход 12, выход 13 и тактовый вход 14, которые являются первым и вторым информационными и тактовыми входами устройства для . контроля. Выход управляемого суммат о ра 1 по модулю два является выходом 15 устройства для контроля регистра сдвига. Формирователь 3 строба может быть выполнен на основе двоичного счетчика, срабатывающего по переднему фрон ту тактового импульса, с коэффициентом пересчета, равным разрядности регистра 11 сдвига, причем импульс, появляющийся на выходе формирователя 3, задним фронтом устанавливает элементы формирователя 3 в исходное нулевое состояние. Синхронные триггеры 4, 7 и 8 переключаются по заднему фронту тактового импульса. Принцип работы предлагаемого устройства основан на запоминании нулевого и единичного бита входной инфор мации, поступающей на вход контролируемого регистра сдвига, и контроля его на выходе регистра сдвига через время, равное времени прохождения этого бита через контролируемый регистр сдвига. Это осуществляется с помощью формирователя 3 строба, кото рый запускается в момент запоминания входного бита информации и выдает строб в момент появления этого бита информации на выходе контролируемого регистра сдвига. Устройство построено таким образом что.если им был зафиксирован и проконтролирован на выходе контролируе-г МОго регистра сдвига нулевой (единичный) бит информации, то контроль следующего нулевого (единичного) бит информации не осуществляется. Новый цикл контроля осуществляется лишь тогда, когда на вход контролируемого регистра-сдвига после окончания цикла контроля нулевого (единичного) бита информации поступит единичный (нулевой) бит информации, т.е. устройством осуществляется поочередной контроль прохождения нулевого и единичного бита информации через контрЬ лируемый регистр сдвига. Поэтому время ожидания до очередного цикла контг роля, осуществляющего контроль прохождения бита информации противоположной полярности, по сравнению с полярностью бита информации на предыдущем цикле контроля может находиться в пределах нескольких тактов, а не нескольких циклов, как при решеЮ я аналогичной задачи контроля . Устройство для контроля регистра сдвига работает следующим образом. При включении питания импульсом начальной установки все элементы памяти устройства приводятся в исходное (нулевое) состояние (цепн установки в ноль на чертеже не показаны). Пусть а момент времени, когда на тактовом входе устройства появляется первьй тактовый импульс, на информационном входе устройства присутствует нулевой бит информации. Следовательно, на выходе элемента НЕ 9 присутствует высокий потенциал, который поступит на второй вход третьего элемента И 6, на первом и третьем входах которого присутствуют высокие потенциалы с инверсных выходов триггеров 4 и 8. Поэтому на выходе элемента И 6 появится высокий потенциал, который поступает на вход установки в ноль триггера 7, на вход установки Б единицу триггера 8 и через элемент ИЛИ 10 - на вход установки в единицу триггера 4. Поэтому по заднему фронту тактового импульса триггеры 4 и 8 установятся в единичное состояние, а триггер 7 останется в нулевом востоянии. На инверсном выходе триггера 8 появится нулевой потенциал, который, поступая на третий вход элемента И 6, запретит на его выходе высокий потен.циал. Низкий потенциал с инверсного выхода триггера 4 закроет элементы И 2 и 6, а высокий потенциал с его прямого выхода даст разрешение прохождению тактовых импульсов с тактового входа устройства на вход формирователя 3 через элемент И 2. Через время, равное прохождению указанного бита информации через регистр . 11, на выходе формирователя 3 появляется сигнал опроса. К этому временн на выходе регистра 11 появится нулевой бит информации, который совпадает с нулевым состоянием триггера 7. Следовательно, при правильной работе регистра 11 на втором входе управляемого сумматора 1 присутствует низкий потенциал с выхода регистра 11, на первом входе управляемого сумматора 1 - низкий потенциал с пря мого выхода триггера 7, Поэтому при поступлении на управляющий вход управляемого сумматора 1 строба с выхо да формирователя 3 на выходе управляемого сумматора 1 отсутствует сигнал Отказ. Кроме того, сигнал с вы хода формирователя 3 поступает на вход установки в ноль триггера 4. Так как на тактовый вход триггера 4 поступает в это время тактовый импульс, то по заднему фронту этого импульса триггер 4 установится в нулевое состояние, закрывая по первому входу элемента И 2 и открывая по первьм входам элементы И 5 и 6. На этом цикл контроля заканчивается и устройство может переходить к следующему циклу контроля. Если после выработки строба формирователем 3 на информационном входе устрой ства вновь появится нулевой бит информации, то новый цикл контроля не начнется, так как элемент И 6 закрыт низким потенциалом с инверсного выхода триггера 8, а на второй вход элемента И 5 поступает нулевой бит информации. Поэтому на выходе элемента ИЛИ 10 присутствует нулевой сигнал. Так продолжается до тех пор, пока на информационном входе устройства не появится единичный бит инфор мации . В этом случае на всех трех входах элемента И 5 присутствуют высокие потенциалы, в результате чего на его вьпсоде также появится высокий потенциал. Это сигнал поступит на вход установки в ноль триггера 8, на вход установки в единицу триггера 7 и через элемент ИЛИ 10 - на вход установ ки в единицу триггера 4. Поэтому зад ним фронтом очередного тактового импульса триггеры 4 и 7 установятся в единичное состояние. При этом высокий потенциаш с прямого выхода триггера 7 поступит на первый вход управляемого сумматора 1, а низкий потенциал с его инверсного выхода закроет элемент И 5. Низкий потенциал с инверсного выхода триггера 4 закроет элементы И 5 и 6, а высокий потенциал с прямого выхода триггера 4 поступит на вход элемента И 2, разрешая прохождение тактовых импульсов на вход формирователя 3. Кроме того, задним фронтом тактового импульса триггер 8 установится в нулевое состояние. Поэтому на его инверсном выходе появится высокий потенциал, снимающий запрет с. третьего входа элемента И 6. Через время, равное прохождению единичного бита информации через регистр 11, на его выходе появится единичный сигнал, который поступит на вход управляемого сумматора 1 . На первом входе управляемого,сумматора 1 также присутствует единичный сигнал с прямого выхода триггера 7. В это же время на выходе формирователя 3 появится строб, поступающий на управляющий вход управляемого сумматора 1. Так как на первом и втором входах управляемого сумматора 1 присутствуют единичные сигналы, то на его выходе отсутствует сигнал Отказ. Кроме того, строб с выхода формирователя 3 поступит также на вход установки в ноль триггера 4, который по заднему фронту тактового импульса установится в нулевое состояние. При этом единичный сигнал с инверсного выхода триггера 4 поступит на первые входы элементов И 5 и 6, открывая их по этому входу, а нулевой сигнал с прямого выхода закроет элемент И 8, запрещая прохождение тактовых импульсов на вход формирователя 3. Устройство готового к следующему циклу контроля, который начнется только тогда, когда на информационный вход устройства поступит теперь уже нулевой бит информации, и т.д. Рассмотрим работу устройства при неисправности регистра 11, заключа.ющейся в наличии постоянного нуля на выходе регистра 11, или любой другой неисправности, приводящей к появлению на выходе регистра 11 ноля вместо ожидаемой единицы. Пусть устройство находится в состоянии, когда оно должно осуществить контроль прохоядения единичного бита информации через регистр 11, т.е. открыт элемент И 5 по первому и тре- . тьему входам высокими потенциалами с инверсных выходов триггеров 4 и 7

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля регистра сдвига | 1986 |

|

SU1322380A1 |

| Генератор сочетаний | 1984 |

|

SU1166090A1 |

| Устройство для контроля регистра сдвига | 1981 |

|

SU964646A1 |

| Устройство для сопряжения между абонентами | 1988 |

|

SU1594550A1 |

| Устройство для контроля регистра сдвига | 1980 |

|

SU911530A1 |

| Сигнатурный анализатор | 1983 |

|

SU1140123A1 |

| Устройство для контроля параметров | 1985 |

|

SU1303998A1 |

| Устройство для программного управления шаговым двигателем | 1989 |

|

SU1675850A1 |

| Квадратор | 1985 |

|

SU1258826A2 |

| Устройство для сопряжения между абонентами | 1987 |

|

SU1411759A1 |

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ РЕГИСТРА СДВИГА, содержащее управляемый сумматор по модулю два, выход которого является выходом устройства, первый и второй элементы И, первый триггер и формирователь строба, отличающееся тем, что, с целью повьшения быстродействия за счет уменьшения времени обнаружения отказа, в устройство введены второй и третий триггеры, элемент НЕ, третий элемент И и элемент ИЛИ, причем выход элемента ИЛИ соединен с входом установки в единицу первого триггера, вход установки в ноль которого еоединен с выходом формирователя строба и управляющим входом сумматора по модулю два, инверсный выход с первь 1И входами второго и третьего элементов И, а прямой выход - с первым входом первого элемента И, выход которого coefi aeH с входом формирователя строёа, второй вход второго элемента И элемент НЕ соединен с вторьм входом третьего элемента И и является первым информационным входом устройства, выход второго элемента И сйединен с первым входом элемента ИЛИ, с входом установки в единицу второго триггера и с входом установки в ноль третьего триггера, выход третьего элемента И соединен с вторым входом элемента ИЛИ, с входом установки в ноль второго триггера и с входом установки в единицу третьего триггера, инверсные выходы и третьего триггеров соединены; с-третьими входами соответствуюадах элементов И, прямой выход второго триггера соединен с первым входом сумматора по модулю два, второй вход которого является вторым информационным входом устрой ства, второй вход первого элемента И соединен с тактовыми входами перэо :л вого, второго и третьего триггеров и является тактовым входом устройства. .

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для контроля регистра сдвига | 1971 |

|

SU463973A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для контроля регистра сдвига | 1978 |

|

SU679984A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-08-15—Публикация

1982-12-31—Подача