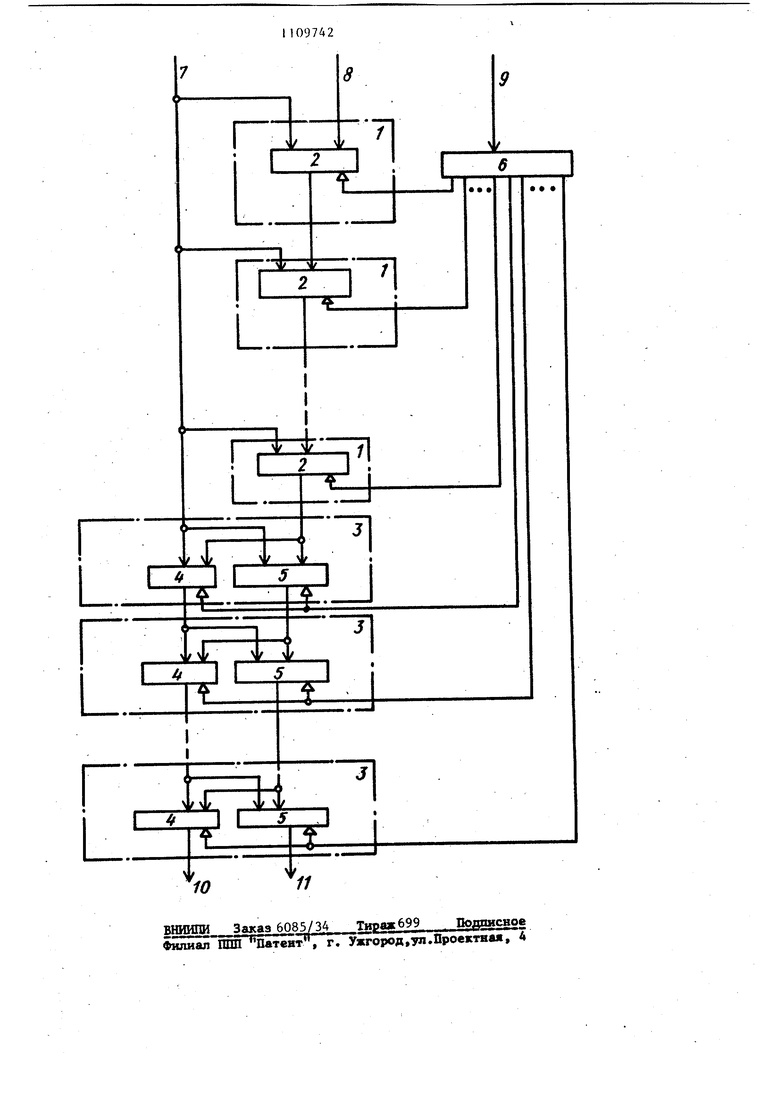

Изобретение относится к вычисли тельной технике и предназначено для построения на его основе специали-. зированных вычислителей. Известно вычислительное устройст во V 3 вьтолняющее операции поворо та вектора на плоскости ,XcosV+YeJn/} ; (Ycos4-Xsinf), координаты исходного вектора; Х,У координаты вектора, повер нутого на угол; коэффициент удлинения коо динат. . Недостатками этого устройства являются низкие быстродействие и то ность вычисления. Известно арифметическое устройст во t2j, содержащее два регистра, два сумматора-вычислителя, два коммутатора, дешифратор. Вычисление вы ражения данном устройстве выполняется по модифицированно алГо ритму Волдера, а время вычисления равно Л . T, .J время сложения или вычита ния; задержка в коммутаторе; время считывания констант из депифратора. Недостатки данного устройства низкие быстродействие и точность вычисления. Наиболее близким к предлагаемому по технической сущности является вычислительное устройство для пово рота вектора З J, реализ5№мцее алгоритм Волдера исодержащее h после довательно соединенных итерационных блоков, каждый из которых содержит три сумматора-вычитателя и коммутатор . Операция ( ) )в известном устройстве вьшолняется по алгоритму Волде Y,,,.Y,-f,X.r; .. /Hi rfi« 42 .. f. - функция, указывающая направ ление поворота, причем .« 9,1,..., (П-П- номер итерации. 42 Для вычисления выражения (1)по алгоритму(2 )в известном устройстве необходимо затратить время Т. ftce Затраты оборудования составляют ) Дв сб затраты на р-разрядный сумматор-вычитатель затраты на коммутатор. Среднеквадратическая общая погрешность вычисления по алгоритму(2 равна f п-г п - 11 I . П2 11 24 что при, составляет четыре единицы младшего разряда. Недостатками известного устройства являются большие затраты оборудования и низкая точность вычйсле ::я. Цель изобретения - сокращение затрат оборудования и повышение точности вычисления. Поставленная цель достигается тем, что ввычислительное устройство для поворота вектора, содержащее П последовательно соединенных итерационных блоков, где п - число шагов итераций, каждый из которых, начиная с первого по n/2-й, содержит сумматор-вычитатель, первые информационные входы которых соединены с входом первой координаты вектора устройства, второй вход координаты вектора устройства соединен с вторым информационным входом сумматора-вычитателя первого итерационного блока, выход каждого сумматора-вычитателя 1-го итерационного блока (,...., П/2-Ij соединен с вторым информационным входом сумматора-вычитателя (i + lj-ro итерационного блока со сдвигом на один разряд вп| аво причем каждый -и итерационный блок (где j n/2+I, П/2+2h) содержит первый и второй сумматорывычитатели, первый информационньЕЙ вход первого сумматора-вычитателя (11/2+1 )-го. итерационного блока соединен с выходом сумматора-вычитателя ft/2-го итерационного блока со сдвигом на один разряд вправо и первым информационным входом второго сумматора-вычитателя со сдвигом на (п -2)разряда вправо, второй информационный вход второго сумматора-вычитателя соединен с первым входом устройства и вторым информационным входом первого сумматора- вычигателя первые информационные входы соответственно первого и второго сумматоров-вычитателей последующего ите рационного блока соединены с выходом второго сумматора-вычитателя предыду щего итерационного блока со сдвигом соответственно на один разряд вправо, вторые информационные входы первого и второго сумматороввычитателей последующего итерационного блока соединены с выходом первого сумматора-вычитателя предьвдуще го итерационного блока, выходы первого и второго сумматоров-вычитателей последующего итерационного блок соединены соответственно с первым и. вторым выходами результата устрбйства, дополнительно введен блок постоянной памяти,причем вход блока п стоянной памяти Ьоединен с входом угла поворота устройства, выходы блока постоянной памяти с первого по n/2-й соединены с знаковыми входами сумматоров-вычитателей соответ ствующих итерационных блоков, выход блока постоянной памяти с(п/2 + 1)по h-й соединены с знаковыми входам первого и второго сумматоров-вычита телей соответствующих итерационных блоков. На чертеже представлена схема вычислительного устройства для пово рота вектора. Устройство содержит л/2 последовательно соединенных итерационных блоков 1, каждый из которых содержи сумматор-вычитатель 2, п/2 итерационных блоков 3, каждый из которых содержит первый и второй сумматорывычитатели 4 и 5, блок 6 постоянной памяти, входы 7 - 9 и выходы 10 и П. Вычисление выражения(1 )в устройстве осуществляется по алгоритму ,Меджита -2(п-1-1) .2- , 43) .г2.Мпн-Л). Отличие алгоритма(. 3 )от алгоритма (2)состоит в том, что значения 6. считываются из блока постоянной памяти, а не вычисляются. Обычно при выполнении операции поворота ве Tojpa значения углов поворота напере известно при выполнении, поэтому они предварительно записываются в блок постоянной памяти в арктангенс ной системе счисления. В блоке постоянной памяти углы поворота записаны.в виде .,., Неустройство работает следующим образом. Координата исходного вектора X по входу 7 поступает на первые входы сумматоров-вычитателей 2 всех итерационных блоков 1 и на вторые входы сумматоров-вычитателей 4 и 5 . первого итерационного блока 3, а координата У по входу 8 поступает на второй вход сумматора-вычитателя 2 первого итерационного блока 1,. В каждом итерационном блоке устройства выполняется одна итерация алгоритма (3)и результаты поступают в следующий итерационный блок, где над ними выполняется следующая итерация.Так как в первом уравнении алгоритма(З) в первых л/2 итерациях значение второго слагаемого равнб нулю(из-за выхода за пределы разрядной сетки при сдвиге), это позволяет не включать в итерационные блоки 1 сумматора-вычитателя для выполнения данного ур авнения. Сдвиги на 2(п - i -1)и На один разряд вправо осуществляются путем жесткости соединения выходов разрядов сумматороввычитателей предыдущего итерационного блока с входами разрядов сумматоров-вычитателей последующего блока со сдвигом на данное число разрядов. Управление работой сумматоров-вычитателей осуществляется от соответствующих разрядов углов поворота, считываемых из блока 6 постоянной памяти по адресу, поступающему по входу 9. Наличие сигнала О на выходе разряда блока постоянной памяти ( Ч -1 )обеспечивает настройку сумматоров-вычитателей 2 и 5 на выполнение операции вычитания, а сумматоров-вычитателей 4 - на выполнение операции сложения. Наличие сигнала 1 на выходе разряда блока постоянной памяти , +I)обеспечивает противоположную настройку. Количество блоков устройства п равно числу требуе1Ф1Х шагов итерационного процесса (З). Координаты y jитогового вектора с выходов 10 и 1J п/2-то блока 3 выводятся на информационные выходы устройства. Общее время вычисления в предлагаемом устройстве равно. .

где 151,5 - время считывания угла поворота из блока постоянной памяти. Затраты оборудования составляют

,,,

затраты на блок постоянной

памяти.

Общая погрешность вычисления в предлагаемом устройстве составляет

л -1-7-

Ч(, 2

т.е. она не зависит от разрядности аргумента и равна приблизительно единице младшего разряда.

Таким образом, при той же скорости вычисления предлагаемое устройство превосходит известное по затратам обо,рудования в

L

.+ w

n(3V4c,

KfA

2

-fWten- nav.

no точности вычисления в

п2 .

раз

при преимущество в 4,16 раз.

В предлагаемом .устройстве полностью отсутствуют элементы синхронизации, что исключает необходимость разработки устройства управления.

Однородность и регулярность структуры предлагаемого устройства позволяет изготавливать его в виде большой интегральной схемы.

Эффективность изобретения заключается в сокращении затрат оборудования и повышений точности вычисления устройства для выполнения операции поворота вектора, причём за счет повышения.точности вычисления обеспечивается дополнительное сокращение затрат оборудования, так как, нет необходимости увеличивать разрядность операционных, элементов с целью повышения точности/

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для поворота вектора | 1983 |

|

SU1144104A1 |

| Устройство для преобразования систем координат | 1976 |

|

SU656069A1 |

| Цифровое устройство для вычисления синусно-косинусных функций | 1980 |

|

SU868753A1 |

| Устройство для преобразования координат | 1977 |

|

SU660055A2 |

| Устройство для выполнения преобразования координат | 1987 |

|

SU1462299A1 |

| Цифровой функциональный преобразователь | 1981 |

|

SU1105888A1 |

| Арифметическое устройство | 1979 |

|

SU796844A1 |

| Устройство для вычисления @ | 1983 |

|

SU1156067A1 |

| Функциональный преобразователь | 1977 |

|

SU693379A2 |

| Конвейерное устройство для вычисления функций синуса и косинуса | 1987 |

|

SU1476462A1 |

ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО ДЛЯ ПОВОРОТА ВЕКТОРА, содержащее ri последовательно соединенных итерационных блоков, где п - число шагов итераций, каждый из которых, начиная с первого по /2-й, содержит сумматор-вычитатель, первые информационные входы которых соединены с входом первой координаты вектора устройства, второй вход координаты вектора устройства соединен с вторым информационным входом сумматоравычитателя первого итерационного блока, выход каждого сумматора-вычитателя j-ro итерационного блока (,..., ) соединен с вторым информационным входом сумматора-вычитателя (i+l)-ro итерационного блока со сдвигом на один разряд вправо, причем каждый j-й итерационный j п/2+1 , п/2 «-2,...п) содержит первый и второй сумматорывычитатели, первый информационный вход первого сумматора-вычитателя (П;/2+1)-го итерационного блока соединен с выходом сумматора-вычитателя П/2-ГО итерационного блока со сдвигом на один разряд вправо и первым информационным входом второго сумматора-вычитателя со сдвигом на(п-2)разряда вправо, второй информационный вход второго сумматоравычитвтеля соединён с первым входом устройства и вторым информационным входом первого сумматора-вычитателя, первые информационные входы соответственно первого и второго сумматороввычитателей последукицего итерационного блока соединены с выходом второго сумматора-вычитателя предыдущего итерационного блока со сдвигом соответственно на(п-2)й на один разряд вправо, вторые информационные входы первого и второго сумматоров-вычитателей порледукйдего итерационного блока соединены с выходом первого сумматора-вычитателя предвдущего итерационного блока, выхода первого и второго ;сумматоров-вычитателей последующего итерационного блока соединены соответственно с первым О и вторым выходами результата устрой- ;о ства, отличающееся трм, что, с целью сокращения затрат обору4: N9 дования и повьшения точности вычислений, оно содержит блок постоянной памяти, причем вход блока постоянной памяти соединен с входом угла поворота устройства, выходы блока постоянной памяти с первого по ni/2-й соединены с знаковыми входами сумматороввычитателей соответствукндих итерационных блоков, выходы блока постоянной памяти с ih72+l)-ro по rj-й соединены с знаковыми входами первого и второго сумматоров-вычйтателей соответствующих итерационных блоков.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Арифметическое устройство | 1978 |

|

SU706846A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-08-23—Публикация

1982-08-11—Подача