1476462

первого аргумента, вход 8 второго В узле коррекции производится коррек- аргумента, вход 9 угла, В итерацион- ция координат вектора, необходимая ных узлах осуществляются вычисления из-за деформации вектора при его по- в соответствии с алгоритмом Волдера. вороте,, 1 з.п. ф-лы, 1 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления элементарных функций | 1986 |

|

SU1310812A1 |

| Функциональный преобразователь | 1983 |

|

SU1136154A1 |

| Функциональный преобразователь | 1980 |

|

SU924714A1 |

| Конвейерное вычислительное устройство | 1987 |

|

SU1432512A1 |

| Цифровой преобразователь координат | 1981 |

|

SU1076903A1 |

| Цифровое устройство для вычисления синусно-косинусных функций | 1980 |

|

SU868753A1 |

| Устройство для вычисления тригонометрических функций | 1986 |

|

SU1332313A1 |

| Устройство для вычисления направляющих косинусов вектора в пространстве | 1982 |

|

SU1164700A1 |

| Вычислительное устройство | 1986 |

|

SU1361546A1 |

| Устройство для поворота вектора | 1982 |

|

SU1076910A1 |

Изобретение относится к вычислительной технике и может быть применено в специализированных процессорах. Целью изобретения является повышение точности вычисления за счет введения быстродействующих средств коррекции аргументов. Устройство содержит N итерационных узлов 1.1...1.N (N - разрядность аргументов), N узлов коррекции 2.1.....2.N, блок 3 памяти коэффициентов, первый тактовый вход 4, второй тактовый вход 5, вход 6 логического нуля, вход 7 первого аргумента, вход 8 второго аргумента, вход 9 угла. В итерационных узлах осуществляются вычисления в соответствии с алгоритмом Волдера. В узле коррекции производится коррекция координат вектора, необходимая из-за деформации вектора при его повороте. 1 з.п. ф-лы, 1 ил.

1

Изобретение относится к вычислительной технике и может быть применено в специализированных процессорах,,

Целью изобретения является повышение точности вычисления за счет введения быстродействующих средств коррекции аргументов.

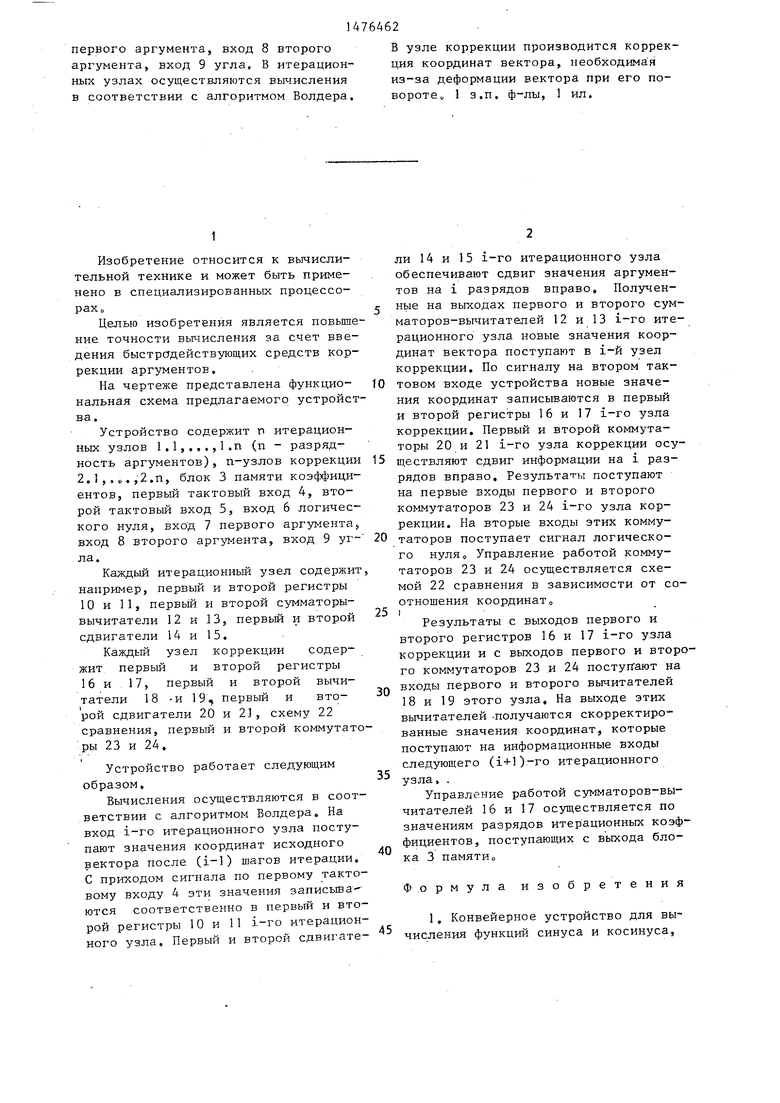

На чертеже представлена функцио- нальная схема предлагаемого устройства.

Устройство содержит п итерационных узлов 1.1,.,.,1.п (п - разрядность аргументов), n-узлов коррекции 2.,.«.,2,п, блок 3 памяти коэффициентов, первый тактовый вход 4, второй тактовый вход 5, вход 6 логического нуля, вход 7 первого аргументаs вход 8 второго аргумента, вход 9 уг- ла.

Каждый итерационный узел содержит например, первый и второй регистры 10 и 11, первый и второй сумматоры- вычитатели 12 и 13, первый и второй сдвигатели 14 и 15.

коррекции содер- второй регистры 16 и 17, первый и второй вычи- татели 18 -и 19. первый и вто-

If

рой сдвигатели 20 и 2J, схему 22 сравнения, первый и второй коммутаторы 23 и 24,

Каждый уз ел жит первый и

Устройство работает следующим образом.

Вычисления осуществляются в соответствии с алгоритмом Волдера, На вход 1-го итерационного узла поступают значения координат исходного вектора после (i-1) шагов итерации, С приходом сигнала по первому тактовому входу 4 эти значения записываются соответственно в первый и второй регистры 10 и 11 i-ro итерационного узла, Первый и второй сдвигатели 14 и 15 1-го итерационного узла обеспечивают сдвиг значения аргументов на i разрядов вправо. Полученные на выходах первого и второго сум- маторов-вычитателей 12 и 13 1-го итерационного узла новые значения координат вектора поступают в 1-й узел коррекции. По сигналу на втором тактовом входе устройства новые значения координат записываются в первый и второй регистры 16 и 17 1-го узла коррекции. Первый и второй коммутаторы 20 и 21 1-го узла коррекции осуществляют сдвиг информации на i разрядов вправо. Результаты поступают на первые входы первого и второго коммутаторов 23 и 24 1-го узла коррекции. На вторые входы этих коммутаторов поступает сигнал логического нуля о Управление работой коммутаторов 23 и 24 осуществляется схемой 22 сравнения в зависимости от со

i

отношения координат о

Результаты с выходов первого и второго регистров 16 и 17 1-го узла коррекции и с выходов первого и второго коммутаторов 23 и 24 постуггают на входы первого и второго вычитателей 18 и 19 этого узла. На выходе этих вычитателей -получаются скорректированные значения координат, которые поступают на информационные входы следующего (1+1)-го итерационного узла, .

Управление работой сумматоров-вы- читателей 16 и 17 осуществляется по значениям разрядов итерационных коэффициентов, поступающих с выхода блока 3 памяти

Формула изобретения

1, Конвейерное устройство для вычисления функции синуса и косинуса,

содержащее n-итераиионных узлов (п - разрядность аргумента) и блок памяти, коэффициентов, причем вход угла уст-1 ройства соединен с адресным входом блока памяти коэффициентов, i-й выход которого (,„„о9п) соединен с входом управления итерацией 1-го итерационного узла, первый тактовый вход устройства соединен с одноимен- ным входом каждого итерационного узла, отличающееся тем, что, с целью повышения точности, в него введены n-узлов коррекции, причем первый и второй информацион- ные выходы j-ro итерационного узла (,...,п-1) соединены соответственно с первым и вторым информационными входами (j+l)-ro итерационного узла, второй тактовый вход устройства сое- динен с тактовым входом всех узлов коррекции, вход логического нуля устройства соединен с одноименным входом всех узлов коррекции, первый и второй информационные входы первого итерационного узла соединены с входами первого и второго аргументов устройства, первый и второй выходы п-го узла коррекции соединены соответственно с первым и вторым выходами ре- зультата устройства.

два сдвигателя, два коммутатора, два вычитателя и схему сравнения, причем первый и второй информационные входы узла коррекции соединены с информационными входами соответственно первого и второго регистров, синхронизирующие входы первого и второго регистров соединены с тактовым входом узла коррекции, выход первого регистра соединен с входом уменьшаемого первого вычитателя и информационным входом первого сдвигателя, выход второго регистра соединен с входом уменьшаемого второго вычитателя и информационным входом второго сдвигателя, выходы первого и второго сдвигателей соединены с первыми информационными входами соответственно первого и второго коммутаторов, вторые информационные входы которых соединена с входов логического нуля узла коррекции, выходы первого и второго коммутаторов соединены с входом вычитаемого соответственно первого и второго вычитателей, управляющие входы первого и второго коммутаторов соединены соответственно с первым и вторым выходами схемы сравнения, входы первого и второго операндов которой соединены с выходами соответственно первого и второго регистров, выходы первого и второго вычитателей, соединены с первым и вторым информационным выходами узла коррекции.

| Устройство для вычисления тригонометрических функций | 1984 |

|

SU1236465A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Байков Б.Д., Смолов В.Б | |||

| Специализированные процессоры | |||

| Итерационные алгоритмы и структуры | |||

| М.: Радио и связь, 1985, с | |||

| Способ образования азокрасителей на волокнах | 1918 |

|

SU152A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1989-04-30—Публикация

1987-10-22—Подача