1

Изобретение относится к вычислительной технике и может быть использовано при построении специализированных ЭВМ.

В предпагаемом изобретении приводится техническое решение задачи преобразования декартовых координат в полярные с одновременным умножением координат векторг на экспоненту, т.е. вычисления вьфажений сдедукще-. го вида:

( А - arctg (Y/X) ,

где X,Y - декартовы координатыГабсцис- са и ордината) вектора;

М,А - полярные координаты I модуль и аргумент) вектора;

Т - аргумент экспоненты.

При Т О выполняется преобразование декартовых координат в полярные с компенсацией изменения масштаба координат.

Целью изобретения является расши- рение области применения устройства за счет возможности преобразования в экспоненциальном масштабе.

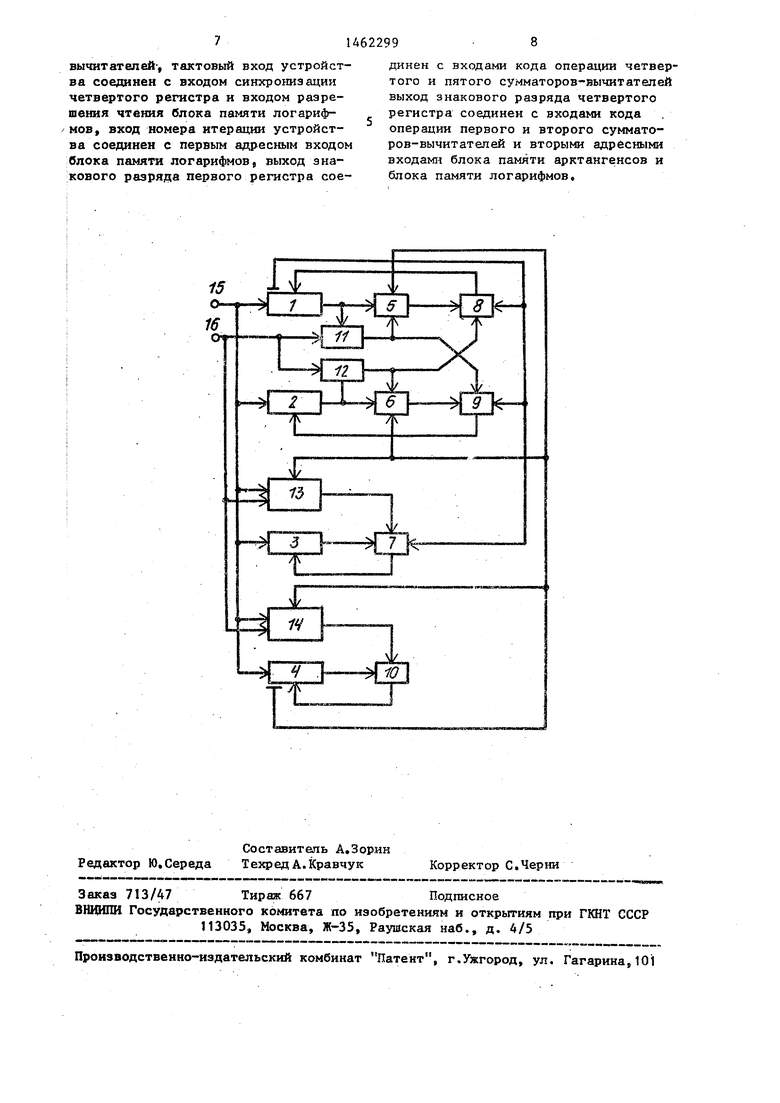

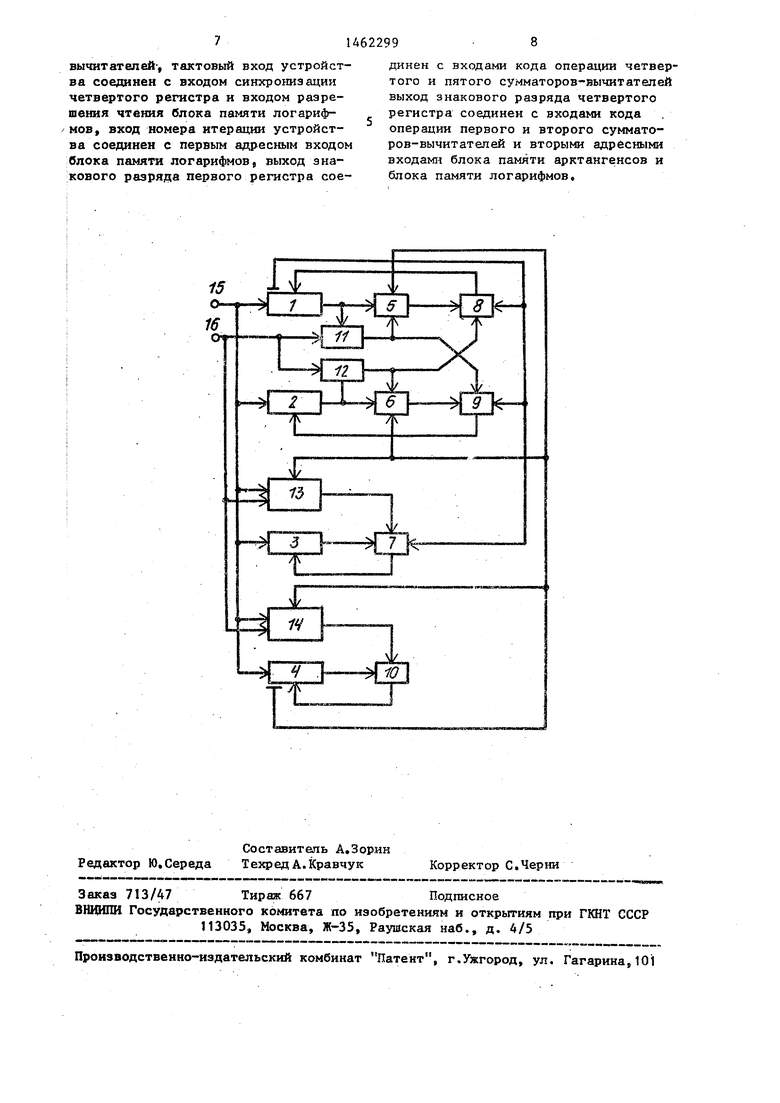

На чертеже представлена блок-схема предлагаемого устройства для выполнения преобразования координат.

Устройство для выполнения преобразования координат содержит регистры 1-4, сумматоры-вычитатели 5-9,

а

1ч9 Ю

СО

со

вычитатель 10, сдвигатели II и 12, блоки 13 и 14 памяти арктангенсов и логарифмов, тактовый вход 15, вход 16 номера итерации.

Введем следующие обозначегшя, поясняюпще работу устройства: А,, В ордината и абсцисса вектора, повернтые на угол Сд; Од - переменная

алх оритма, используемая для преобра аования аргумента экспоненты на л-о

шаге; ЕдС -1, + 1 - оператор направления изменения аргумента вектор

; на л-ом шаге алгоритма; P -1 -ц ; оператор направления изменения мо дуля вектора на л-ом иаге алгоритi ма; л - сквозной номер шага от нача:ла вычислений; к - номер выполняемой итерации; п - количество разря.дов в дробной части числа, количест: во выполняемых итераций; (п + 3) ; разрядность устройства, включая два

; разряда в целой части шсла и знаковый .

Область определения функций:

06(Y)1; 0 (Т) $ I. Области значений функций: 06/arctg(Y/X)/ ir/4}

е- /2 е. (

-и

Устройство реализует следующий алгоритм преобразования декартовых координат в полярные.

Начальные условия:

S

(А,); (D, );

(1)

(2) (3)

(4)

(5) (6) (7) (8) arctg((l+P,- 2); (9)

.

„ A,.B,.2- j В.,- 2 +ЕЯ-А,- 2-%

Эд,, Бд-0,51п(,.

) (10)

где л 1,2s,,,.,2n

4 1)12 для нечетных л/2 для четных л

Результатыг

Чп+г

О,

03)

Sn + i

D.nv, .. , г г - (. t Y J

(X V)S

arctg (Y/X);

0

(14) (15) (16)

При Т О устройство выполняет преобразование декартовых координат X и Y в полярные

(/2.

и А arctg (Y/X)

без искажения модуля вектора, а при Y О вычисляет функцию М X. е , В исходном положении (см, блок 5 схему устройства) в регистрах находятся следующие данные:

в первом регистре 1 ордината вектора Y; во втором регистре 2 абсцисса вектора X; в третьем регистре 3 число 0 в четвертом регистре 4 аргумент экспоненты Т.

Таким образом, реализованы выражения (1) - (4).

Устройство работает циклически.

25 На л-ом шаге на тактовый вход 15 устройства подается синхросигнал, на вход номера итерации б устройства - номер К выполняемой итерации. При этом двум синхросигналам соответ0 ствует одно значение номера выполняемой итерации, т.е. используются двойные шаги итераций в соответствии с выражениями (11) и (12), Под воздействием синхросигналов и номеров итераций в устройстве развивается вычислительный процесс.

Под воздействием каждого синхросигнала реализуется един шаг алгоритма в соответствии с выражениями (5) 0 (10).

Режимы работыf сложение или вычитание V третьего 7, четвертого 8, пятого 9 сумматоров-вычитателей задает сигнал с выхода знакового разряд да первого регистра 1 - выражение (5). Режимы работы (сложение или вычитание) первого 5 и второго 6 сумматоров-вычитателей задают сигнал с выхода знакового разряда четвертог го регистра 4. Этот же сигнал управляет выбором соответствующей константы в блоках 13 и 14 памяти - выражение (6). В соответствии с номером выполняемой итерации в первом 11 и втором 12 сдвигателях выполняется сдвиг дыдущих значений соответственно ординаты Ад и абсциссы Вд вектора на К разрядов вправо, т.е. на выходах

0

5

первого 11 н второго 12 сдвигателей формируются величины соответственно Ад . и БД- 2. Предыдущее значение ординаты вектора Ад, ее приращения и Вд- поступают соответственно из первого регистра 1 , первого 11 и второго 12 сдвигателей в цепь, состоящую из первого 5 и четвертого 8 сумматоров-вычитателей, в резульате в четвертом сумматоре- вычитателе 8 формируется новое значение ординаты вектора А,., , которое фиксируется в первом регистре 1 - выражение 7), Предыдущее значение абсциссы вектора В, ее приращения и 2 поступают соответственно из второго регистра 2, второго 12 и пер вого 11 сдвигателей в цепь, состоящую из второго 6 и пятого 9 сумматоров-вычитателей, в результате в пятом сумматоре-вычитателе 9 формируется иовое значение абсциссы вектора которое фиксируется во втором регистре 2 - выражение (8)

Предыдущее значение аргумента вектора Сл и арктангенсная константа arctg ( (1 4- Р. 2) поступают соответственно из третьего регистра 3 и блока 13 памяти арктангенсов в третий сумматор-вычитатель 7, где формируется новое значение аргумента вектора Сд.,, которое фиксируется в третьем регистре 3 - выражение (9).

Предыдущее значение преобразованного аргумента D экспоненты и логарифмическая константа 0,5 In (1 + + 2 + ) поступают соответственно из четвертого регистра 4 и блока 14 памяти логарифмов в вычи- татель 10, где формируется новое значение преобразованного аргумента Вд экспоненты, которое фиксируется в четвертом регистре 4 .- выражение (10).

Все итерационные шаги выполняются в устрсйстве аналогично рассмотренному.

После выполнения п итераций с двойными шагами в регистрах зафиксированы следующие результаты: в первом регистре 1 А, 0; во втором регистре 2 , & (хЧу) 1/2; в третьем регистре 3 С„, arctg(Y/X) ; в четвёртом регистре 4 Din., О.

Таким образом, реализованы вьфа- жения (13) - (16).

622996

Формула изобретенй я

Устройство для выполнения преобра- зования координат , содержащее три i регистра, три сумматора-вычитателя, два сдвигателя и блок памяти арктангенсов, причем выходы первого и второго регистров соединены с информа- 10 ционными входами соответственно первого и второго сдвигателей, входы первого операнда первого и второго сумматоров-вычитателей соединены с выходами соответственно первого и 5 второго регистров, тактовьш вход устройства соединен с входами синхронизации первого, второго и третьего регистров и с входом разрешения чтения блока памяти арктангенсов, вход но 20 мера итерации устройства соединен с входами сдвига первого и второго сдвигателей и с первыми адресными входами блока памяти арктангенсов, выход знакового разряда первого 25 регистра соединен с входом кода oner рации третьего сумматора-вычитателя, вход первого операнда которого соединен с выходок блока памяти арктангенсов, вход второго операнда . 30 третьего сумматора-вычитателя соединен с выходом третьего регистра, выход третьего сумматора-вычитателя .соединен с информационным входом третьего регистра отлич ающе- е с я тем, что, с целью расширения области применения за счет возможности преобразования в экспоненциальном масщтабе, в него введены четвертый регистр, четвертый и пятый Q сумматоры-вычнтатели, вычитатель и . блок памяти логарифмов, выход которого соединен с входом вычитаемого вы- читателя, вход уменьшаемого которого соединен с выходом четвертого ре- дс гистра, выход вычитателя соединен с информационным входом четвертого ре- , гистра, выходы первого и второго сумматоров-вычитателей соединены с входами первого операнда соответст- CQ венно четвертого и пятого сумматоров-вычитателей, выходы которых соединены с информшщонными входами соответственно первого и второго регистров, выход первого сдвигателя соединен с входами второго операн55

да первого и пятого сумматоров-вычитателей, выход второго сдвигателя соединен с входами второго операнда второго и четвертого сумматороввычитателей тактовый вход устройства соединен с входом синхронизации четвертого регистра и входом разрешения чтения блока памяти логариф- / нов, вход номера итерации устройства соединен с первым адресным входом блока памяти логарифмов, выход знакового разряда первого регистра соединен с входами кода операции четвертого и пятого сумматоров-вычитателей выход знакового разряда четвертого регистра соединен с входами кода операции первого и второго сумматоров-вычитателей и вторыми адресными входами блока памяти арктангенсов и блока памяти логарифмов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления эллиптических функций | 1987 |

|

SU1474641A2 |

| Устройство для вычисления логарифма | 1987 |

|

SU1432513A1 |

| Устройство для вычисления функций | 1986 |

|

SU1374219A1 |

| Вычислительное устройство | 1988 |

|

SU1508208A1 |

| Устройство для вычисления квадратного корня | 1986 |

|

SU1397904A1 |

| Устройство для вычисления обратного гиперболического тангенса | 1987 |

|

SU1456952A1 |

| Устройство для вычисления тригонометрических функций | 1986 |

|

SU1370653A1 |

| Вычислительное устройство | 1986 |

|

SU1322270A1 |

| Устройство для вычисления тригонометрических функций | 1986 |

|

SU1332313A1 |

| Векторный процессор | 1979 |

|

SU849228A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении специапизиро-, ванных ЭВМ. Целью изобретения явля- ется расширение области применения . за счет выполнения преобГ)азования в экспоненциальном масштабе. Устройство преобразует декартовые координаты в полярные с компенсацией изменения масштаба координат вектора и, . кроме того, позволяет .вычислять функцию М Х.. Для этого в устройство, содержащее три регистра, три сумматора-вычитателя, два сдвига- теля, первый блок памяти, введены четвертый регистр, четвертый и пятый сумматоры-выч11татели, вычитатель, .второй блок памяти, 1 ил. S

| .Рабинович З.Л., Раманаускас В.А | |||

| Типовые операции в вычислительных машинах, - Киев., Техника, 19BOj с | |||

| Ветряный много клапанный двигатель | 1921 |

|

SU220A1 |

| Аппаратурная реализация элементарных функций в ЦВМ --Л.; из-во Ленинградского университета, 1975 - с, 19, 71 (прототип) . | |||

Авторы

Даты

1989-02-28—Публикация

1987-07-06—Подача