каскада, выходы первого, второго и третьего сумматоров-вычитателей последнего каскгида преобразователя соединены соответственно с первым, вторым и третьим выходами результата преобразователя, отличающееся тем, что, с целью повышения точности -вычислений, каждый из каскадов преобразователя с (j + 1)-го

по(п-1)-й содержит первый, второй и третий блоки запрета итераций, первые и вторые входы которых соединены соответственно с первыми и вторыми выходами соответственно первого второго и третьего коммутаторов, первые и вторые управляющие входы которых соединены соответственно с третьими и четвертыми входами соответственно первого, второго и третьего блоков запрета итераций, пятые входы которых соединены с разрядными выходами соответственно первого, второго и третьего регистров, номера которых равны номеру соответствующего каскада, знаковые разряды первого второго и третьего регистров соединены с шестыми входами соответственно первого, второго и третьего блоков запрета итераций, первые к вторые выходы первого, второго и третьего блоков запрета итераций соединены соответственно с первыми и вторыми управляющими входами соответственно первого, второго и третьего сумматоров-вычитателей.

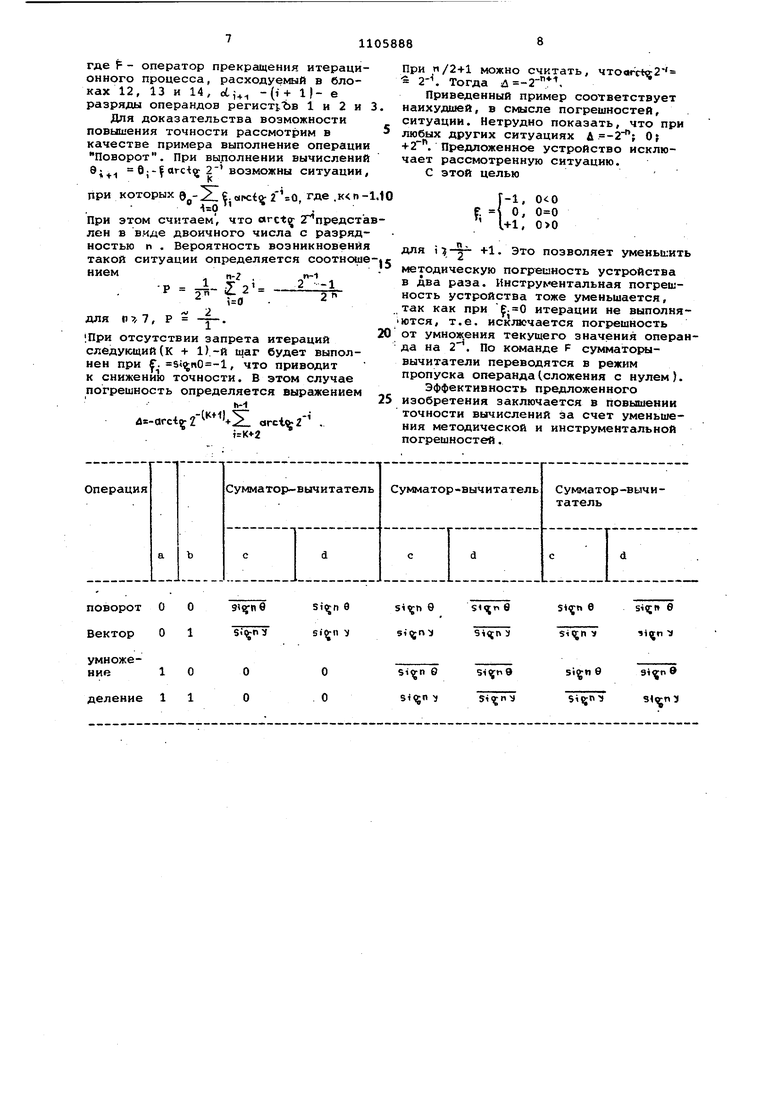

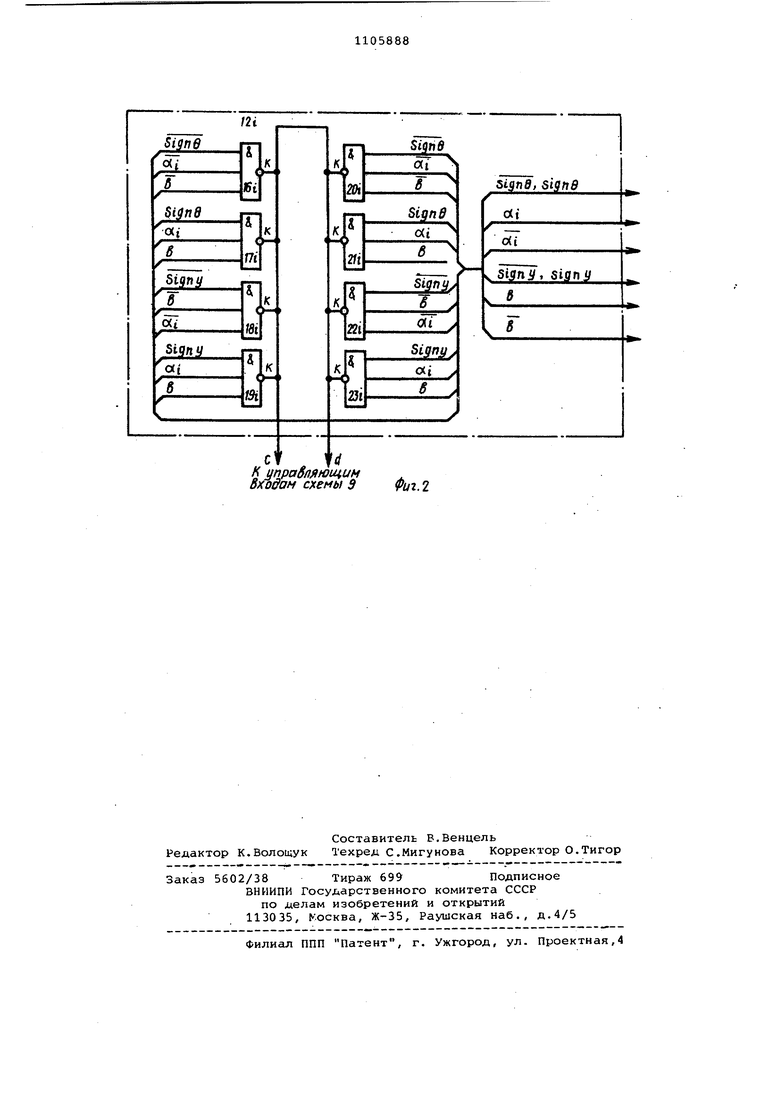

2. Преобразователь по п. 1, о тличающийся тем, что кaжJqый блок запрета итераций содержит с первого по восьмой элементы И-НЕ, причем первые информационные входы первого, второго,пятого и шестого элементов И-НЕ соединены с первым входом блока запрета итераций, второй вход которого соединен с вторыми информационными входами второго, четвертого, шестого и восьмого элементов И-НЕ, вторые информационные входы первого5 третьего, пятого и седьмого элементов И-НЕ соединены с третьим входом блока запрета итераций, четвертый вход которого соединен с первым} и вторыми информационными входами третьего, четвертого, седьмого и восьмого элементов И-НЕ, третьи информационные входы четвертого, шестого и восьмого элементов И-НЕ соединены с пятым экодом блока запрета итераций, шестой вход которого соединен с третьими информационными входами первого, т ретьего,пятого и седьмого элементов И-НЕ, информационные инвеные выходы с первого по четвертый элементов И-НЕ соединены с первым информационньа выводом блока запрет итераций, второй информационный выход которого соединен с информационными инверсными выходами с шестого по восььюй элементов И-НЕ блока запрета итераций.

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство | 1981 |

|

SU1136147A1 |

| Цифровой функциональный преобразователь | 1980 |

|

SU991419A2 |

| Цифровой функциональный преобразователь (варианты) | 1981 |

|

SU1015375A1 |

| Устройство для определения модуля трехмерного вектора | 1983 |

|

SU1142830A1 |

| Функциональный преобразователь | 1983 |

|

SU1136154A1 |

| Цифровой функциональный преобразователь | 1980 |

|

SU911522A1 |

| Вычислительное устройство | 1981 |

|

SU959071A1 |

| Устройство для деления в системе остаточных классов | 1983 |

|

SU1141400A1 |

| Устройство для вычисления направляющих косинусов вектора в пространстве | 1982 |

|

SU1164700A1 |

| Устройство для вычисления функции | 1986 |

|

SU1348829A1 |

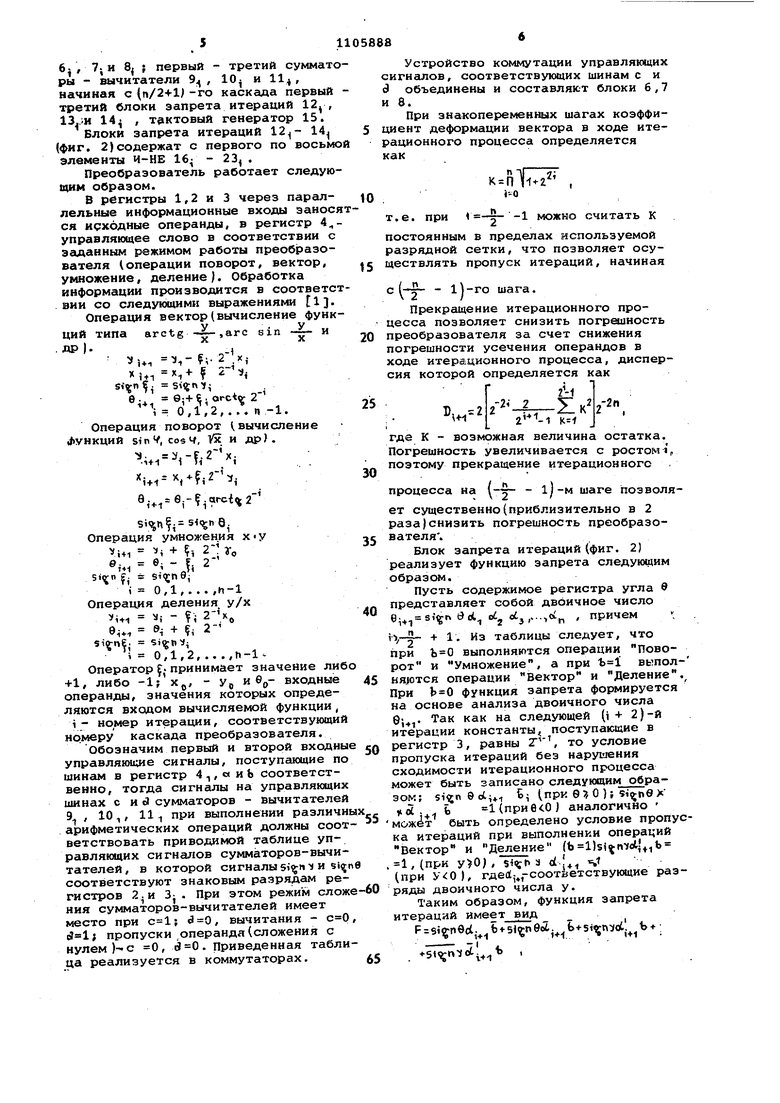

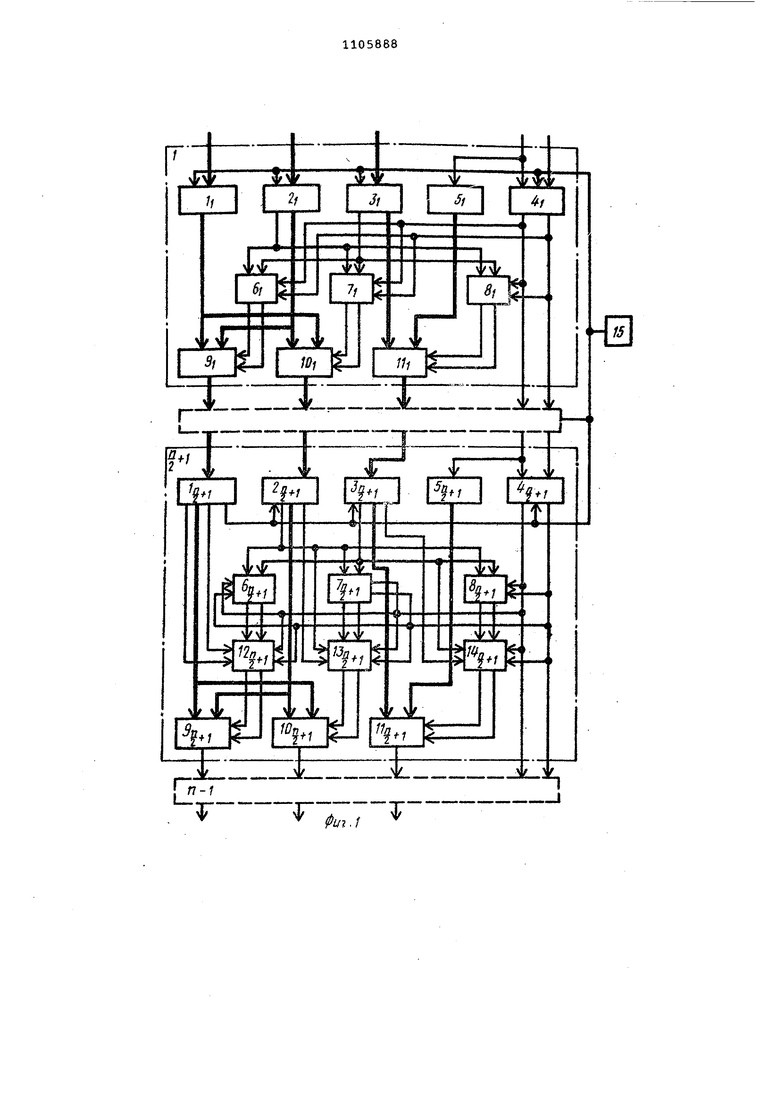

Изобретение относится к вычислительной технике и может быть исполь зовано в устройствах для вычисления элементарных функций с использовани ем итерационных вычислительных алго ритмов. Известно устройство, использующее для вычисления элементарных функций (x/y,Vx,sin X, cos X, е. In х, arctg X,...) итерационные алгорит и цифра за цифрой и содержащее регистры, сдвигатели, сумматоры, посто янные запоминающие устройства 1. Недостатком данного устройства является сравнительно низкое быстродействие и значительная поргрешность вычисления, обусловленная в основном погрешностью усече ния операндов в ходе итерационного процесса. Наиболее близким по технической сущности к предложенному устройству является арифметическое устройство, .содержащее п последовательно соединенных каскадов,каждый из которых содержит четыре регистра хранения,три параллельных сумматора-вычитателя,постоянное запоминающее устройство,коммутационное устройство, тактовый генератор 2. Недостатком указанного устройства является низкая точность вычисления элементарных функций, что обусловлено наличием погрешности усечения операндов в ходе итерационного процесса. Цель изобретения - повышение точности вычислений преобразователя . Поставленная цель достигается тем, что в преобразователь, содержащий тактовый генератор и п-1(где ji разрядность операндов)последовательно соединенных каскадов, причем каждый из каскадов содержит с первого по четвертый регистры, 6JJOK памяти, первый, второй и третий коммутаторы, первый, второй и третий сумматорывычитатели, тактовые входы регистров с первого по четвертый соединены между собой и подключены к выходу тактового генератора, адресная шина блока памяти соединена с первым информационным входом четвертого регистра, разрядный выход первого регистра соединен с первым информационным входом первого сумматоравычитателя и вторым информационным входом второго сумматора-вычитателя со сдвигом вправо на число разрядов равное номеру, каскада, первый информационный вход второго сумматоравычитателя соединен с вторым информационным входом первого сумматоравычитателя, разрядный выход второго регистра соединен с вторым информационным входом первого сумматоравычитателя со сдвигом вправо на числ разрядов, равное номеру каскада, разрядный выход третьего регистра соединен с первым информационным входом третьего сумматора-вычитателя второй информационный вход которого соединен с информационной шиной данных блока памяти, знаковый разряд второго регистра соединен с первыми информационными входами первого, второго и третьего коммутаторов, вто рые информационные входы которых соединены с выходом знакового разряд третьего регистра, первый информационный выход четвертого регистра соед нен с первыми управляющими входами первого, второго и третьего коммута торов , вторые управляющие входы которых соединены с вторым информацио ным выходом четвертого регистра, пр чем в каждом из первых п/2 каскадов преобразователя первые и вторые информационные выходы первого, втог рого и третьего коммутаторов соединены соответственно с первыми и вто рыми управляющими входами соответст венно первого, второго и третьего сумматоров-вычитателей, причем разрядные входы первого, второго и третьего регистров первого каскада соединены соответственно с первым, вторым и третьим информационными входами преобразователя, четвертый и пятый информационные входы которо го соединены соответственно с первы и вторым информационными входами четвертого регистра, выходы первого второго и третьего сумматоров-вычитателей каждого каскада преобразователя соединены с разрядными входа ми соответственно первого, второго и третьего регистров последующего каскада, первый и второй выходы чет вертого регистра каждого каскада соединены соответственно с первым и вторым информационными входами четвертого регистра последующего ка када, выходы первого, второго и третьего сумматоров-вычитателей последнего каскада преобразователя соединены соответственно с первым, вторым и третьим выходами результата преобразователя, в каждый из каскадов преобразователя +l|-r по (п-1)-й дополнительно введены первый, второй и третий блока запрета итераций,первые и вторые входы которых соединены соответственно с первыми и:вторыми выходами соответственно первого, второго и третьего коммутаторов, первые и вторые управляющие входы которых соединены соответственно с третьими и че вертыми входами соответственно первого, второго и третьего блоков запрета итераций, пятые входы которых соединены с разрядными выходами соответственно первого, второго и третьего регистров, номера которых равны номеру соответствующего каскада, знаковые разряды первого, второго и третьего регистров соединены с шестыми входами соответственно первого, второго и третьего блоков запрета итераций, первые и вторые выходы первого, второго и третьего блоков запрета итераций соединены соответственно с первыми и вторыми управляющими входами соответственно первого, второй и третьего сумматоров-вычитателей. Кроме того,каждый блок запрета итераций содержит с первого по восьмой элементы И-НЕ, причем первые информационные входы первого, второго, пятого и шестого элементов И-НЕ соединены с первым входом блока запрета итераций, второй вход которого соединен с вторыми информационными входами второго, четвертого, шестого и восьмого элементов И-НЕ, вторые информационные входы первого, третьего, пятого и седьмого элементов И-НЕ соединены с третьим входом блока запрета итераций, четвертый вход которого соединен с первыми и вторыми информационными входами третьего, четвертого, седьмого и восьмого 5лементов И-НЕ, третьи информационные входы четвертого, шестого и восьмого элементов И-НЕ соединены с пятым входом блока запрета итераций, шестой вход которого соединен с третьими информационными входами первого, третьего, пятого и седьмого элементов И-НЕ, информационные инверсные выходы с первого по четвертый элементов И-НЕ соединены с первым информационным выходом блока запрета итераций, второй информационный выход которого соединен с информационными инверсными выходами с шестого по восьмой элементов И-НЕ блока запрета итераций. На фиг. 1 представлена функциональная схема преобразователя; на фиг. 2 - функциональная схема блока запрета итераций. Преобразователь(фиг. 1) содержит последовательно соединенные каскады, каждый из которых содержит первый четвертый регистры 1, 2|, 3, и 4 (где i- номер каскада I, блок памяти 5 i , первый - третий коммутаторы 6, 7. и 8 ; первый - третий суммато ры - вычитатели 9. , 10 и И г начиная с (п/2+1)-го каскада первый третий блоки запрета итераций 12, 13.;и 14 , тактовый генератор 15. Блоки запрета итераций 14 (фиг. 2(содержат с первого по восьмо элементы И-НЕ 16 - 23, . Преобразователь работает следующим образом. В регистры 1,2 и 3 через параллельные информационные входы занося ся исходные операнды, в регистр 4 управлякхцее слово в соответствии с заданным режимом работы преобразователя (операции поворот, вектор, умножение, деление ). Обработка информации производится в соответст ВИИ со следующими выражениями t Операция вектор(вычисление функций типа arctg- -,агс sin и .ДР). , vu. 1- ; 2 X,. ЬЧт 1+1 2- . . е-, е;+. 0,1,2,... и -1. Операция поворот . вычисление функций sinV, сое ч, Vx и др). 4u, 9,.-|.с,гоЦ2 Ч г Ч б, Операция умножения i + -, 2-; То в- е - i 0,1, . . . ,h-l Операция деления, у/х Vi - i 2-Ч, 9i. 9i + i 2SifdE. i 0,1,2,...,h-l Оператор fj принимает значение либ +1, либо -I; Хр, - Уд и вр- входные операнды, значения которых определяются входом вычисляемой функции, i- итерации, соответствующий номеру каскада преобразователя. Обозначим первый и второй входны управляющие сигналы, поступающие по шинам в регистр 4, а иЬ соответственно, тогда сигнсшы на управляющих шинах сии сумматоров - вычитателей 9 , 10,, 11 при выполнении различн арифметических операций должны соот ветствовать приводимой таблице управляющих сигналов сумматоров-вычитателей, в которой сигналы signs и ei соответствуют знаковым разрядам регистров 2 и 3- . При этом режим слож ния сумматоров-вычитателей имеет место при , вычитания - пропуски операнда(сложения с нулем )-с 0, . Приведенная табли ца реализуется в коммутаторах, Устройство коммутации управляющих сигналов, соответствующих шинам с и 3 объединены и составляют блоки 6,7 и а. При знакопеременных шагах коэффициент деформации вектора в ходе итерационного процесса определяется как K-nTJT , I--0 -1 можно считать к т.е. при постоянным в пределах используемой разрядной сетки, что позволяет осуществлять пропуск итераций, начиная с (- - шага. Прекращение итерационного процесса позволяет снизить погрешность преобразователя за счет снижения погрешности усечения операндов в ходе итерационного процесса, дисперсия которой определяется как КИ где К - возможная величина остатка. Погрешность увеличивается с ростом, поэтому прекращение итерационного процесса на (- - I)-M шаге позволяет существенно(приблизительно в 2 раза{снизить погрешность преобразователя. Блок запрета итераций (фиг. 2) реализует функцию запрета следующим образом. Пусть содержимое регистра угла 9 представляет собой двоичное число 2 з«--- г. причем ; i),-- + 1. Из таблицы следует, что при выполняются операции Поворот и Умножение, а при вьшолня отся операции Вектор и Деление., При функция запрета фо1 1ируется на основе анализа двоичного числа 9,+,. Так как на следующей (i + 2)-й итерации константы поступающие в регистр 3, равны то условие пропуска итераций без нарушения сходимости итерационного процесса может быть записано следующим образок; Ь (при е О )f цоС. . b 1(прив.0 аналогично мож4т быть определено условие пропуска итераций при выполнении операций Вектор и Деление ()sitm(ot|+ib 1,(при ) , i 1+1 V (при ), гдей,-соответствующие разряды двоичного числа у. Таким образом, функция запрета итераций имеет вид F siijn9cij fet5i n0 i. т 1. . + 5«9j w-v+i где F- оператор прекращения итерационного процесса, расходуемый в блоках 12, 13 и 14, ot,-+ -(i+ 1)- е разряды операндов регист11Ьв 1 и 2 и Для доказательства возможности повышения точности рассмотрим в качестве примера выполнение операции Поворот. При выполнении вычислений 9;. в;-f arc-l возможны ситуации при которых Э--2 . arete где .к п При этом считаем, что arct З предста лен в виде двоичного числа с разряд ностью п , Вероятность возникновения такой ситуации определяется cooTHOuie 1 п-2 . -Р 2 -il2 для и : 7 , Р При отсутствии запрета итераций следующий (К + 1).-й шаг будет выполнен при f. , что приводит к снижению точности. В этом случае погрешность определяется выражением Л8-с1гс г2 + . При n/2+l можно считать, чтовгг с2 2- Тогда Приведенный пример соответствует наихудшей, в смысле погрешностей, ситуации. Нетрудно показать, что при любых других ситуациях Д Of +2 . Предложенное устройство исключает рассмотренную ситуацию. С этой целью нf -U; для t . Это позволяет умены1:ить методическую погрешность устройства в два раза. Инструментальная погрешность устройства тоже уменьшается, так как при .0 итерации не выполняЮТСЯ, т.е. иск асчается погрешность от умножения текущего знач1ения операнда на 2. По кс 1анде Р сумматорывычитатели переводятся в режим пропуска операнда(сложения с нулем). Эффективность предложенного изобретения заключается в повышении точности вычислений за счет уменьшения методической и инструментальной погрешностей.

Т

Фиг.

Л {/npagfl fomuM ам с)(ены Э

Фиг.1

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Байков В.Д.и Смолов В.Б | |||

| Аппаратурная реализация элементарных функций в ЦВМ | |||

| Л., ИЗД.-ВО ЛГУ, 1975 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

| ЦИФРОВОЙ ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ, содержащий тактовый генератор и п-1(где h-разрядность операндов)последовательно соединенных каскадов, причем каждый из каскадов содержит с первого по четвертый регистры, блок памяти, первый, второй и третий коммутаторы, первый, второй и третий сумматоры-вычитатели, тактовые входы регистров с первого по четвертый соединены между собой и подключены к выходу тактового генератора, адресная шина блока памяти соединена с первым информационным входом четвертого регистра, разрядный выход первого регистра соединен с первым информационным входом первого сумматора-вычитатёля и вторым информационным входом второго сумматора-вычитатёля со сдвигом вправо на число разрядов, равное номеру каскада, первый информационный вход второго сумматоравычитатёля соединен с вторым информационным входом первого сумматоравычитатёля, разрядный выход второго регистра соединен с вторым информационным входом первого сумматоравычитатёля со сдвигом вправо на число разрядов, равное номеру каскада, разрядный выход третье хэ регистра соединен с первыминформационным входом третьего сумматора-вычитатёля, второй информационный вход которого соединен с информационной шиной данных блока памяти, знаковый разряд второго регистра соединен с первыми информационными входами первого, второго и третьего коммутаторов, вторые информационные входы которых соединены с выходом знакового разряда третьего регистра, первый информационный выход четвертого регистра со-, единен с первыми управляющими входами первого, второго и третьего § коммутаторов, вторые управляющие входы которых соединены с вторым информационным выходом четвертого регистра, причем в каждом из первых каскадов преобразователя первые и вторые информационные выходил первого, второго и третьего коммутаторов соединены соответственно с первыми и вторыми управляющими.входами соответственно первого, второго и третьего сумматоров-вычитаО1 телей, причем разрядные входы первоСХ) го, второго и третьего регистров первого каскада соединены соответстоо, венно с первым, вторым и третьим 00 | |||

| информационными входами преобразователя, четвертый и пятый информационные входы которого соединены соответственно с первым и вторым информационными входами четвертого регистра, выходы первого, второго и третьего сумматоров-вычитателей -каждого каскада преобразователя соединены с разрядными входами соответственно первого , второго и третьего регистров последующего каскада, первый и второй выходы четвертого регистра каждого каскада соединены соответственно с первым и вторым информационными входами четвертого регистра последующего | |||

Авторы

Даты

1984-07-30—Публикация

1981-12-25—Подача