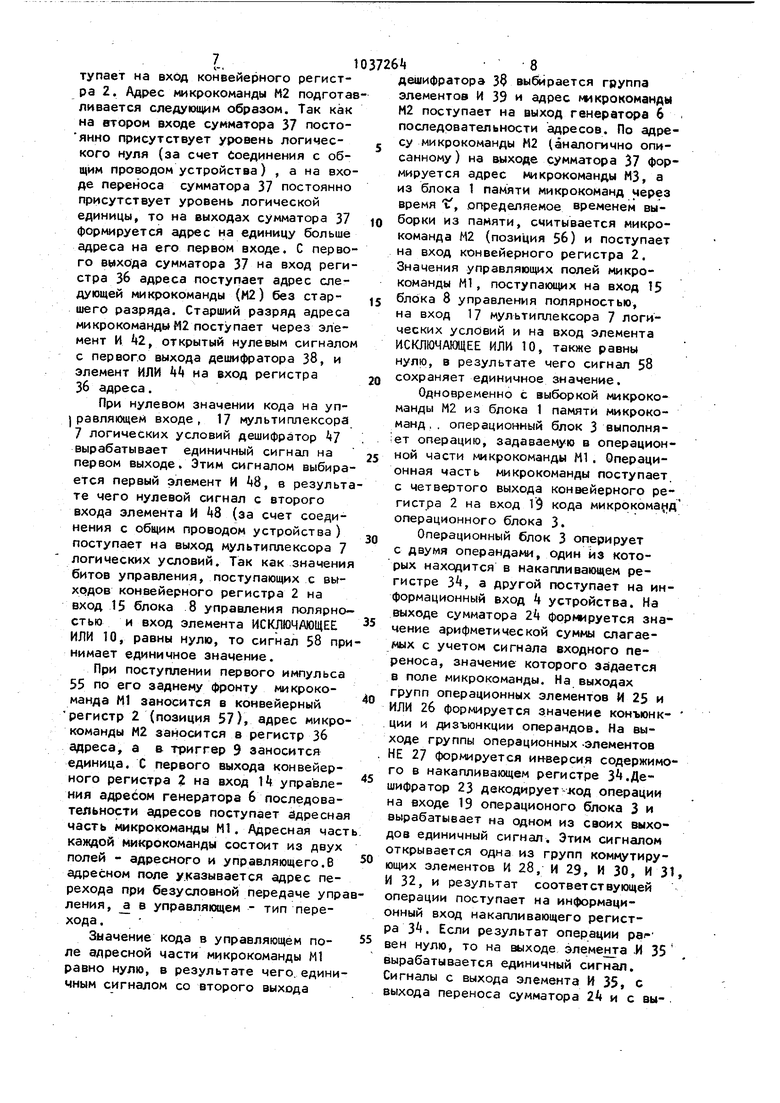

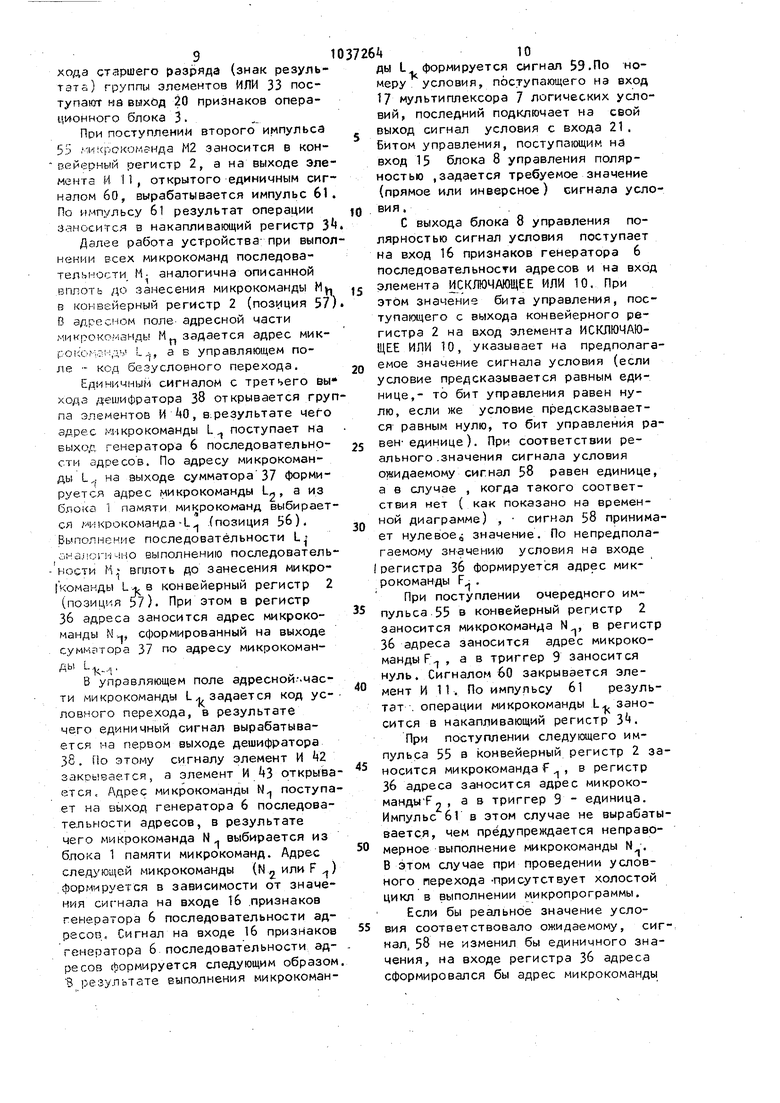

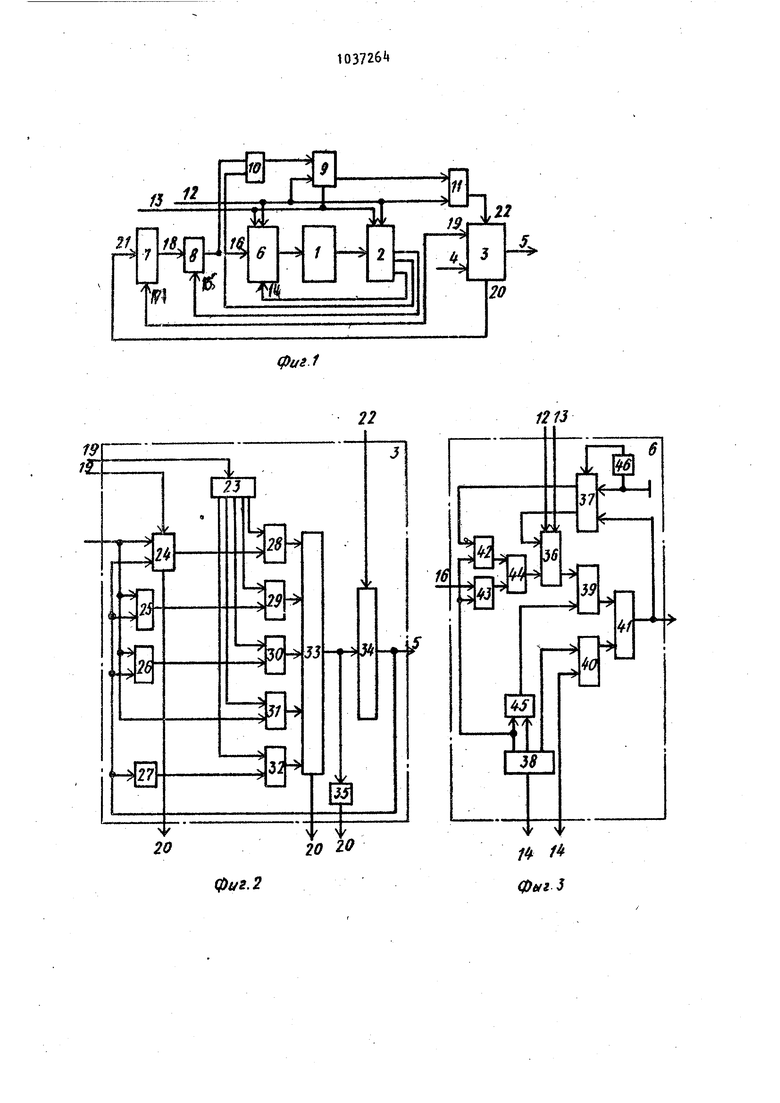

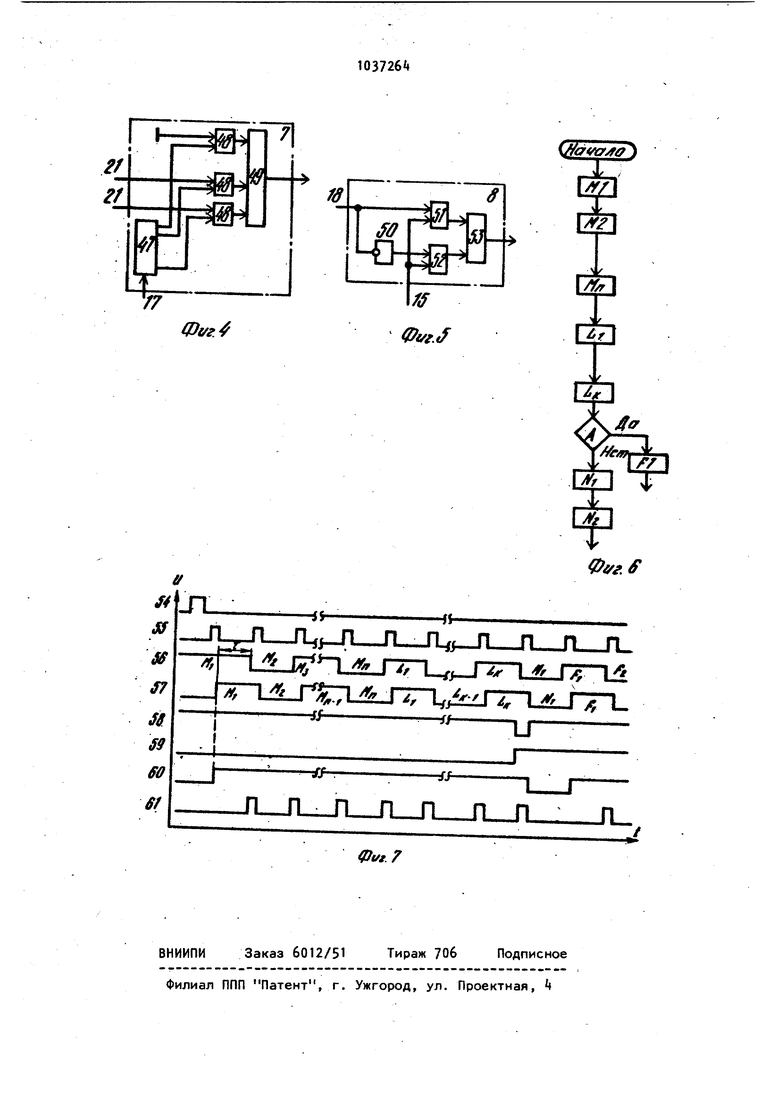

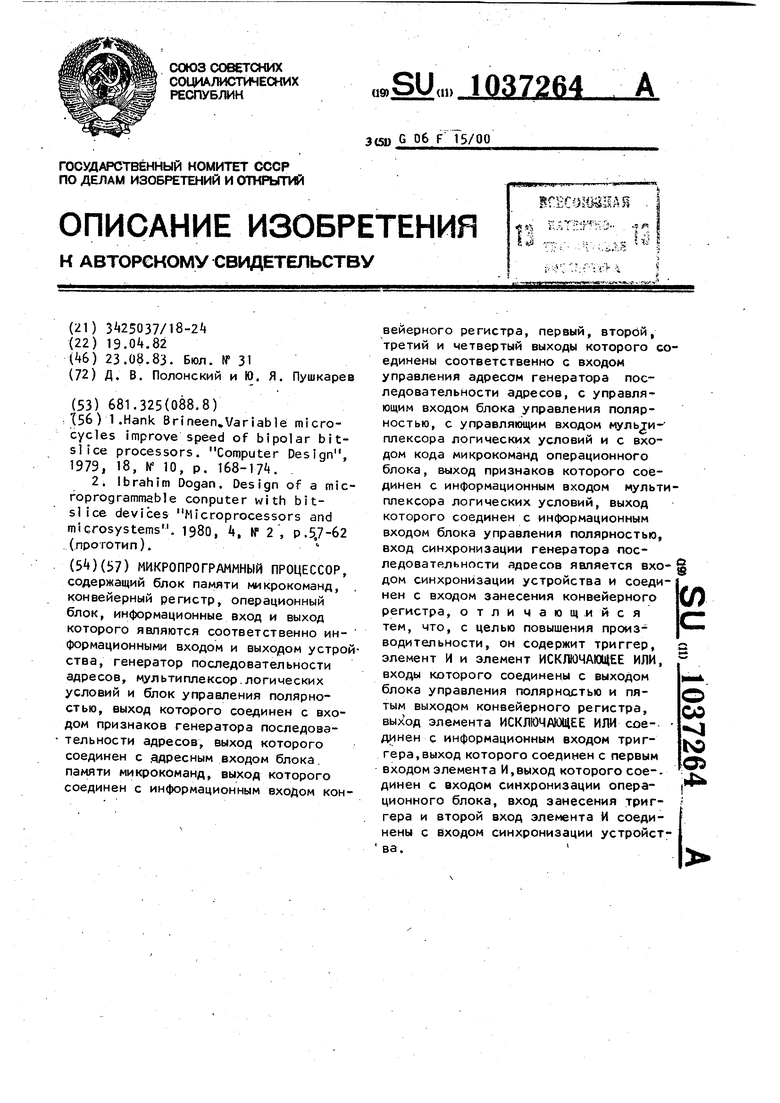

Изобретение относится к вычисли тельной технике и может быть исполь зовано для обработки данных в систе мах управления, Известен микропрограммный процес °Р содержащий блок памяти микроко манд, конвейерный регистр, генератор последовательности адресов, опе рационный блок и мультиплексор логических условий 1 1 Недостатком данного процессора яв ляется низкая производительность вследствие того, что при выполнении каждого условного перехода непроизво дительно расходуется микрокомандный цикл. Наиболее близким к изобретению по технической сущности является мик ропрограммный процессор, содержащий блок памяти микрокоманд, конвейерный ре гистр, операционный блок, генерато последовательности адресов, мультиплексор логических условий и блок управления полярностью 2 }. В известном микропрограммном процБссоре совмещены в одном микропро раммном цикле выполнение текущей мик рокоманды, хранимой на конвейерном регистре, с выборкой следующей микрокоманды из блока памяти микрокоманд. Однако при выполнении условных переходов следующая после условного перехода микрокоманда выбирается раньше, чем формируется логичес кое условие, определяющее направление перехода. Поэтому для каждого условного перехода в микропрограммные предусматривается холостая микрокоманда, выполняющая функцию задержки на один цикл. Наличие холостых циклов при выпо нении микропрограммы снижает производительность известного микропрограммного процессора. Кроме того, этот микропрограммный процессор имеет большой объем микропрограммной памяти за счет наличия в микропрограмме холостых микрокоманд. Целью изобретения является повышение производительности. Поставленная цель достигается тем, что микропрограммный процессор, содержащий блок памяти микрокоманд, конвейерный регистр, операционный блок, информационные вход и выход которого являются соответственно информационными входом и выходом уст ройства, генератор последовательности адресов, мультиплексор логических условий и блок управления полярностью, выход которого соединен с входом признаков генератора последовательности адресов, выход которого соединен с адресным входом блока памяти микрокоманд, выход которого соединен с информационным входом конвейерного регистра, первый, второй, третий и четвертый выходы которого со единены соответственно с входом управления адресом генератора последовательности адресов, с управляющим входом блока управления полярностью, с управляющим входом мультиплексора логических условий и с входом кода микрокоманд операционного блока, выход признаков которого соединен с информационным входом мультиплексора логических условии, выход которого соединен с информационным входом блока управления полярностью, вход синхронизации генератора последовательности адресов является входом синхронизации устройства и соединен с входом занесения конвейерного регистра, содержит триггер, элемент И и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, входы которого соединены с выходом блока управления полярностью и пятым выходом конвейерного регистра, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с информационным входом триггера,выход которого соединен с первым входом элемента И, выход которого соединен с входом синхронизации операционного блока, занесения триггера и второй вход элемента И соединены с входом синхронизации устройства . При таком решении значение условия предсказывается наперед. Если реальное значение условия совпадает с предполагаемым, то условный переход выполняется без холостого цикла. Если же реальное значение условий отличается от предполагаемого - при выполнении условного перехода присутствует холостой цикл. Сокращение холостых циклов при работе устройства повышает его производительность . Кроме того, при таком решении тпадает необходимость в использовании холостых микрокоманд, вследствие чего сокращается объм микропрограммной памяти устройства. На фиг. Т представлена схема пред лагаемого процессора; на фиг. 2 схема операционного блока; на фиг.Зсхема генератора последовательностей адресов; на .фиг. - схема мультиплексора логических условий; на фиг. 5- схема блока управления полярностью; на фиг. 6- алгоритмы микропрограммы; на фиг. 7 временная диаграмма работы устройства. Микропрограммный процессор содержит блок 1 памяти микрокоманд,конвейерный регистр 2, операционный бло 3, информационные вход k и выход 5 к торогО являются соответственно информационными входом и выходом устройства, генератор 6 последовательнос1;и адресов, мультиплексор 7 логических условий, блок 8 управления полярностью, триггер 9,элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 10, элемент И 11, а также входы 12 синхронизации и 13 на чальной установки устройства. Выход блока Т памяти микрокоманд соединен с информационным входом кон вейерного регистра 2, первый вход .которого соединен с входом Ц управления адресом генератора 6 последова тельности адресов. Второй выход конвейерного регист ра 2 соединен с управляющим входом 15 блока 8 управления полярностьто, выход которого соединен с входом.16 признаков генератора 6 последователь ности адресов и с входом элемента ИСКЛЮЧАЮЩЕЕ.ИЛИ 10. Третий выход конвейерного регистра 2 соединен с у равляющим входом 17 мультиплексора 7 логических условий, выход которого соединен с информационным входом 18 блока управления полярностью. Четвер тый выход конвейерного регистра 2 соединен с .входом 19 кода микрокоманд операционного блока 3,. выход, 20 признаков которого соединен с информационным входом 21 мультиплексора 7 логических условий. Пятый выход ко вейер.ного регистра 2 соединен с входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 10, выход которого соединен с информационным входом триггера 9. Выход генератора 6 последовательности адресов соедине;н с адресным входом блока 1 памяти микрокоманд. В ход триггера 9 соединен с.первым входом элемента И 11, второй вход ко торого соединен с входами занесения конвейерного регистра 2 и -,.irrepa 9 .с входом синхронизации генератора 6 последовательности адресов И с входом 12 синхронизации устройства. Выход элемента И 11 соединен с входом 22 синхронизации операционного блока 3. Установочные входы конвейерного регистра 2, генератора 6 последовательности адресов и триггера 9 соединены с входом 13 начальной установки устройства. Операционный блок 3 ((twr.2) содержит дешифратор 23 операций, сумматор 2, группы операционных элементов И 25, ИЛИ 26, и НЕ 27, группы коммутирующих элементов И 28, И 29, И 30, И 31, И 32, группу элементов ИЛИ 33, накапливающий регистр З и элемент И 35.. Вход дешифратора 23 операций и вход переноса сумматора 24 соединены с входом 19 кода микрокоманд операционного блока 3. Выходы дешифратора 23 операций соединены с входами групп коммутирующих элементов И 28, И 29, И 30, И 31, И 32, выходы которых -.соединены с-входами группы эпеч ментов ИЛИ 33, Выход группы элементов ИЛИ 33 соединен с информационным входом (накапливающего регистра 3 и с входом элемента И 35. Вход занесения накапливающего регистра 3 является входом 22 синхронизации операционного блока 3. Выход накапливающего регистра З является информационным выходом 5 устройства и соединен с первы входами сумматора 2, групп операционных элементов И 25, ИЛИ 26 и с входом группы операционных элементов НЕ 27. Вторые входы сумматора 2, групп операционных элементов .И 25, ИЛИ 26 и вход группы коммутирующих элементов И-31 соединены с информационным входом k устройства. Выходы сумматора 24,групп операционных элементов И 25, ИЛИ 26, НЕ 27 соединеныс входами коммутирующих элементов И 28, И 29, И 30, И 32 соответственно. Выход переноса сумматора 24, выход старшего разряда группы элементов ИЛИ 33 и выход элемента И 35 являются выходом 20 признаков операционно го блока 3.. Генератор 6 последовательности адресов (фиг.З) содержит регистр 36 адреса, сумматор 37, Дешифратор 38, группы элементов И 39, И 4о и ИЛИ 41, элементы И 42, И 43, ИЛИ 44, ИЛИ 45 и НЕ 46. Выход регистра 36 адреса сое 4нен с входом группы элементов И 39, выход которой соединен с входом группы элементов ИЛИ Ц , Выход группы элементов ИЛИ f1 является выходом генератора 6 последовательности адресов и соединен с первым входом сумматора 37, второй вход которого соединен с входом элемента НЕ +6 и общим проводом устройства. Выход зле иента НЕ А6 соединен с входом переноса сумматора 37, первый и второй выходы которого соединены соответственно с первым информационный входо регистра Зб адреса и входом элемента И ifZ. Вход дешифратора 38 и вход группы элементов И 0 являются входо k управления адресом генератора 6 последовательности адресов. Первый выход дешифратора 38 соединен с входами элементов И 3, ИЛИ f5 и с инверсным входом элемента И }2, выход которого соединен с входом элемента ИЛИ , Второй выход дешифратора ЗВ соединен с входом эле мента ИЛИ +5, выход которого соединен с входом группы элементов И 39. Третий выход дешифратора 38 соединен с входом группы элементов И kO, выход которой соединен с входом группы элементов ИЛИ 41, Вход элемента И 3 является входом 16 признаков генератора 6 последовательности адресов. Выход элемента И ЛЗ соединена аерез элемент ИЛИ k с вторым информационным входом регистра 36 адреса, входы занесения и адреса -которого являются, соответственно входом 12 синхронизации и входом 13 начальной установки устройства. . Мультиплексор 7 логических условий (фиг,4) содержит дешифратор 47, группу элементов И ЦЬ и элемент ИЛИА Вход дешифратора 7 является входом 17 мультиплексора 7 логических условий. Выходы дйцифратора 7соединены с первыми входами элементов И группы элементов И ЦВ, выходы которых через элемент соединены с выходом мультиплексора 7 логических условий,- Второй вход первого элемент И группы элементов И 8.соединен с о щим проводом устройства.Вторые входы остальных элементов И группы элементов И iS являются информационным входом 21 мультиплексора 7 логических . условий. ю б Блок 8 упра8Л€ ния полярностью (фиг,5) содержит элементы НЕ 50,И 5Ь И 52, и ИЛИ 53. Входы элементов НЕ 50 и И 5.1 соединены с информационным входом 16 блока 8 управления полярностью. Выход элемента НЕ 50 соедине н с входом эле| ента И 52, инверсный вход которого соединен с входом элемента И 51 и с управляющим входом 15 блока 8 управления полярностью. Выходы элементов И 51 и И 52 соединены с входами элемента ИЛИ 53, выход которого является выходом блока В управления полярч 91ОСТЬЮ. На фиг, 6 показан алгоритм микропрограммы, где символами М, L,N,, F. (,2,3,., . ,п...k... ) обозначены последовательности микрокоманд,а символом А - проверяемое логическое условие. На фиг, 7 показана временная диаграмма работы устройства, где; 5 сигнал начальной установки на вхоДе 13; 55- импульсы на входе 12 синхронизации; 56- коды микрокоманд на выходе блока 1 памяти микрокоманд; 57 - коды микрокоманд на выходе конвейерного регистра 2; 58- сигнал на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 1.0}59-сигнал условия на выходе 20 признаков генератора 6 последовательности адресов; 60- сигнал на выходе триггера 9; 61 - импульс на выходе элемента И 11. Для более четкого понимания работы устройства рассмотрим вьлполненкё им примера микропроГ(раммы,алгоритм которой показан на фиг.6. Работа устройства производится в соответствии с временной диаграммой (фиг.7). На вход 13 устройства подается сигнал 5, по которому конвейерный регистр 2, тртггер Э и регистр 36 адреса устанавливаются в нуль, По нулевому коду на входе Т генератора 6 последовательности адресов дешифратор 38 вырабатывает единичный сигнал на своем етрром выходе . Этим сигналом через элемент ИЛИ kS выбирается группа элементов И 39, в результате чего нулевой адрес с выхода регистра 36 адреса передается на выход генератора $ последовательности адресов, По нулевому адресу из блока 1 памяти микрокоманд выбирается первая микрокоманда Ml (позиция 56) и поступает на вход конвейерного регистра 2. Адрес микрокоманды М2 подготав ливается следующим образом. Так как на втором входе сумматора 37 постоянно присутствует уровень логического нуля (за счет Соединения с общим проводом устройства) , а на входе переноса сумматора 37 постоянно присутствует уровень логической единицы, то на выходах сумматора 37 формируется адрес на единицу больше адреса на его первом входе. С первого вихода сумматора 37 вход регистра 36 адреса поступает адрес следующей микрокоманды (М2) без старшего разряда. Старший разряд адреса микрокомандыМ2 поступает через элемент И 42, открытый нулевым сигналом с первого выхода дешифратора 38, и элемент ИЛИ 4 на вход регистра 36 адреса. При нулевом значении кода на упI равляющем входе , 17 мультиплексора 7 логических условий дешифратор 47 вырабатывает единичный сигнал на первом выходе. Этим сигналом выбира ется первый элемент И 48, в результ те чего нулевой сигнал с второго входа элемента И 48 (за счет соединения с общим проводом устройства ) поступает на выход мультиплексора 7 логических условий. Так как значени битов управления, поступающих с выходов конвейерного регистра 2 на вход 15 блока 8 управления полярно стью и вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 10, равны нулю, то сигнал 5В пр нимает единичное значение. При поступлении первого импульса 55 по его заднему фронту микрокоманда Ml заносится в конвейерный регистр 2 (позиция 57), адрес микро команды М2 заносится в регистр Зб адреса, а в триггер 9 заносится единица. С первого выхода конвейерного регистра 2 на вход 14 управления адресом генерэтора 6 последовательности адресов поступает адресна часть микрокоманды Ml. Адресная час каждой микрокоманды состоит из двух полей - адресного и управляющего.В адресном поле указывается адрес перехода при безусловной передаче упр ления, в управляющем - тип перехода. Значение кода в управляющем поле адресной части микрокоманды Ml равно нулю, в результате чего, едини чным сигналом со второго выхода 1 48 дешифратора ЗЗ вы&1рается группа элементов И 39 и адрес микрокоманды М2 поступает на выход генератора 6 . последовательности адресов. По адресу микрокоманды Н2 (аналогично описанному ) на выходе сумматора 37 формируется адрес макрокоманды МЗ, а из блока 1 памяти микрокоманд через время f, определяемое временем выборки из памяти, считывается микрокоманда М2 (позиция 56) и поступает на вход конвейерного регистра 2. Значения управляющих полей микрокоманды Ml, поступающих на вход 15 блока 8 управления полярностью, на вход 17 мультиплексора 7 логических условий и на вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 10, также равны нулю, в результате чего сигнал 58 сохраняет единичное значение. Одновременно с выборкой микрокоманды М2 из блока 1 памяти микрокоманд, , операционный блок 3 выполня;ет операцию, задаваемую в операционной части микрокоманды Ml. Операционная часть микрокоманды поступает, с четвертого выхода конвейерного регистра 2 на вход Т9 кода микрокома(д операционного блока 3. Операционный блок 3 оперирует с двумя операндами, один из которых находится в накапливающем регистре 34, а другой поступает на информационный вход 4 устройства. На выходе сумматора 24 формируется значение арифметической суммы слагаемых с учетом сигнала входного переноса, значение которого задается в поле микрокоманды. На выходах групп операционных элементов И 25 и ИЛИ 26 формируется значение кон-ьюнкции и /: зъюнкции операндов. На выходе группы операционных -элементов НЕ 27 формируется инверсия содержимого в накапливающем регистре 34.Дешифратор 23 декодирует-код операции на входе 19 операционого блока 3 и вырабатывает на одном из своих выходов единичный сигнал. Этим сигналом открывается одна из групп коммутирующих элементов И 28, И 29, И 30, И 31, И 32, и результат соответствующей операции поступает на информационный вход накапливающего регистра 34 . Если результат операции par вен нулю, то на выходе элеменуа Л 35 вырабатывается единичный сигнал. Сигналы с выхода элемента И 35, с выхода переноса сумматора 24 и с вы-. хода старшего разряда (знак результата) группы элементов ИЛИ 33 поступают на выход 20 признаков операционного блока 3. При поступлении второго импульса 55 микрокомгнда М2 заносится в конвейерный регистр 2, а на выходе эле мента И 11, открытого единичным си|- налом 60, вырабатывается импульс 61 По импульсу 61 результат операции заносится в накапливающий регистр 3 Далее работа устройства- при выпо нении всех микрокоманд последовательности М- аналогична описанной вплоть до занесения микрокоманды М в конвейерный регистр 2 (nosvinHH 57 В адресном поле- адресной части микрокоманды М„ задается адрес микро ;ома1-;дь , а в управляющем поле - код безусловного перехода. Единичным сигналом с третьего вы хода дешифратора 38 открывается гру па элементов И 40, в.результате чего адрес микрокоманды L поступает на выход генератора 6 последовательности адресов. По адресу микрокоманды L,j на аыходе сумматора37 формируется адрес микрокоманды L-, а из блока 1 памяти микрокоманд выбирает ся икрокоманда L .(позиция 5б), Выполнение последовательности L .noi i--iHO выполнению последователь - нести Н вплоть до занесения микро команды Lvj в конвейерный регистр 2 4Ы L. Л и I .ия 7). (позиция 57). При этом в регистр Зб адреса заносится адрес микрокоманды N j сформированный на выходе сумматора 37 по адресу микрокоманfib Ч-V 8 управляющем поле адресной-части микрокоманды L задается код условного перехода, в результате чего единичный сигнал вырабатывается на первом выходе дешифратора 3S. По этому сигналу элемент И 2 закрывается, а элемент И 3 открыва ется. Адрес микрокоманды N поступа ет на выход генератора 6 последовательности адресов, в результате чего микрокоманда N выбирается из блока 1 памяти микрокоманд. Адрес следующей микрокоманды (N2 или F ) формируется в зависимости от значения сигнала на входе 16 .признаков генератора 6 последовательности адресов. Сигнал на входе 16 признаков генератора 6 последовательности адре сов формируется следующим образом В результате выполнения микрокоманfды L формируется сигнал 59.По номеру условия, поступающего на вход 17 мультиплексора 7 логических условий, последний подключает на свой выход сигнал условия с входа 21. Битом управления, поступающим на вход 15 блока 8 управления полярностью .задается требуемое значение (прямое или инверсное) сигнала условия. С выхода блока 8 управления полярностью сигнал условия поступает на вход 16 признаков генератора 6 последовательности адресов и на вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 10. При этом значение бита управления, посту пакхцего с выхода конвейерного регистра 2 на вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 10, указывает на предполагаемое значение сигнала условия (если условие предсказывается равным единице,- то бит управления равен нулю, если же условие предсказывается равным нулю, то бит управления равен- единице). При соответствии реального .значения сигнала условия ожидаемому сигнал 58 равен единице, а в случае , когда такого соответствия нет ( как показано на временной диаграмме) , - сигнал 58 принимает нулевое значение. По непредполагаемому значению условия на входе регистра 36 формируется адрес микрокоманды F . При поступлении очередного импульса 55 в конвейерный регистр 2 заносится микрокоманда N , в регистр 36 адреса заносится адрес микрокоманды р , а в триггер 9 заносится нуль. Сигналом 60 закрывается элемент И 11. По импульсу 61 результат . операции микрокоманды 1 заносится в накапливающий регистр 3. При поступлении следующего импульса 55 в конвейерный регистр 2 заносится микрокомандаГ , в регистр 36 адреса заносится адрес микрокомандыР , а в триггер 9 - единица. Импульс 61 в этом случае не вырабатывается, чем предупреждается неправомерное выполнение микрокоманды N. В этом случае при проведении условного перехода -присутствует холостой цикл в выполнении микропрограммы. Если бы реальное значение условия соответствовало ожидаемому, сиг-: нал, 58 не изменил бы единичного значения, на входе регистра Зб адреса сформировался бы адрес микрокоманды 11 . 10 Nj. В этом случае после выполнения микрокоманды L без пропуска цикла выполнялись бы ( 1крокоманды N ,N,, и т.д. Таким образом, в предлагаемом микропрограммном процессоре потеря производительности за счет холостых циклов при проведении условных переходов происходит только в случаях непредполагаемого значения условия, в отличие от известного, где холостой цикл присутствует при выполнении каждого условного перехода. Исключение из к кропрограммы холостых команд позволяет сократить объем микропрограммной памяти. В качестве базового объекта принят микропрограммный процессор, встроенный в сопроцессор обработки каналов связи для ЭВМ СМ-. В предлагаемом микропрограммном процессоре потери производитель.ности холостых циклов при выполнении условных переходов происходят только в случае перехода по не предполагаемому значению условия, в оч личие от базового объекта, где хо лостой цикл присутствует при выполнении каждого условного перехода. Даже при равной вероятности обоих на равлении перехода в среднем предлагаемый микропрограммный процессор дает выигрыш в.50% случае выполнения переходов в микропрограмме. Однако в большинстве случае вероятности переходов не одинаковы и их несложно .-определить .Например, при необходимос.ти повторения циклической программы Rpa3, значение вероятности возврат в цикл в R раз выше, чем значение ве роятности выхода из цикла. В реальны микропрограммных процессорах экономия времени будет присутствовать в среднем при выполнении условных переходов. В связи с этим в пред лагаемом устройстве потери производительности будут как минимум в 2 раза ниже, чём э базовом объекте. Для качественной оценки эффективности предлагаемого микропрограммно го процессора проанализируем время выполнения микропрограмм, ицеющих различную кон(1 1гурацию. Любую микропрограмму можно представить в виде дерева, имеющего линейные участки и узловые точки, в которых осуществляются условные переходы в микропрограмме. Например, необходимо выполнить циклический участок микропрограммы, содержащей линейный участок и узловую точкуу из которой осуществляется возврат в цикл или выход из него. Пусть линейный участок микропрограммы 1у состоит из К микрокоманд, Т - длительность цикла микрокоманды, а необходимость повторения данного участка микропрограммы равна R . Тогда вероятности возврата в цикл (р) и выхода из неге {1-Р) распределятся следующим образом: Время выполнения микропрограммы Т без использования предлагаемого устройства определяются из выраженияТ Kt+t (К+1 )Г, . так как при выполнении перехода необходимо каждый раз выполнить холостой цикл. При выполнении цикла R раз получим : Т (К+1 )Rr. При использовании предлагаемого устройства имеем: Т KR-u Величина т - т показывает относительное сокращение времени выполнения микропрограммы.Из выражения видно, что при небольших . линейных участках в цикле (К.$20 ) мы получим существенное сокращение времени выполнения микропрограммы.

Фт1

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1983 |

|

SU1124299A1 |

| Микропрограммный процессор | 1987 |

|

SU1517034A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1108448A1 |

| Микропроцессор | 1984 |

|

SU1179363A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1100624A1 |

| Микропроцессор | 1984 |

|

SU1164721A1 |

| Микропрограммное устройство управления с контролем | 1985 |

|

SU1277105A1 |

| Микропрограммный процессор | 1985 |

|

SU1275457A1 |

| Устройство управления контролем | 1985 |

|

SU1285471A1 |

| Микропроцессор | 1982 |

|

SU1037263A1 |

МИКРОПРОГРАММНЫЙ ПРОЦЕССОР, содержащий блок памяти микрокоманд, конвейерный регистр, операционный блок, информационные вход и выход которого являются соответственно информационными входом и выходом устройства, генератор последовательности адресов, мультиплексор.логических условий и блок управления полярностью, выход которого соединен с входом признаков генератора последовательности адресов, выход которого соединен с .адресным входом блока. памяти микрокоманд, выход которого соединен с информационным входом конвейерного регистра, первый, второй, третий и четвертый выходы которого соединены соответственно с входом управления адресом генератора последовательности адресов, с управляющим входом блока управления полярностью, с управляющим входом мультиплексора логических условий и с входом кода микрокоманд операционного блока, выход признаков которого соединен с информационным входом мультиплексора логических условий, выход которого соединен с информационным входом блока управления полярностью, вход синхронизации генератора последовательности адоесов является входом синхронизации устройства и соеди(Л С нен с входом занесения конвейерного регистра, отли чающийся тем, что, с целью повышения производительности, он содержит триггер, элемент И и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, входы которого соединены с выходом блока управления полярностью и пятым выходом конвейерного регистра, 00 выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ сое-. ьо динен с информационным входом триггера, выход которого соединен с первым Од входом элемента И,выход которого сое-, :4 динен с входом синхронизации операционного блока, вход занесения триггера и второй вход элемента И соединены с входом синхронизации устройства.

фиг. 2 f-

.ff

/4

jy

ss ff

ЛГ ff9

SO 6/

Авторы

Даты

1983-08-23—Публикация

1982-04-19—Подача