Изобретение относится к автоматике и вычислительной технике, в частности к микропрограммным устройствам управления повышенной надежности, и может быть использовано в цифровых вычислительных системах, а также в терминальной аппаратуре.

Цель изобретения - повьппение надежности устройства за счет восстановления работы при сбое.

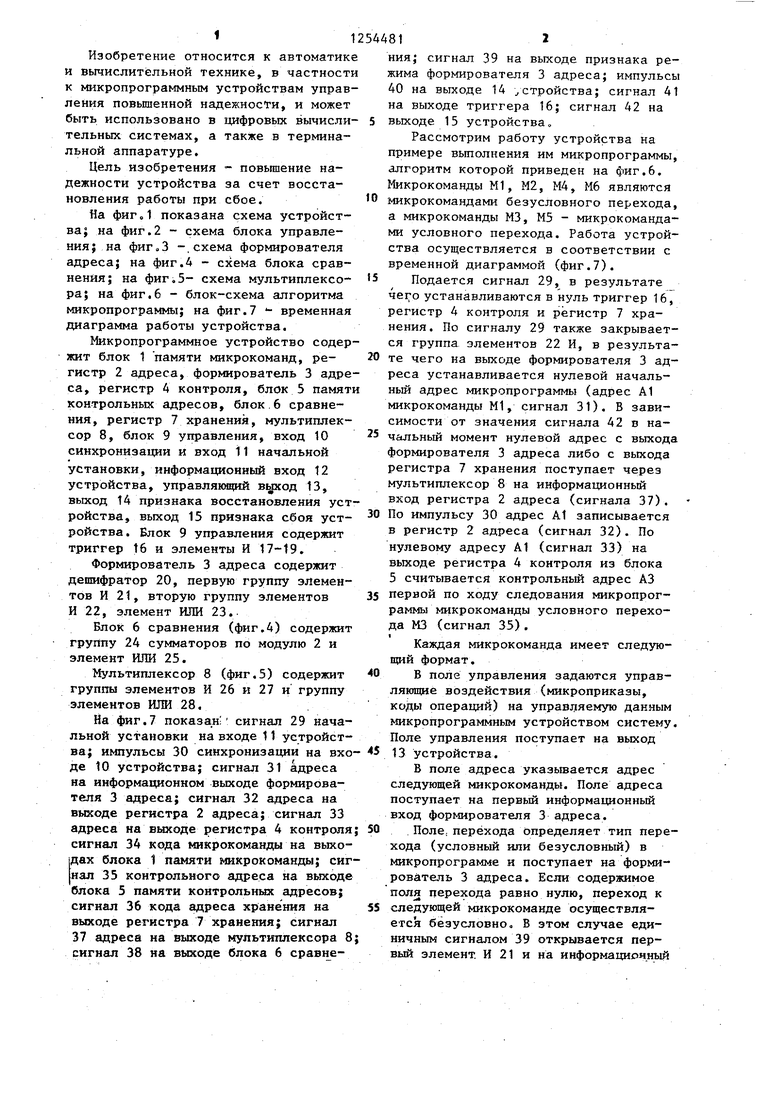

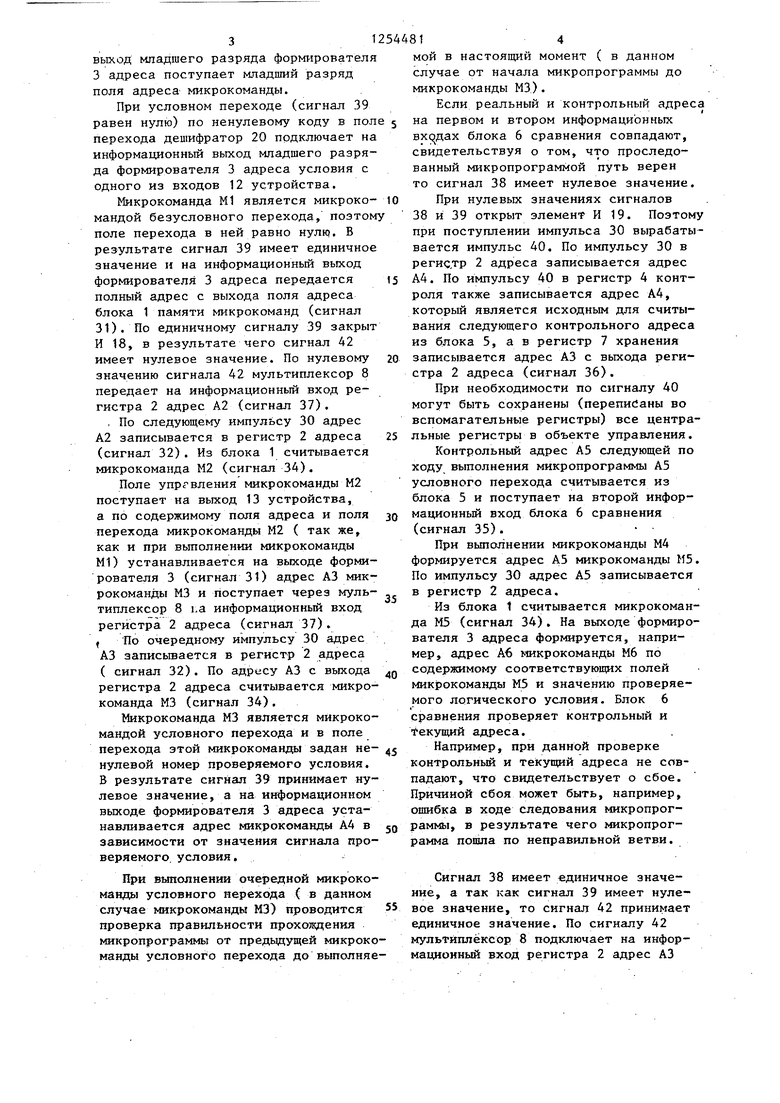

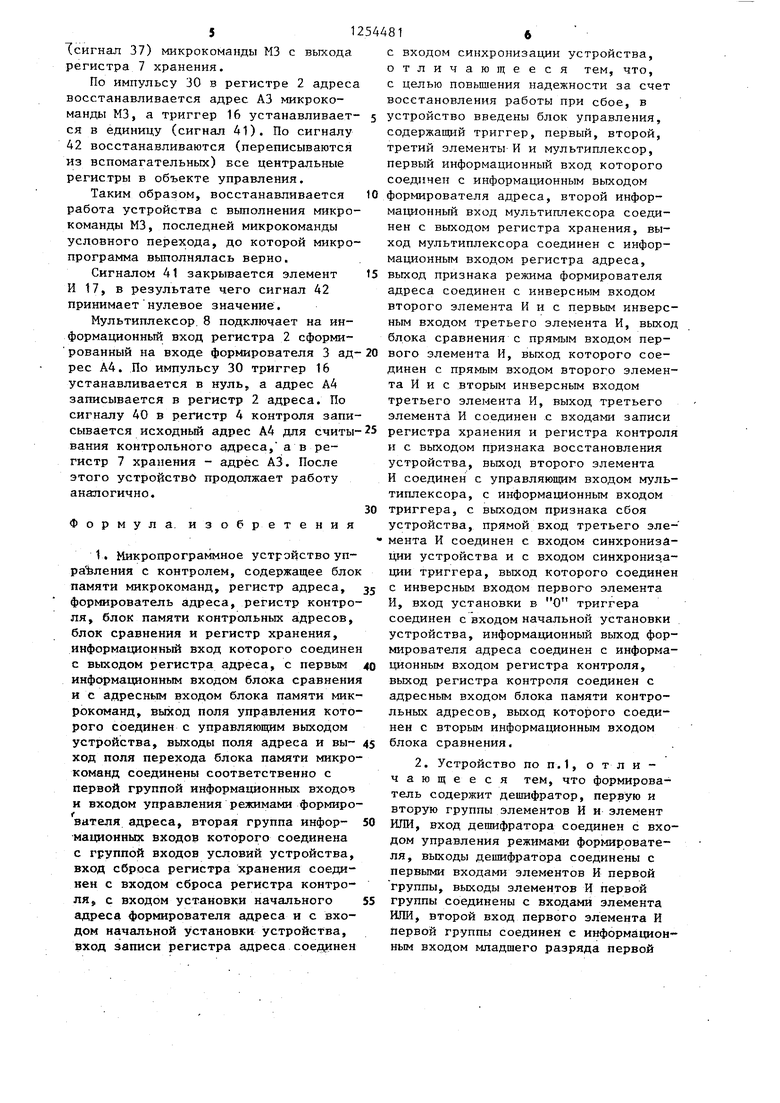

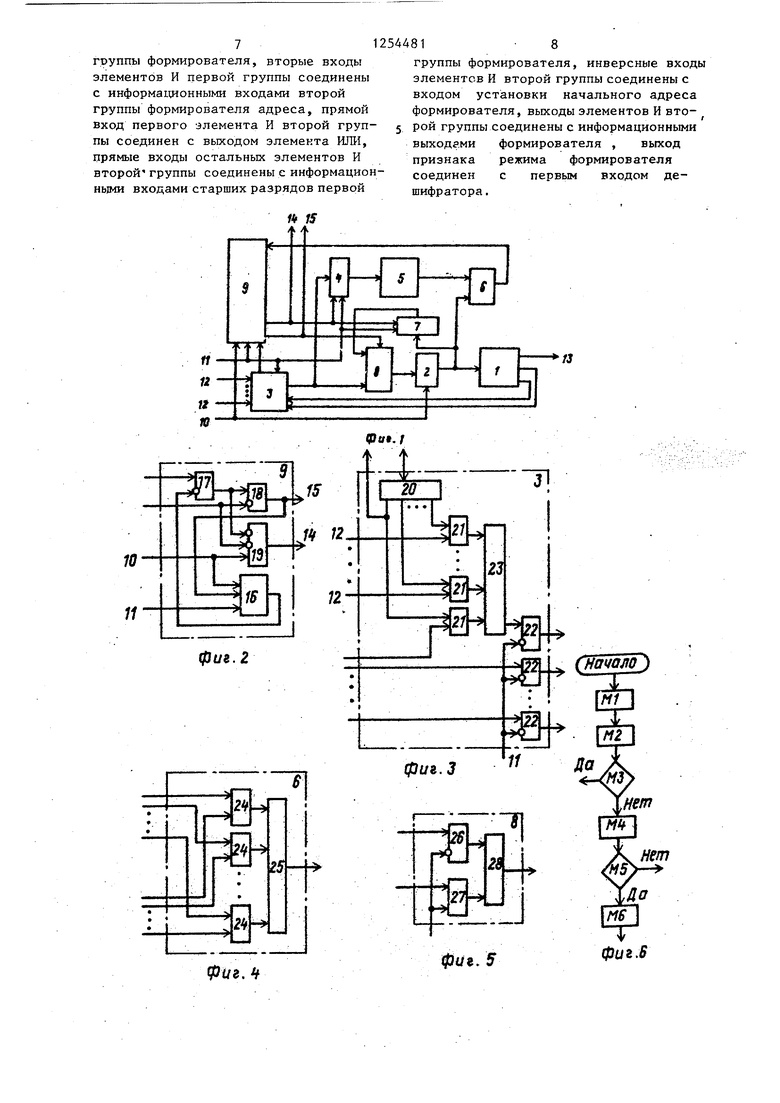

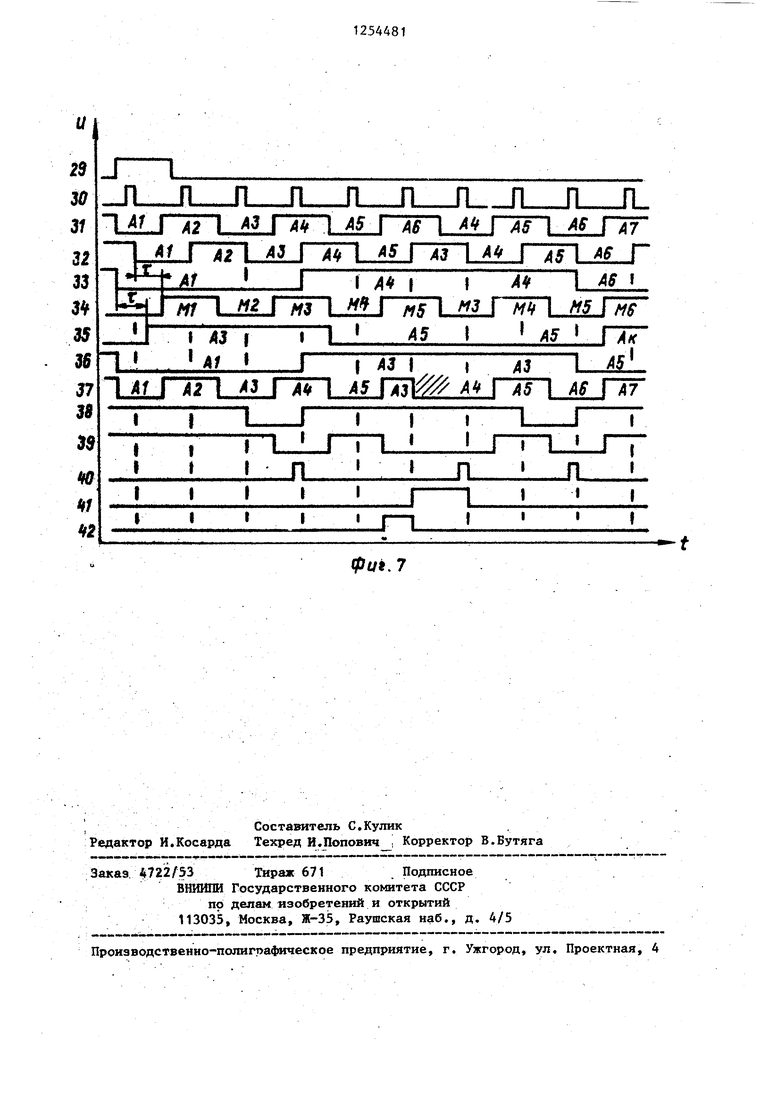

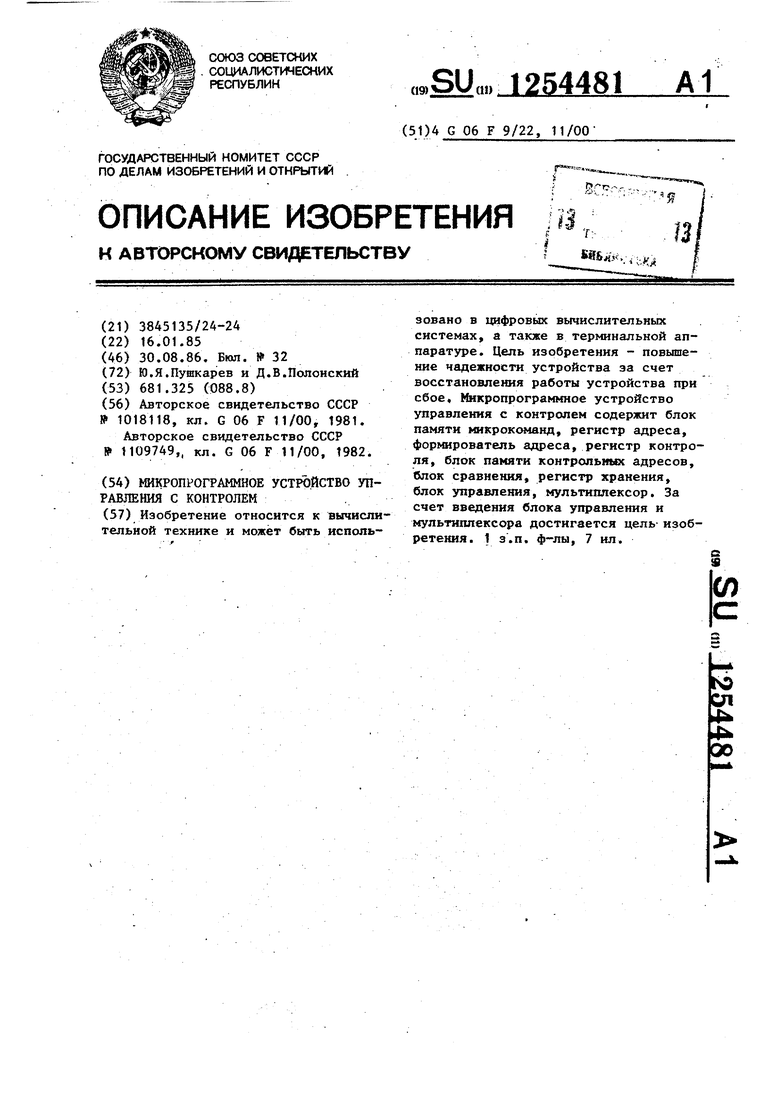

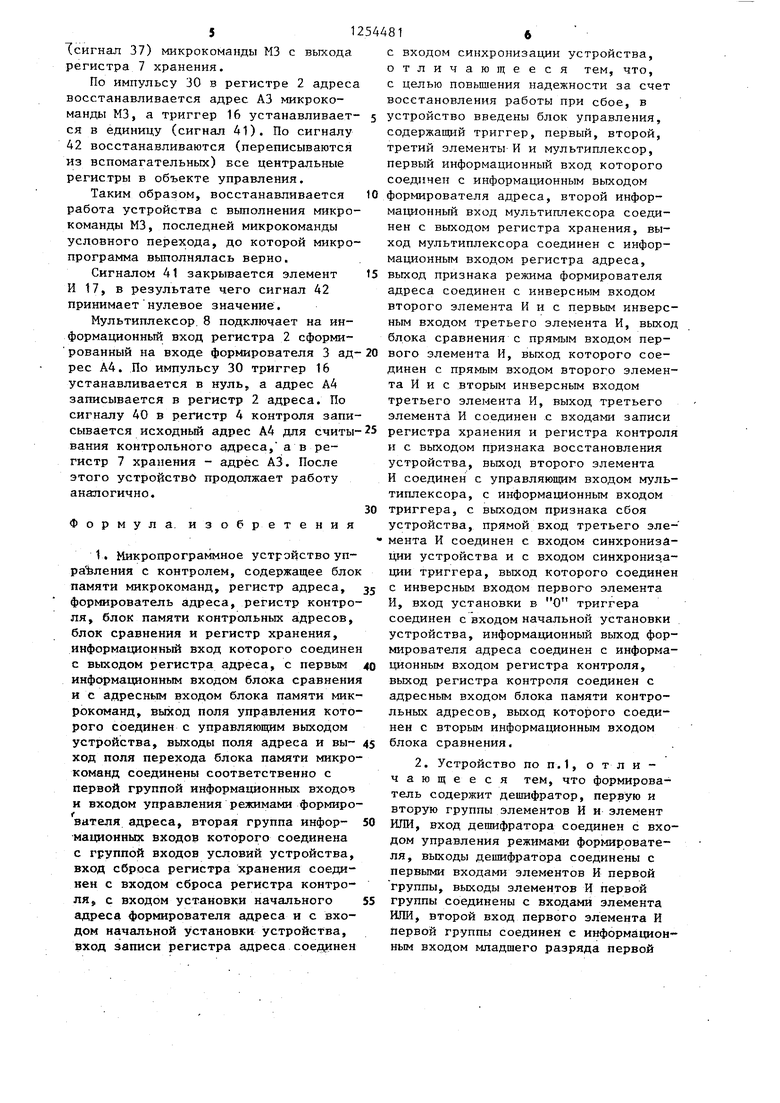

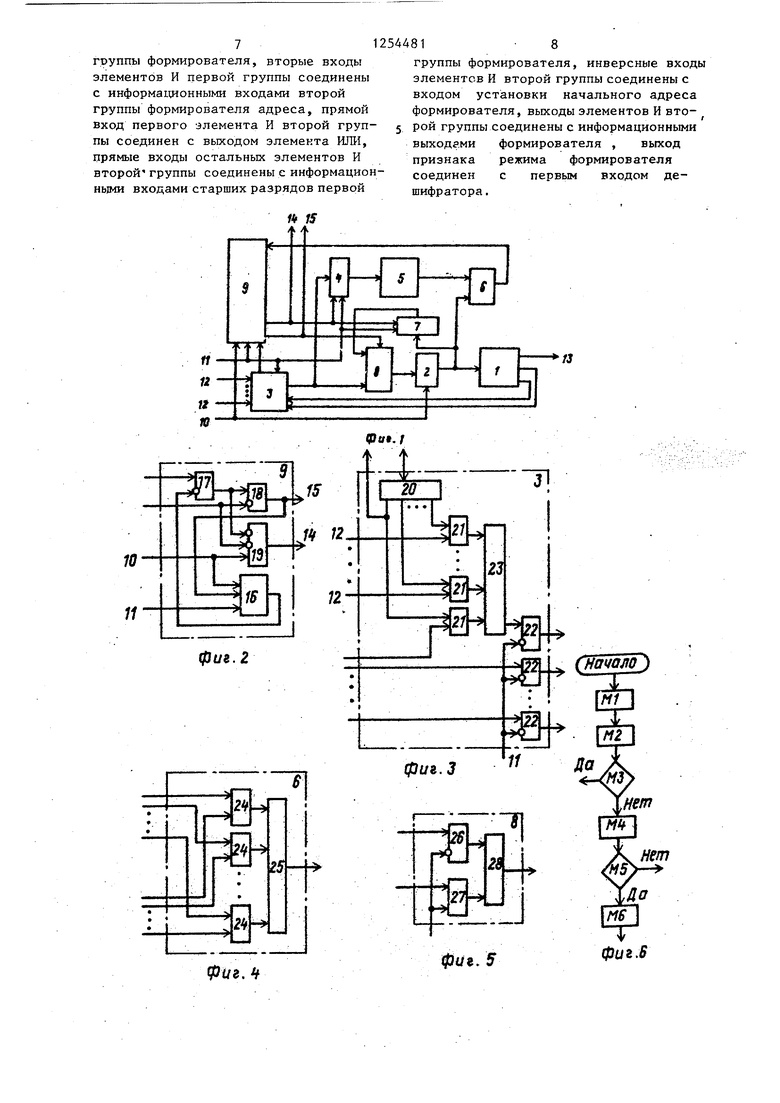

На фиг„1 показана схема устройства; на фиг.2 - схема блока управления; на фиг.З -.схема формирователя адреса; на фиг.4 - схема блока сравнения; на фиг.5- схема мультиплексора; на фиг.б - блок-схема алгоритма микропрограммы; на фиг.7 - временная диаграмма работы устройства.

Микропрограммное устройство содержит блок 1 памяти микрокоманд, регистр 2 адреса, формирователь 3 адреса, регистр 4 контроля, блок 5 памят контрольных адресов, блок 6 сравнения, регистр 7 хранения, мультиплексор 8, блок 9 управления, вход 10 синхронизации и вход 11 начальной установки, информационный вход 12 устройства, управляющий выход 13, выход 14 признака восстановления устройства, выход 15 признака сбоя устройства. Блок 9 управления содержит триггер 16 и элементы И 17-19.

Формирователь 3 адреса содержит дешифратор 20, первую группу элементов И 21, вторую группу элементов И 22, элемент ИЛИ 23..

Блок 6 сравнения (фиг.4) содержит группу 24 сумматоров по модулю 2 и элемент ИЛИ 25.

Мультиплексор 8 (фиг.5) содержит группы элементов И 26 и 27 и группу элементов ИЛИ 28.

На фиг.7 показан; сигнал 29 начальной установки на входе 11 устройства; импульсы 30 синхронизации на вхо де 10 устройства; сигнал 31 адреса на информационном выходе формирователя 3 адреса; сигнал 32 адреса на выходе регистра 2 адреса; сигнал 33 адреса на выходе регистра 4 контроля сигнал 34 кода микрокоманды на выхо дах блока 1 памяти микрокоманды; сигнал 35 контрольного адреса на выходе блока 5 памяти контрольных адресов; сигнал 36 кода адреса хране ния на выходе регистра 7 хранения; сигнал 37 адреса на выходе мультиплексора 8 сигнал 38 на выходе блока 6 сравне

S

0

5

5

ния; сигнал 39 на выходе признака режима формирователя 3 адреса; импульсы 40 на выходе 14 стройства; сигнал 41 на выходе триггера 16; сигнал 42 на выходе 15 устройства

Рассмотрим работу устройства на примере выполнения им микропрограммы, алгоритм которой приведен на фиг.6. Микрокоманды М1, М2, М4, Мб являются микрокомандами безусловного перехода, а микрокоманды МЗ, М5 - микрокомандами условного перехода. Работа устройства осуществляется в соответствии с временной диаграммой (фиг.7).

Подается сигнал 29, в результате 4ei;o устанавливаются в нуль триггер 16, регистр 4 контроля и регистр 7 хранения. По сигналу 29 также закрывается группа элементов 22 И, в результате чего на выходе формирователя 3 адреса устанавливается нулевой начальный адрес микропрограммы (адрес А1 микрокоманды Ml, сигнал 31). В зависимости от значения сигнала 42 в начальный момент нулевой адрес с выхода формирователя 3 адреса либо с выхода регистра 7 хранения поступает через мультиплексор 8 на информационный вход регистра 2 адреса (сигнала 37). По импульсу 30 адрес А1 записывается в регистр 2 адреса (сигнал 32). По нулевому адресу А1 (сигнал 33) на Выходе регистра 4 контроля из блока 5 считывается контрольный адрес A3 первой по ходу следования микропрограммы микрокоманды условного перехода МЗ (сигнал 35).

Каждая микрокоманда имеет следующий формат.

В поле управления задаются управляющие воздействия (микроприказы, коды операций) на управляемую данным микропрограммным устройством систему. Поле управления поступает на выход 13 устройства.

В поле адреса указывается адрес следующей микрокоманды. Поле адреса поступает на первый информационный вход формирователя 3 адреса.

Поле, перехода определяет тип перехода (условный или безусловный) в микропрограмме и поступает на формирователь 3 адреса. Если содержимое поля перехода равно нулю, переход к 5 следующей микрокоманде осуществляется безусловно. В этом случае единичным сигналом 39 открывается первый элемент. И 21 и на информационный

0

5

0

0

выход младшего разряда формирователя 3 адреса поступает младший разряд поля адреса микрокоманды.

При условном переходе (сигнал 39 равен нулю) по ненулевому коду в пол перехода дешифратор 20 подключает на информационный выход младшего разряда формирователя 3 адреса условия с одного из входов 12 устройства.

Микрокоманда Ml является микроко- мандой безусловного перехода, поэтом поле перехода в ней равно нулю. В результате сигнал 39 имеет единичное значение и на информационный выход формирователя 3 адреса передается полный адрес с выхода поля адреса блока 1 памяти микрокоманд (сигнал 31). По единичному сигналу 39 закрыт И 18, в результате чего сигнал 42 имеет нулевое значение. По нулевому значению сигнала 42 мультиплексор 8 передает на информационный вход регистра 2 адрес А2 (сигнал 37),

. По следующему импульсу 30 адрес А2 записывается в регистр 2 адреса (сигнал 32). Из блока 1 считывается микрокоманда М2 (сигнал 34).

Поле управления микрокоманды М2 поступает на выход 13 устройства, а по содержимому поля адреса и поля перехода микрокоманды М2 ( так же, как и при вьшолнении микрокоманды Ml) устанавливается на выходе формирователя 3 (сигнал 31) адрес A3 микрокоманды МЗ и поступает через муль- типлексор 8 i.a информационный вход регистра 2 адреса (сигнал 37). f По очередному импульсу 30 адрес A3 записьшается в регистр 2 адреса ( сигнал 32). По адресу A3 с выхода регистра 2 адреса считывается микрокоманда МЗ (сигнал 34).

Микрокоманда МЗ является микрокомандой условного перехода и в поле перехода зтой микрокоманда задан не- нулевой номер проверяемого условия. В результате сигнал 39 принимает нулевое значение, а на информационном выходе формирователя 3 адреса устанавливается адрес микрокоманды А4 в зависимости от значения сигнала проверяемого, условия.

При выполнении очередной микрокоманды условного перехода ( в данном случае микрокоманды МЗ) проводится проверка правильности прохождения микропрограммы от предыдущей микрокоманды условного перехода до выполняемой в настоящий момент ( в данном случае от начала микропрограммы до микрокоманды МЗ).

Если реальный и контрольный адре на первом и втором информационных блока 6 сравнения совпадают, свидетельствуя о том, что проследо- ванный микропрограммой путь верен то сигнал 38 имеет нулевое значение

При нулевых значениях сигналов 38 и 39 открыт элемент И 19. Поэтом при поступлении импульса 30 вырабатывается импульс 40. По импульсу 30 в регис.тр 2 адреса записывается адрес А4. По импульсу 40 в регистр 4 контроля также записывается адрес А4, который является исходным для считывания следующего контрольного адреса из блока 5, а в регистр 7 хранения записывается адрес A3 с выхода регистра 2 адреса (сигнал 36).

При необходимости по сигналу 40 могут быть сохранены (переписаны во вспомагательные регистры) все центральные регистры в объекте управления.

Контрольный адрес А5 следующей по ходу выполнения микропрограммы А5 условного перехода считывается из блока 5 и поступает на второй информационный вход блока 6 сравнения (сигнал 35).

При выполнении микрокоманды М4 формируется адрес А5 микрокоманды М5 По импульсу 30 адрес А5 записывается в регистр 2 адреса.

Из блока t считывается микрокоманда М5 (сигнал 34). На выходе формирователя 3 адреса формируется, например, адрес А6 микрокоманды Мб по содержимому соответствующих полей мик рокоманды М5 и значению проверяемого логического условия. Блок 6 сравнения проверяет контрольный и текущий адреса.

Например, при данной проверке контрольный и текущий адреса не совпадают, что свидетельствует о сбое. Причиной сбоя может быть, например, ощибка в ходе следования микропрограммы, в результате чего микропрограмма попша по неправильной ветви.

Сигнал 38 имеет единичное значение, а так как сигнал 39 имеет нулевое значение, то сигнал 42 принимает единичное значение. По сигналу 42 мультиплексор 8 подключает на информационный вход регистра 2 адрес A3

51

Тсигнал 37) микрокоманды МЗ с выхода регистра 7 хранения.

По импульсу 30 в регистре 2 адрес восстанавливается адрес A3 микрокоманды МЗ, а триггер 16 устанавливается в единицу (сигнал 41). По сигналу 42 восстанавливаются (переписываются из вспомагательньк) все центральные регистры в объекте управления.

Таким образом, восстанавливается работа устройства с вьшолнения микрокоманды МЗ, последней микрокоманды условного перехода, до которой микропрограмма вьтолнялась верно.

Сигналом 41 закрывается элемент И 17, в результате чего сигнал 42 принимает нулевое значение.

Мультиплексор. 8 подключает на информационный вход регистра 2 сформи

рованный на входе формирователя 3 ад-20 вого элемента И, выход которого соерее А4. По импульсу 30 триггер 16 устанавливается в нуль, а адрес А4 записывается в регистр 2 адреса. По сигналу 40 в регистр 4 контроля записывается исходньй адрес А4 для считы-25 регистра хранения и регистра контроля вания контрольного адреса, а в регистр 7 хранения - адрес A3. После этого устройство продолжает работу аналогично.

Формула, изобретения

30

и с выходом признака восстановления устройства, выход второго элемента И соединен с управляющим входом мультиплексора, с информационным входом триггера, с выходом признака сбоя устройства, прямой вход третьего эле- мента И соединен с входом синхронизации устройства и с входом синхронизации триггера, вькод которого соединен с инверсным входом первого элемента И, вход установки в О триггера соединен с входом начальной установки устройства, информационный выход формирователя адреса соединен с информационным входом регистра контроля, выход регистра контроля соединен с адресным входом блока памяти контрольных адресов, выход которого соединен с вторым информационным входом блока сравнения.

1. Микропрограммное устройство уп- раЪления с контролем, содержащее блок памяти микрокоманд, регистр адреса, 35 формирователь адреса, регистр контроля, блок памяти контрольных адресов, блок сравнения и регистр хранения, информационный вход которого соединен с выходом регистра адреса, с первьм 40 информационным входом блока сравнения и с адресньш входом блока памяти микрокоманд, выход поля управления которого соединен с управляющим выходом устройства, выходы поля адреса и вы- 45 ход поля перехода блока памяти микрокоманд соединены соответственно с первой группой информационных входов и входом управления режимами формирователя адреса, вторая группа инфор- 50 мационных входов которого соединена с группой входов условий устройства, вход сброса регистра хранения соединен с входом сброса регистра контроля, с входом установки начального 55 адреса формирователя адреса и с входом начальной установки устройства, вход записи регистра адреса соединен

с входом синхронизации устройства, отличающееся тем, что, с целью повышения надежности за счет восстановления работы при сбое, в

устройство введены блок управления, содержащий триггер, первый, второй, третий элементы И и мультиплексор, первый информационный вход которого соединен с информационным выходом формирователя адреса, второй информационный вход мультиплексора соединен с выходом регистра хранения, выход мультиплексора соединен с информационным входом регистра адреса,

выход признака режима формирователя адреса соединен с инверсным входом второго элемента И и с первым инверсным входом третьего элемента И, выход блока сравнения с прямым входом пер

динен с прямым входом второго элемента И и с вторым инверсным входом третьего элемента И, выход третьего элемента И соединен с входами записи

регистра хранения и регистра контроля

и с выходом признака восстановления устройства, выход второго элемента И соединен с управляющим входом мультиплексора, с информационным входом триггера, с выходом признака сбоя устройства, прямой вход третьего эле- мента И соединен с входом синхронизации устройства и с входом синхронизации триггера, вькод которого соединен с инверсным входом первого элемента И, вход установки в О триггера соединен с входом начальной установки устройства, информационный выход формирователя адреса соединен с информационным входом регистра контроля, выход регистра контроля соединен с адресным входом блока памяти контрольных адресов, выход которого соединен с вторым информационным входом блока сравнения.

2. Устройство по п.1, отличающееся тем, что формирователь содержит дешифратор, первую и вторук группы элементов И и элемент ИЛИ, вход дещифратора соединен с входом управления режимами формирователя, выходы дешифратора соединены с первыми входами элементов И первой группы, выходы элементов И первой группы соединены с входами элемента ИЛИ, второй вход первого элемента И первой группы соединен с информационным входом младшего разряда первой

71254481 8

группы формирователя, вторые входы группы формирователя, инверсные входы элементов И первой группы соединены элементов И второй группы соединены с с информагшонными входами второй входом установки начального адреса группы формирователя адреса, прямой формирователя, выходы элементов И втовход первого элемента И второй груп-5 РОЙ группы соединены с информационными пы соединен с выходом элемента ИЛИ, выходами формирователя , выход прямые входы остальных элементов И признака режима формирователя второй группы соединены с информацион- соединен с первым входом де- ными входами старших разрядов первой шифратора.

фиг. ч

а

нет

фиг. 5

Составитель С,Кулик Редактор И.Косарда Техред И.Попович , Корректор В.Бутяга

Заказ NB 722/53 Тираж 671 . Подписное ВМИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полигпафическое предприятие, г. Ужгород, ул. Проектная, 4

Фи9.7

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропроцессор | 1984 |

|

SU1179363A1 |

| Микропроцессор | 1984 |

|

SU1257657A1 |

| Микропроцессор | 1984 |

|

SU1164721A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1130865A1 |

| Устройство для сопряжения электронно-вычислительной машины с группой внешних устройств | 1989 |

|

SU1734098A1 |

| Многоканальное устройство для сопряжения ЭВМ | 1988 |

|

SU1695311A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1136162A1 |

| Микропрограммное устройство для управления каналами ЭВМ | 1982 |

|

SU1068938A1 |

| Устройство для управления памятью | 1984 |

|

SU1236489A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных системах, а также в терминальной аппаратуре. Цель изобретения - повышение чадежиости устройства за счет восстановления работы устройства при сбое. Микропрограммное устройство управления с контролем содержит блок памяти микрокоманд, регистр гщреса, формирователь адреса, регистр контроля, блок памяти контрольтк адресов, блок сравнения, регистр хранения, блок управления, мультиплексор. За счет введения блока управления и мультиплексора достигается цель- изобретения. 1 з.п. ф-лы, 7 ил. сд 4;; 4: 00

| Микропрограммное устройство управления с контролем переходов | 1981 |

|

SU1018118A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Микропрограммное устройство управления с контролем переходов | 1982 |

|

SU1109749A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-08-30—Публикация

1985-01-16—Подача