НЕ, пятому выходу депшфратора микроопераций и входу признака прерывания устройства, первый, второй и третий входы и выход второго элемента И соединены соответственно с информационным входом устройства, пятым выходом дешифратора микроопераций, входом признака прерьгеания устройства и входом второго элемента НЕ, первый и второй входы и выход третьего элемента И подключены соответственно к входу признака прерывания устройства, пятому выходу дешифратора микроопераций и первому входу второго элемента ИЛИ, второй вход

6071

и выход которого соединены соответственно с первым выходом дешифратора микроопераций и входом третьего элемента НЕ, первый и второй входы второй группы входов, первый и второй входы третьей группы входов и первый и второй входы четвертой группы входов мультиплексора адреса подключены.соответственно к выходу первого элемента И и информационному входу устройства, вьгходу второго элемента И и информационному входу устройства, выходу третьего элемента НЕ и выходу суматора адреса ,

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1982 |

|

SU1019450A1 |

| Микропрограммное устройство управления (его варианты) | 1983 |

|

SU1125625A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1109751A1 |

| Микропрограммное устройство для контроля и управления | 1985 |

|

SU1325476A1 |

| Устройство для микропрограммного управления | 1983 |

|

SU1188742A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1522203A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1142833A1 |

| Микропрограммное устройство управ-лЕНия | 1978 |

|

SU807288A1 |

| Устройство для программного управления и контроля | 1985 |

|

SU1280574A1 |

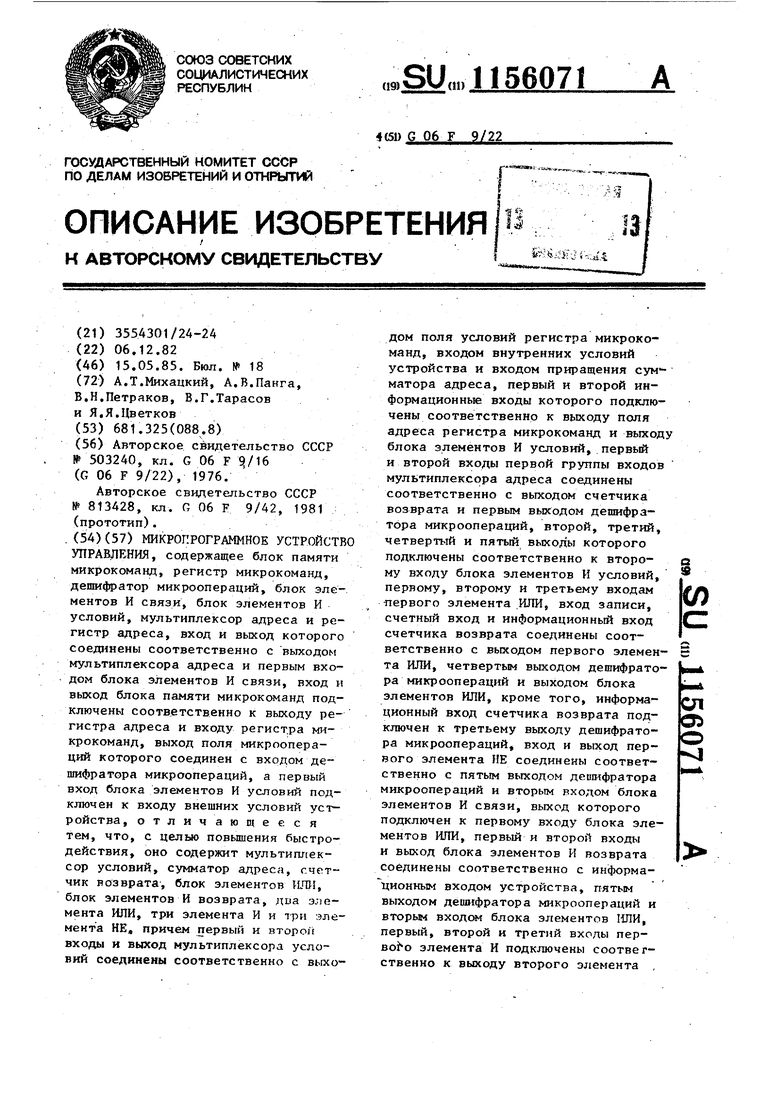

МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ, содержащее блок памяти микрокоманд, регистр микрокоманд, дешифратор микроопераций, блок элементов И связи, блок элементов И условий, мультиплексор адреса и регистр адреса, вход и выход которого соединены соответственно с выходом мультиплексора адреса и первым входом блока элементов И связи, вход и выход блока памяти микрокоманд подключены соответственно к выходу регистра адреса и входу регистра микрокоманд, выход поля микроопераций которого соединен с входом дешифратора микроопераций, а первый вход блока элементов И условий подключен к входу внешних условий устройства, отличающееся тем, что, с целью повьшения быстродействия, оно содержит мультишсексор условий, сумматор адреса, счетчик возврата, блок элементов ИЛИ, блок элементов И возврата, два элемента ИЛИ, три элемента И и три элемента НЕ, причем первый и BTopoit входы и выход мультиплексора условий соединены соответственно с выхо дом поля условий регистра микрокоманд, входом внутренних условий устройства и входом приращения сумматора адреса, первый и второй информационные входы которого подключены соответственно к вькоду поля адреса регистра микрокоманд и выходу блока элементов И условий, первый и второй входы первой группы входов мультиплексора адреса соединены соответственно с выходом счетчика возврата и первым выходом дешифратора микроопераций, второй, третий, четвертый и пятый выходы которого подключены соответственно к второму входу блока элементов И условий, W первому, второму и третьему входам первого элемента ИЛИ, вход записи, счетный вход и информационный вход счетчика возврата соединены соответственно с выходом первого элемента ИЛИ, четвертым выходом дешифратора микроопераций и выходом блока элементов ИЛИ, кроме того, информаСП ционный вход счетчика возврата подо: ключен к третьему выходу дешифратора микроопераций, вход и выход первого элемента НЕ соединены соответственно с пятым выходом дешифратора микроопераций и вторьтм входом блока элементов И связи, выход которого подключен к первому входу блока элементов ИЛИ, первый и второй входы и выход блока элементов И возврата соединены соответственно с информационным входом устройства, пятым выходом дешифратора микроопераций и вторьм входом блока элементов 11ЛИ, первый, второй и третий входы первo o элемента И подключены соответственно к БЕЛСоду второго элемента

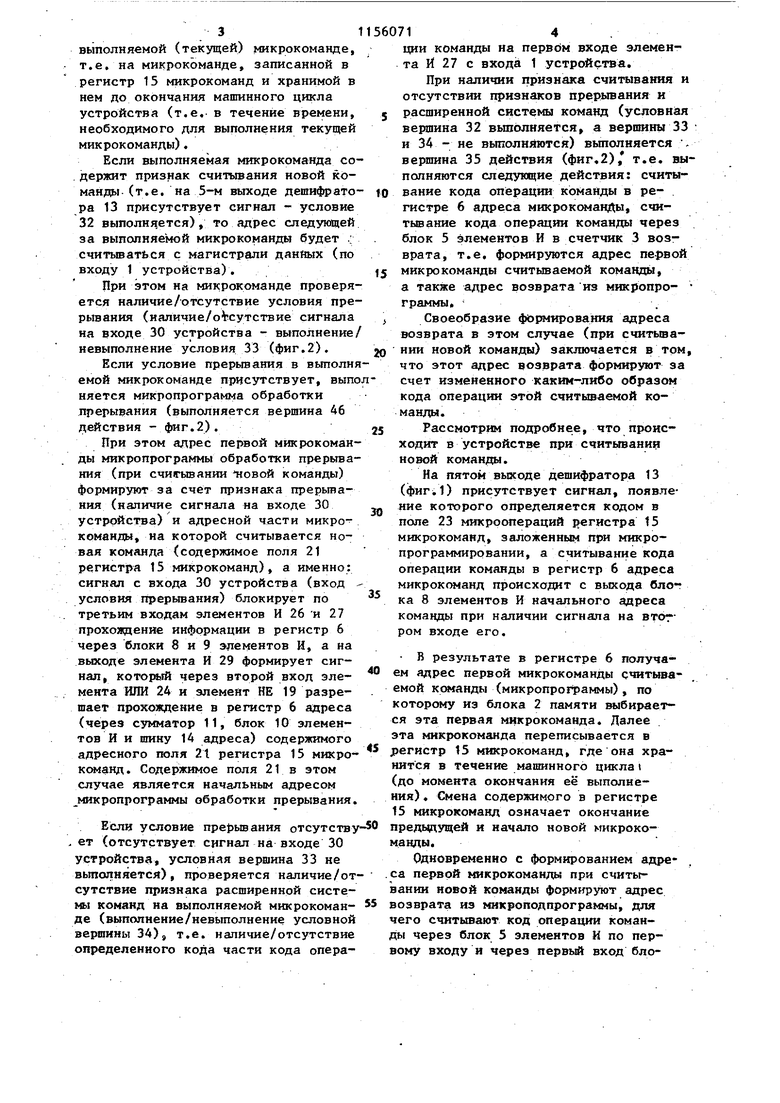

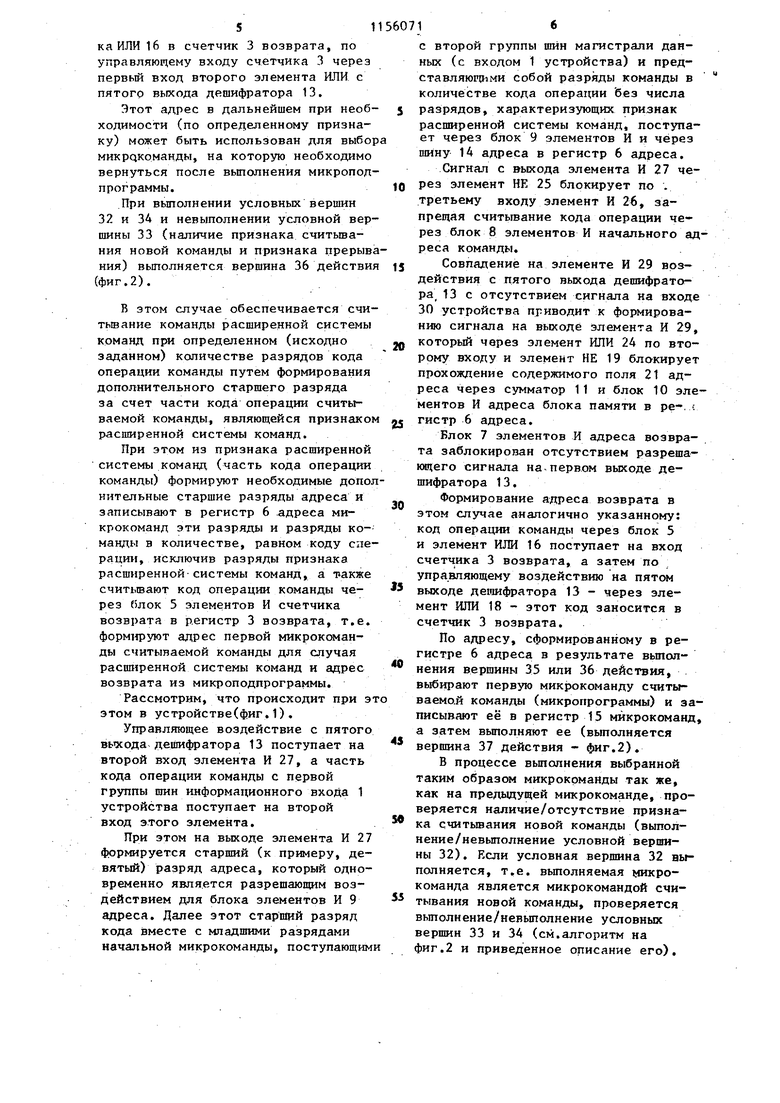

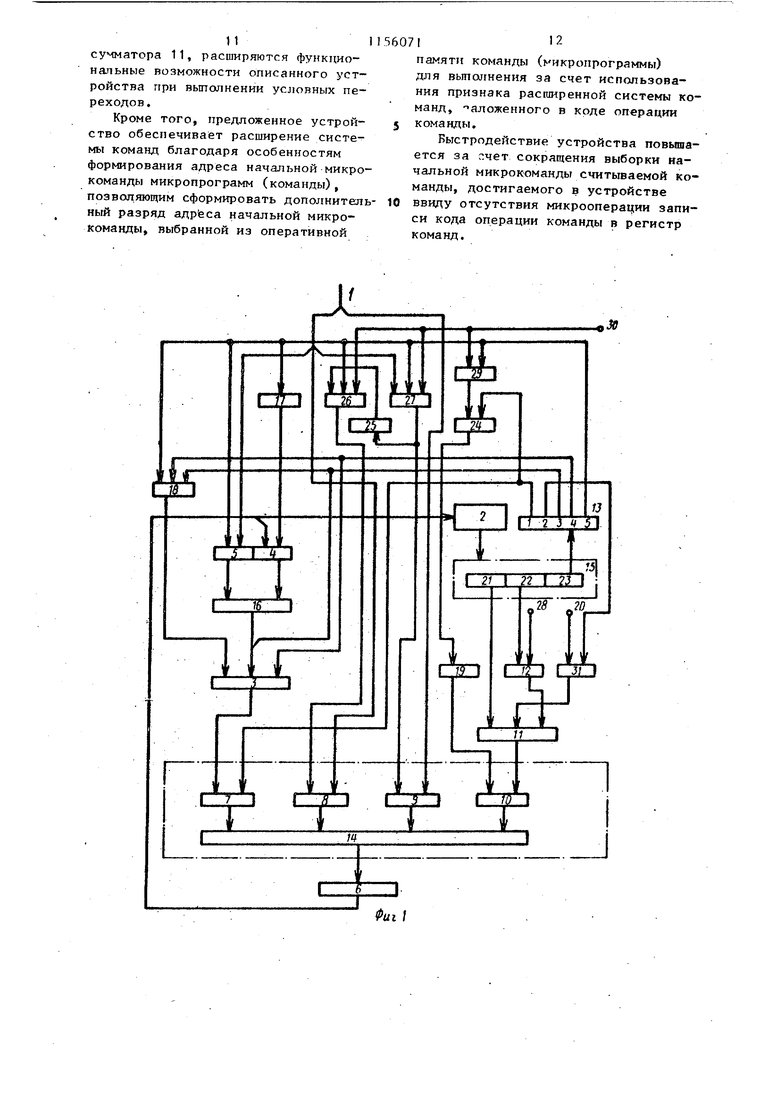

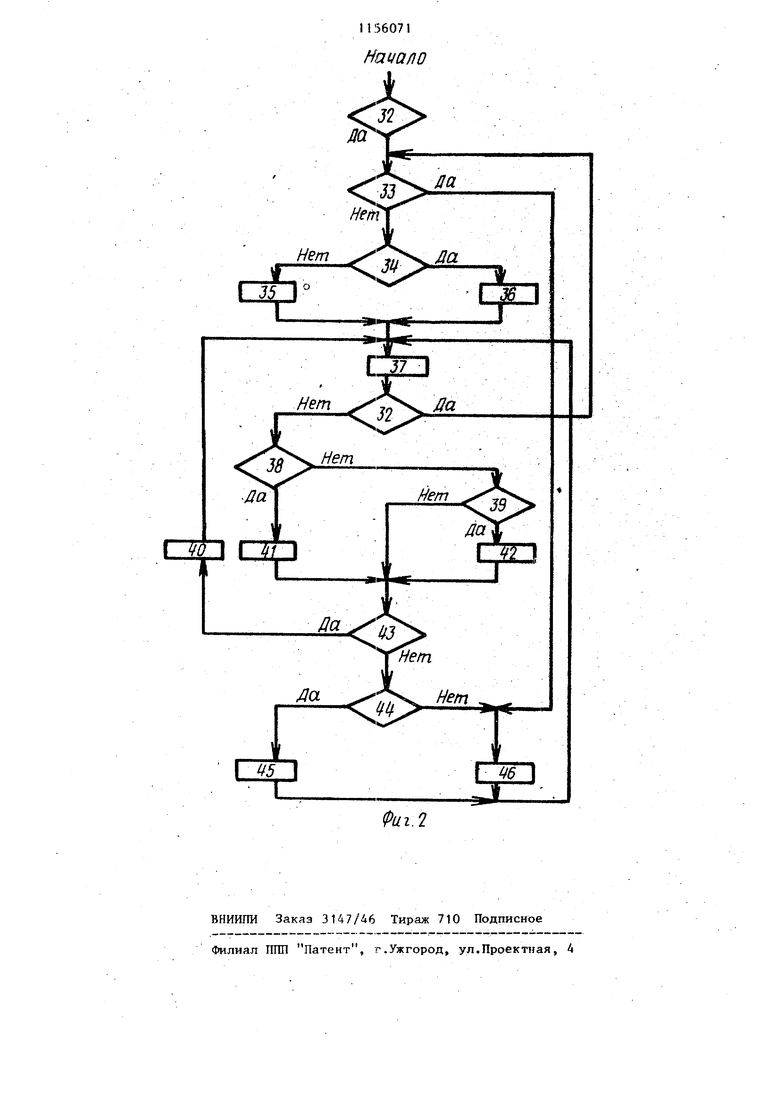

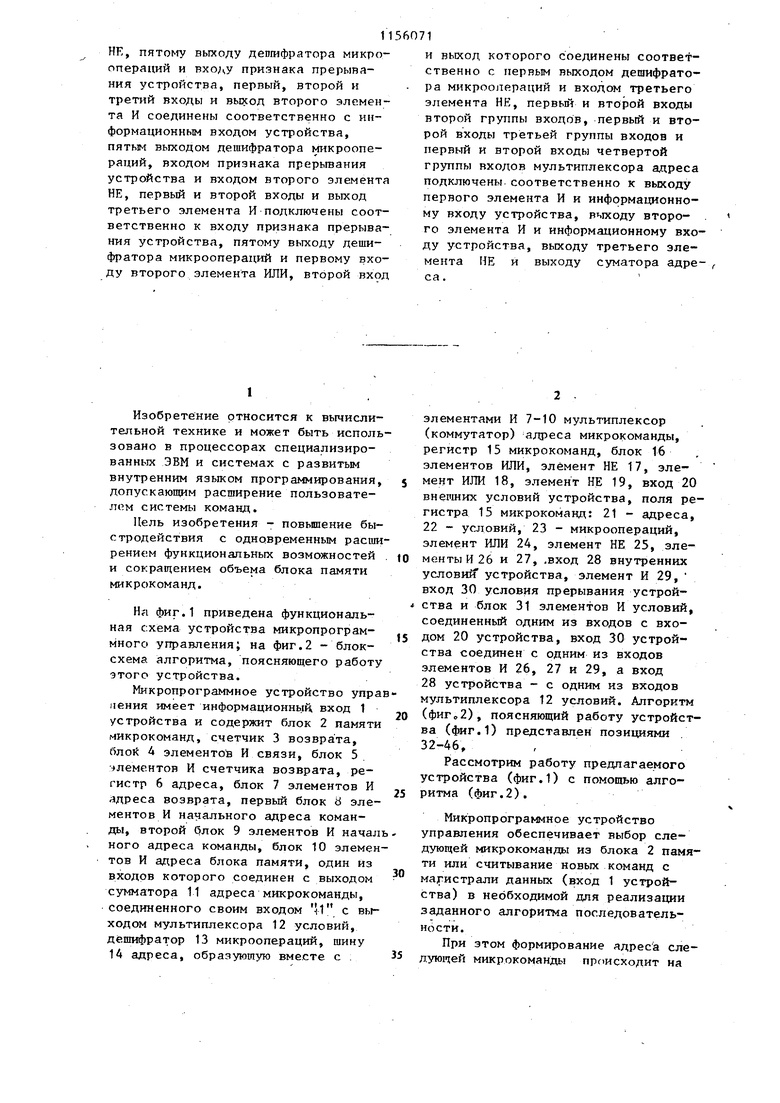

Изобретение относится к вычислительной технике и может быть исполь зовано в процессорах специализированных ЭВМ и системах с развитым внутренним язьжом программирования допускающим расширение пользователем системы команд. Цель изобретения - повышение быстродействия с одновременным расши рением функциональных возможностей и сокращением объема блока памяти микрокоманд. Ня фиг.1 приведена функциональная схема устройства микропрограммного управления; на фиг.2 - блоксхема алгоритма, поясняющего работу этого устройства. Микропрограммное устройство упра пения имеет информационнык вход 1 устройства и содержит блок 2 памяти микрокоманд, счетчик 3 возврата, бло 4 элементов И связи, блок 5. : лементов И счетчика возврата, регистр 6 адреса, блок 7 элементов И адреса возврата, первый блок в элементов И начального адреса команды, второй блок 9 элементов И начал ного адреса команды, блок 10 элемен тов И адреса блока памяти, один из входов которого соединен с выходом сумматора 11 адреса микрокоманды, соединенного своим входом 1 с вьг ходом мультиплексора 12 условий, де.шифратор 13 микроопераций, шину 14 адреса, образутошую вместе с : элементами И 7-10 мультиплексор (коммутатор) адреса микрокоманды, регистр 15 микрокоманд, блок 16 элементов ИЛИ, элемент НЕ 17, элемент ИЛИ 18, элемент НЕ 19, вход 20 внешних условий устройства, поля регистра 15 микрокоманд: 21 - адреса, 22 - условий, 23 - микроопераций, элемент ИЛИ 24, элемент НЕ 25, элементы И 26 и 27, .вход 28 внутренних условии устройства, элемент И 29, вход 30 условия прерывания устройства и блок 31 элементов И условий, соединенный одним из входов с входом 20 устройства, вход 30 устройства соединен с одним из входов элементов И 26, 27 и 29, а вход 28 устройства - с одним из входов мультиплексора 12 условий. Апгоритм (фиг,2), поясняющий работу устройства (фиг.1) представлен позициями 32-46, Рассмотрим работу предлагаемого устройства (фиг.1) с помоиью алгоритма (фиг.2). Микропрограммное устройство управления обеспечивает выбор следующей микрокоманды из блока 2 памяти или считывание новых команд с магистрали данных (вход 1 устройства) в необходимой для реализации заданного алгоритма последовательности. При этом формирование адреса следующей микрокоманды прг)исходит на выполняемой (текущей) микрокоманде, т.е. на микрокоманде, записанной в регистр 15 микрокоманд и хранимой в нем до окончания машинного цикла устройства (т.е. в течение времени, необходимого для выполнения текущей микрокоманды). Если выполняемая микрокоманда содержит признак считьгоания новой команды (т.е. на 5-м выходе дешифрато ра 13 присутствует сигнал - условие 32 выполняется), то адрес следуняцей за выполняемой микрокоманды будет .; считьшатЬся с магистрали данных (по входу 1 устройства). При этом на микрокоманде проверяется наличие/отсутствие условия прерывания (наличие/отсутствие сигнала на входе 30 устройства - выполнение/ невыполнение условия 33 (фиг.2). Если условие прерьшания в выполня емой микрокоманде присутствует, выпо няется микропрограмма обработки прерывания (выполняется вершина 46 действия - фиг.2). При этом адрес первой микрокоманды микропрограммы обработки прерывания (при счи1гывании новой команды) формируют за счет признака прерывания (наличие сигнала на входе 30 устройства) и адресной части микрокоманды, на которой считывается новая команда (содержимое поля 21 регистра 15 микрокоманд), а именно: сигнал с входа 30 устройства (вход условия прерывания) блокирует по третьим входам элементов И 26 и 27 прохождение информации в регистр 6 через блоки 8 и 9 элементов И, а на выходе элемента И 29 формирует сигнал, когорыН через второй вход элемента ИЛИ 24 и элемент НЕ 19 разрешает прохождение в регистр 6 адреса (через сумматор 11, блок 10 элементов И и шину 14 адреса) содержимого адресного 1голя 21 регистра 15 никрокс 1анд. Содержимое поля 21 в этом случае является начальным адресом микропрограммы обработки прерывания. Если условие прерьшания отсутству , ет (отсутствует сигнал на входе 30 устройства, условная вершина 33 не вьтолняется), проверяется наличие/от сутствие признака расширенной системы команд на выполняемой микрокоман- 55 де (выполнение/невьтолнение условной вершины 34), т.е. наличие/отсутствие определенного кода части кода операции команды на первом входе элемента И 27 с входа 1 устройства. При наличии признака считывания и отсутствии признаков прерывания и расширенной системы команд (условная вершина 32 вьшолняется а вершины 33 и 34 - не вьшолнйются) выполняется . вершина 35 действия (фиг,2)/ т.е. выполняются следующие действия: считывание кода операции команды в регистре 6 микрокс «анДы, считывание кода операции команды через блок 5 элементов И в счетчик 3 возврата, т.е. формируются адрес пе-рвой микрокоманды считываемой команды, а также адрес возврата из микропро- граммы, Своеобразие формирования адреса возврата в этом случае (при считьшаНИИ новой команды) заключается в том, что этот адрес возврата формируют за счет измененного каким-либо образом кода операции этой считываемой команды. Рассмотрим подробнее, что происходит в устройстве при считывании новой команды. На пятом выходе дешифратора 13 (фиг.1) присутствует сигнал, появление которого определяется кодом в поле 23 микроопераций регистра 15 микрокоманд, заложенным при микропрограммировании, а считывание кода операции команды в регистр 6 адреса микрок(4анд происходит с выхода блока 8 элементов И начального адреса команды при наличии сигнала на втог ром входе его. - В результате в регистре 6 получам адрес первой микрокоманды считывамой ксманды (микропрограммы), по оторому из блока 2 памяти выбираетя эта первая микрокоманда. Далее та микрокоманда переписывается в егистр 15 микрокоманд, где она храится в течение машинного циклаi до момента окончания её выполнеия) . Смена содержимого в регистре 5 микрокоманд означает окончание редццущей и начало новой микрокоанды. Одновременно с формированием адре а первой микрокоманды при считыании новой команды формируют адрес возврата из микроподпрограммы, для чего считывают код операции команды через блок 5 элементов Н по первому входу и через первый вход блока ИЛИ 16 в счетчик 3 возврата, по управляющему входу счетчика 3 через первый вхол второго элемента ИЛИ с пятого выхода дешифратора 13. Этот адрес в дальнейшем при необходимости (по определенному признаку) может быть использован для выбор микракоманды, на которую необходимо вернуться после вьтолнения микроподпрограммы. При выполнении условных вершин 32 и ЗД и невыполнении условной вершины 33 (наличие признака считьшания новой команды и признака прерыв ния) вьтолняется вершина 36 действия (фиг. 2). В этом случае обеспечивается считьюание команды расширенной системы команд при определенном (исходно заданном) количестве разрядов кода операции команды путем формирования дополнительного старшего разряда за счет части кода операции считываемой команды, являющейся признаком расширенной системы команд. При этом из признака расширенной системы команд (часть кода операции команды) формируют необходимые допол нительные старшие разряды адреса и записывают в регистр 6 .адреса микрокоманд эти разряды и разряды команды в количестве, равном коду опе рации, ИС1СПЮЧИВ разряды признака расширенной системы команд, а также считьгоают код операции команды через блок 5 элементов И счетчика возврата в регистр 3 возврата, т.е. формируют адрес первой микрокоманды считываемой команды для случая расширенной системы команд и адрес возврата из микроподпрограммы. Рассмотрим, что происходит при э этом в устройстве(фиг.1). Управляющее воздействие с пятого вьтхода дешифратора 13 поступает на второй вход элемента И 27, а часть кода операции команды с первой группы шин информационного входа 1 устройства поступает на второй вход этого элемента. При этом на выходе элемента И 27 фор1 руется старший (к примеру, девятый) разряд адреса, который одновременно является разрешающим воздействием для блока элементов И 9 адреса. Далее этот старший разряд кода вместе с младшими разрядами начальной микрокоманды, поступающим с второй группы шин магистрали данных (с входом 1 устройства) и представляющими собой разряды команды в количестве кода операции без числа разрядов, характеризующих признак расширенной системы команд, поступает через блок 9 элементов И и через пину 14 адреса в регистр 6 адреса. Сигнал с выхода элемента И 27 через элемент НЕ 25 блокирует по . третьему входу элемент И 26, запрещая считывание кода операции через блок 8 элементов И начального адреса команды. Совпадение на элементе И 29 воздействия с пятого выхода депшфратора, 13 с отсутствием сигнала на входе 30 устройства приводит к формированию сигнала на выходе элемента И 29, который через элемент ИЛИ 24 по второму входу и элемент НЕ 19 блокирует прохождение содержимого поля 21 адреса через сумматор 11 и блок 10 элементов И адреса блока памяти в ре-. гистр 6 адреса. Блок 7 элементов И адреса возврата заблокирован отсутствием разрешакицего сигнала на.первом выходе дешифратора 13. Формирование адреса возврата в этом случае аналогично указанному: код операции команды через блок 5 и элемент ИЛИ 16 поступает на вход счетчика 3 возврата, а затем по упра.вляющему воздействию на пятом выходе деишфратора 13 - через элемент ИЛИ 18 - этот код заносится в счетчик 3 возврата. По адресу, сформированному в регистре 6 адреса в результате вьтолнения вершины 35 или 36 действия, выбирают первую микрокоманду считываемой команды (микропрограммы) и записывают её в регистр 15 микрокоманд, а затем вьтолняют ее (выполняется вершина 37 действия - фиг.2). В процессе выполнения выбранной таким образом микрокоманды так же, как на предыдущей микрокоманде, проверяется наличие/отсутствие признака считьгоания новой команды (выполнение/невьшолнение условной вершины 32). Если условная вершина 32 abfполняется, т.е. выполняемая микрокоманда является микрокомандой считывания новой команды, проверяется выполнение/невыполнение условных вершин 33 и 34 (см.алгоритм на фиг.2 и приведенное описание его). Наличие в микропрограммах одинаковьк последовательностей, а также одинаковизс микрокоманд позволило использовать в предпагаемом устройстве микроподпрограммы. Причем эти микроподпрограммы могут располагать ся по всему объему блока 2 памяти, так как переход на первую микрокоманду микрополпрограммы осуществляется за счет адресного поля 21 регистра 15 микрокоманд, при этом необходимо обеспечить возможность воз вращения в свсяо микропрограмму посл окончания вьшолнения микроподпрогра мы. Формирование адреса возврата в микропрограмму при считывании новой команды (выполнение условной вершин 32) и для случая расширенной систем команд (выполнение условньк вершин 32 и 34) уже описано , вьппе. Рассмотрим, каким образом формируется адрес возврата при вьтолнени текущей микрокоманды (условная вершина 32 после вершины 37 действия не вьшолняется). ЕСЛИ выполняемая микрокоманда не является микрокомандой считывания новой команды (условная вершина 32 не вьшопняется), проверяется наличие/отсутствие в ней первого признака формирования адреса возврата (вьшолнение/Иевыполнение условной .вершины 38 алгоритма и, соответстве но, наличие/отсутствие сигнала на четвертом выходе дешифратора 13 фиг.1). Если выполняемая микрокоманда является микрокомандой, на которой осу ществляется переход на микропрограмму, и на четвертом выходе дешифратора t3 присутствует сигнал (выполнение условной вершины 38), то адрес возврата из. микроподпрограммы формируется за счет содержимого регистра 6 адреса, представляющего собой адрес этой выполняемой микрокоманды. Содержимое регистра 6 адреса по управляющему воздействию выхода элемента ИЛИ 18 на первый вход счетчика 3 возврата записывается в него, а воздействием по второму управляюще му входу счетчика 3 возврата с четвертого выхода дешифратора 13 содержимое счетчика 3 возврата увеличивается на единицу. Полученньй таким об разом адрес, представляющий собой адрес выполняемой микрокоманды, увел ченнь1Й на единицу, является адресом микрокоманды, на которую необходимо вернуться в микропрограмму после выполнения микроподпрограммы (адрес возврата). Если вьтолняемая микроко- . манда не является микрокомандой считывания :ювой команды (условная вершина 32 не выполняется) и не содержит первый признак формирования адреса возврата (условная вершина 38 не выполняется), то проверяется наличие/отсутствие в ней второго признака формирования адреса возврата (выполнение/невьтолнение условной вершины 39), и соответственно нали.чие/отсутствие сигнала на третьем выходе дешифратора 13. Если выполняемая микрокоманда является микрокомандой перехода на микроподпрограмму и на третьем выходе дешифратора 13 присутствует сигнал (условия вершины 39 выполняется, т.е. микрокоманда содержит второй признак формирования адреса возврата), то адрес микрокоманды, на которую необходимо вернуться после выполнения микроподпрограммы(адрес возврата) , форми1 уется логическим сложением сигнала с третьего выхода дешифратора 13 и содержимого регистра 6 в блоке 16 элементов ИЛИ с последующим воздействием результата этого сложения на счетчик 3 по управляющему воздействию с выхода элемента ИЛИ 18. Использование адреса возврата, сформированного одним из описанных способов и хранимого в счетчике 3, производится по особому признаку (наличие сигнала на первом выходе дешифратора 13), который может быть заложен в последней микрокоманде любой микроподпрограммы. В этом случае (возврат из микроподпрограммы) сигнал с первого выхода дешифратора 13 через элемент ИЛИ 24 и элемент НЕ 19 блокирует прохождение содержимого адресного поля 21 через сумматор 11, блок 10 элементов И и шину 14, а по второму входу блока 7 элементов И разрешает прохождение содержимого счетчика 3 через блок 7 и шину 14 регистр 6, т.е. при положительном ешении вершины 43 при необходимоси возврата в микропрограмму после ьтолнения микроподпрограммы выполнятся вершина 40 (фиг.2). В результае содержимое счетчика 3 записываетя в регистр 6 и выбирает по данному .адресу в блоке 2 памяти микрокоманду, на которую необходимо вернуться после выполнения микроподпрограммы, т.е. осуществляется возврат из микроподпрограммы в вьшолняемую микропрограмму. При невыпопнении условной вершины 43, т.е. при отсутствии необходимости возврата в микропрограмму, проверяется выполнение/невыполнение условной вершины 44 (наличие/отсутствие признака условного перехода или выполнение условия и соответственно наличие сигнала на входе 28 (вход внутренних условий) или на вхо де 20 (внешних условий устройства). Бели условная верпшна 44 выполняется, т.е. выполняемая микрокоманда является условной микрокомандой, требующей анализа условий, поступаю щих на вход 20 или 28, то вьшолняет ся вершина действия 45, а именно: в регистр 6 записьюается арифметическая сумма кода поля 21, являющегося адресной частью вьшолняемой микрокоманды, результата выходного состояния мультиплексора 12 и кода условий. Рассмотрим подробнее, каким обра зом формируется адрес следующей микрокоманды для. случая условной микроксманды (условная вершина 44 выполняется), т.е. адрес перехода. Если на вход 28 (вход внутренних условий устройства) поступают условия, то код поля 22 регистра 15 определяет тторядковь й номер проверя емого условия, а выход мультиплексо ра 12 определяет, выполняется данно условие ипи нет. Если проверяемое условие, поступающее на вход 28, вы полняется, то адресная часть поля 2 регистр а 15, поступающая на вход А сумматора 11 увеличивается на едини цу,- а если условие не вьшолняется, адресная часть поля регистра 15 не изменяется. Если при этом с входа 20 (внешних условий) также поступает код условия на первый вход блока 31 эле ментов И, а на второй вход последнего поступает сигнал с второго вых да дешифратора 13, то адрес следующей микрокоманды (адрес микрокоманды условного перехода) будет арифме

тической суммой сигналов на трех входах: адресной части поля 21 регистра 15, вьйоде блока элементов И

йать адрес микрокоманды при условных переходах за счет арифметической суммы кодов, поступаюгцих на вход и выходе мультиппёксора 12. Такое формирование адреса микрокоманды условного перехода значительно расширяет возможности условных переходов в микропрограммах. Если условная вершина 44 не выполняется, т.е. вьшрлняемая микрокоманда не является условной микрокомандой, то выполняется вершина 46 действия, а именно в регистр 6 записывается содержимое адресного поля 21 регистра 15 выполняемой микрокоманды, представляющее собой адрес следующей микрокоманды, т.е. в блоке 2 памяти выбиратеся следующая микрокоманда. В этом случае на каждом машинном цикле выбора микрокоманды из блока 2 памяти и занесения ее в регистр 15 содержимое поля 21 регистра 15 через сумматор 11, блок 10 злементов И и шину 14 записьшается в регистр 6. Отсутствие сигналов на первом и пятом выходах дешифратора 13 (отсутствие признаков возврата из микроподпрограммы и считывания новой команды) блокирует блоки 7-9 элементов И и разрешает прохождение содержимого поля 21 регистра 15 через сумматор 11, блок 10 элементов И и тшну 14 в регистр 6. Таким образом, совокупность аппаратных средств устройства позволяет построить микро фограммы так, что каждая микрокоманда блока 2 памяти может быть использована более чем в одной микропрограмме, т.е. позволяет создавать микроподпрограммы, переход на которые возможно осуществлять по любому адресу блока 2. При этом использование блока 5 элементов И в данном устройстве позволяет сформировать адрес возврата из микроподпрограммы на первой микрокоманде команды (микропрограммы). Формирование адреса возврата с помощью блока 5 и использование при зтом признака формирования возврата обеспечивает возможность вьшолнения двух и более микроподпрограмм подряд без промежуточного возвращения в свою микропрограмму, что позволяет значительно сократить объем блока 2 памяти. Использование в устройстве отдельных от счетчика 3 мультиплексора 12 и сумматора 11, позволяющих формиро11сумматора 11, расширяются функциональные возможности описанного устройства при выпагшении условных переходов. Кроме того, предложенное устройство обеспечивает расширение системы команд благодаря особенностям формирования адреса начальной микро команды микропрограмм (команды), позводяющим сформировать дополнител ный разряд адреса начальной микроКоманды, выбранной из оперативной 1 памяти команды (микропрограммы) для вьтшгнения за счет использования признака рас1ииренной системы команд, заложенного в коде операции команды. Быстродействие устройства повышается за счет сокращения выборки начальной микрокоманды считываемой команды, достигаемого в устройстве ввиду отсутствия микрооперации записи кода операции команды в регистр команд

Hanafio

| Микропрограммное устройство управления | 1974 |

|

SU503240A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство управления микропрограм-МНыМи пЕРЕХОдАМи | 1979 |

|

SU813428A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| . | |||

Авторы

Даты

1985-05-15—Публикация

1982-12-06—Подача