коммутатора, выход которого соединен с информационным входом регистра операндов, выход которого соединен с первым информационным входом коммутатора, с первым входом второго элемента И и с входом элемента НЕ, выход которого подключен к первому входу третьего элемента И, второй и третий информационные входы коммутатора соединены соответственно с выходами первого и второго триггеров, четвертьй информационньй вход коммутатора подключен к выходу однобитового логического устройства, второй и третий адресные входы коммутатора соединены соответственно с первым и вторым выходами дешифратора команд, третий выход которого подключен к третьему входу элемента И-НЕ, выход регистра выбора операндов соединен с его последним входом и с вторыми входами второго и третьего элементов И, выходы второго и третьего элементов И соединены соответственно с единичными и нулевыми входами второго и первого триггеров, установочный вход первого триггера является входом логической 1 процессора, установочный вход второго триггера является входом логического О процессора, входы синхронизации первого и второго триггеров соединены с первым выходом дешифратора сигналов управления.

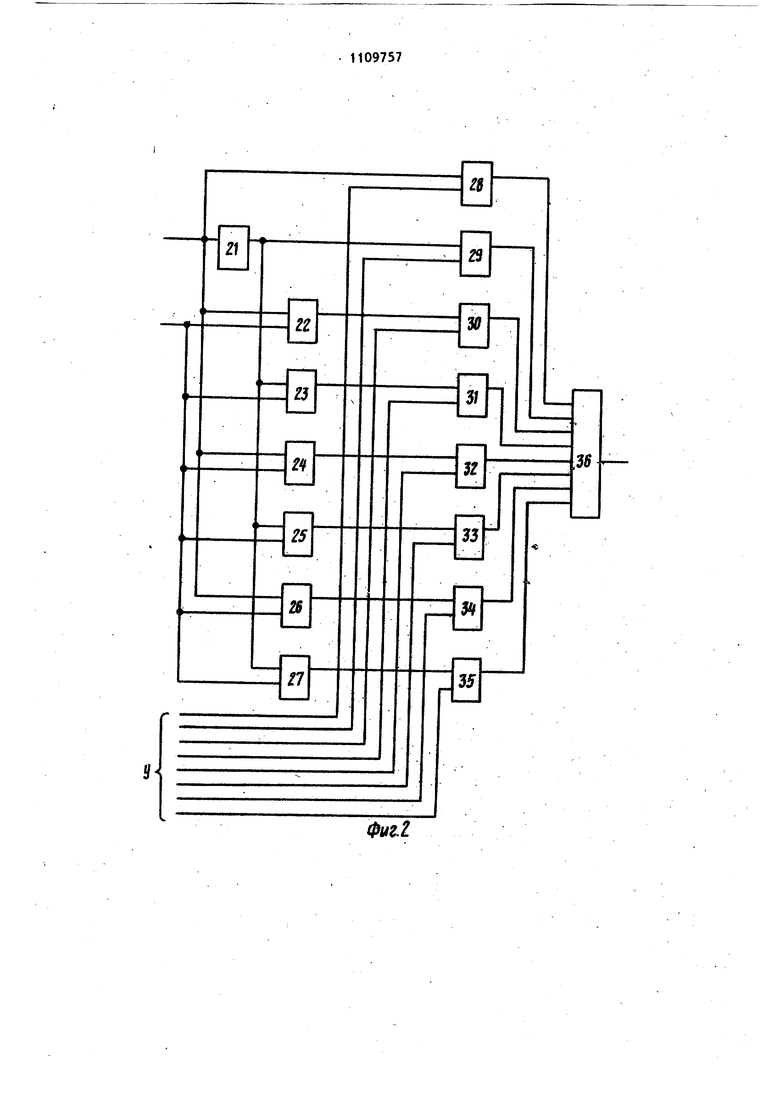

2. .Процессор по п. 1, отличающийся тем, что устройство выполнения логических операций содержит элемент НЕ, десять элементов И, три элемента ИЛИ и два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, причем первый информационный вход устройства соединен с входом элемента НЕ, с первыми входами первых элементов ИЛИ, И, ИСКЛЮЧАЮЩЕЕ ИЛИ, с .первым входом второго элемента И, второй информационный вход устройства соединен с вторыми входами первого элемента ИЛИ, второго элемента И, первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и с первыми входами второго элемента ИЛИ, третьего элемента И, второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход элемента НЕ подключен к вторым входам второго элемента ИЛИ третьего элемента И, второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и к первому входу четвертого элемента И, выход первого элемента ИЛИ соединен с первым входом пятого элемента И, выход второго элемента ИЛИ соединен с первьт входом шестого элементами, выход второго элемента И соединен с первым входом седьмого элемента И, выход третьего элемента И соединен с первым входом восьмого элемента И, выход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с первым входом девятого элемента И, выход второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с первым входом десятого элемента И, вторые входы первого, четвертого, пятого, шестого, седьмого, восьмого, девятого и десятого элементов И подключены соответственно к управляющим входам устройства, выходы первого, четвертого, пятого, шестого, седьмого, восьмого, девятого и десятого элементов подключены к соответствукщим входам третьего элемента ИЛИ, выход которого является вькодом устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Центральный процессор | 1979 |

|

SU960830A1 |

| Процессор цифровой вычислительной машины | 1979 |

|

SU1164723A1 |

| Процессор | 1984 |

|

SU1247884A1 |

| Процессор параллельной обработки | 1990 |

|

SU1797126A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Параллельный процессор | 1985 |

|

SU1315989A1 |

| Процессор для обработки массивов данных | 1982 |

|

SU1381532A1 |

| Ячейка однородной вычислительной среды | 1986 |

|

SU1386987A1 |

| Устройство для обмена информацией | 1983 |

|

SU1149239A1 |

| Ассоциативный параллельный процессор | 1981 |

|

SU1166128A1 |

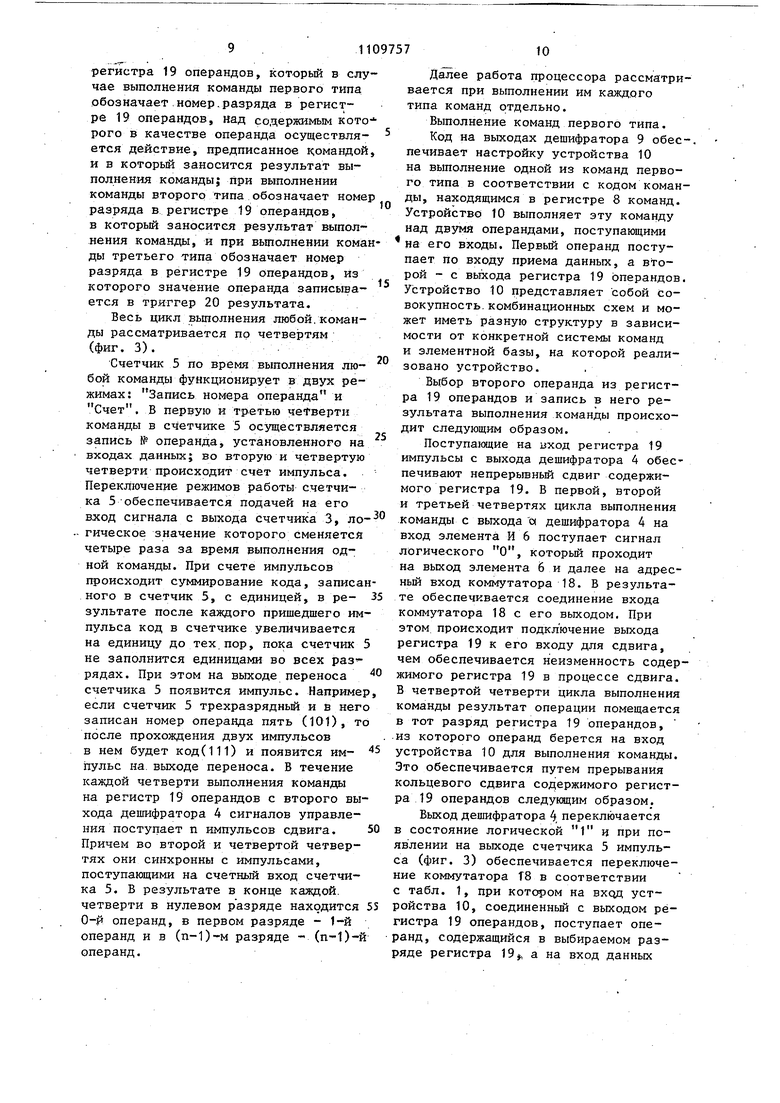

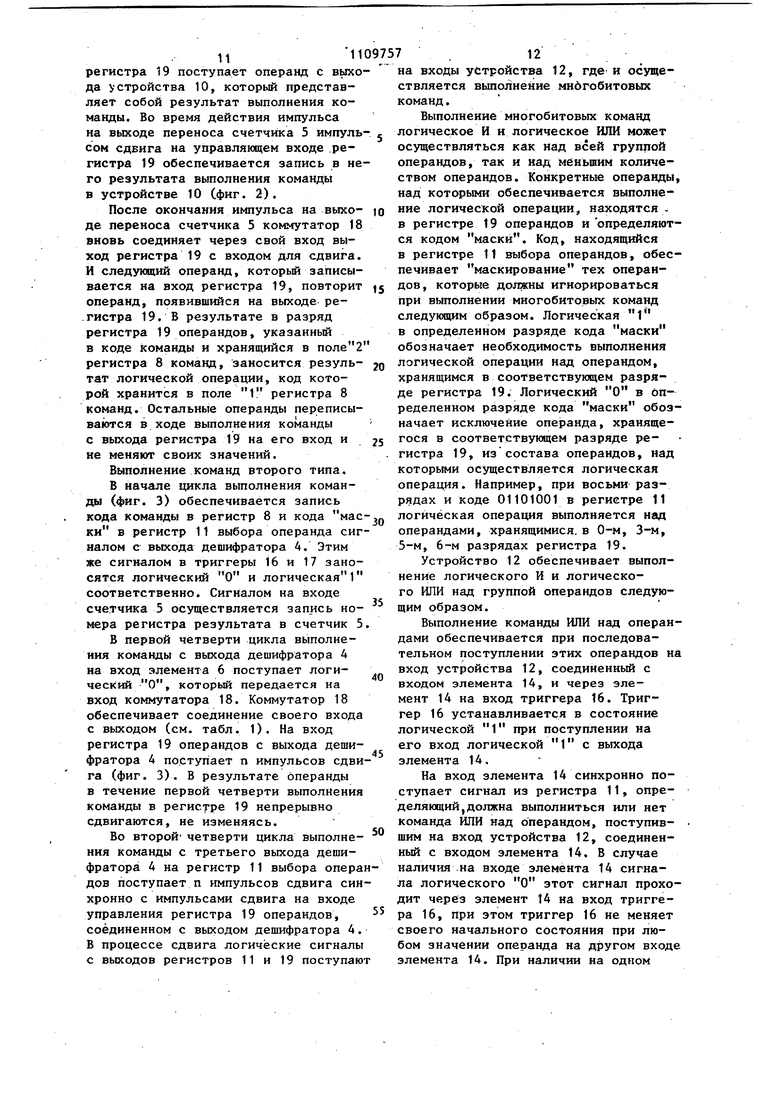

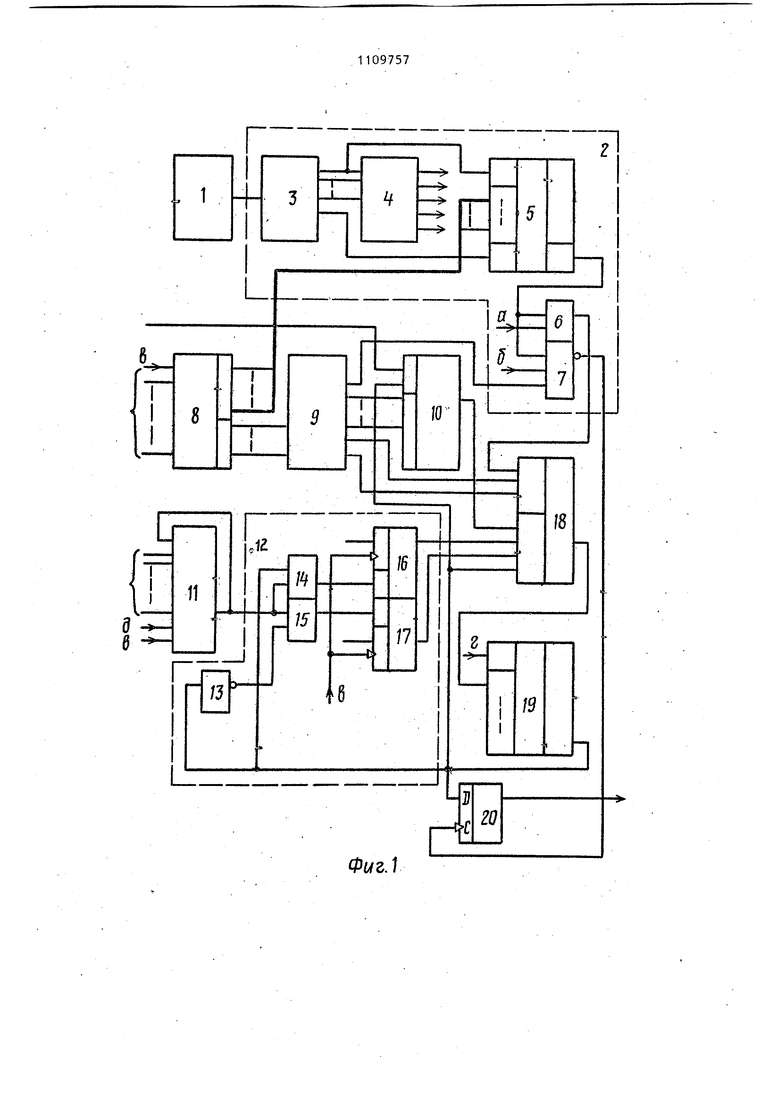

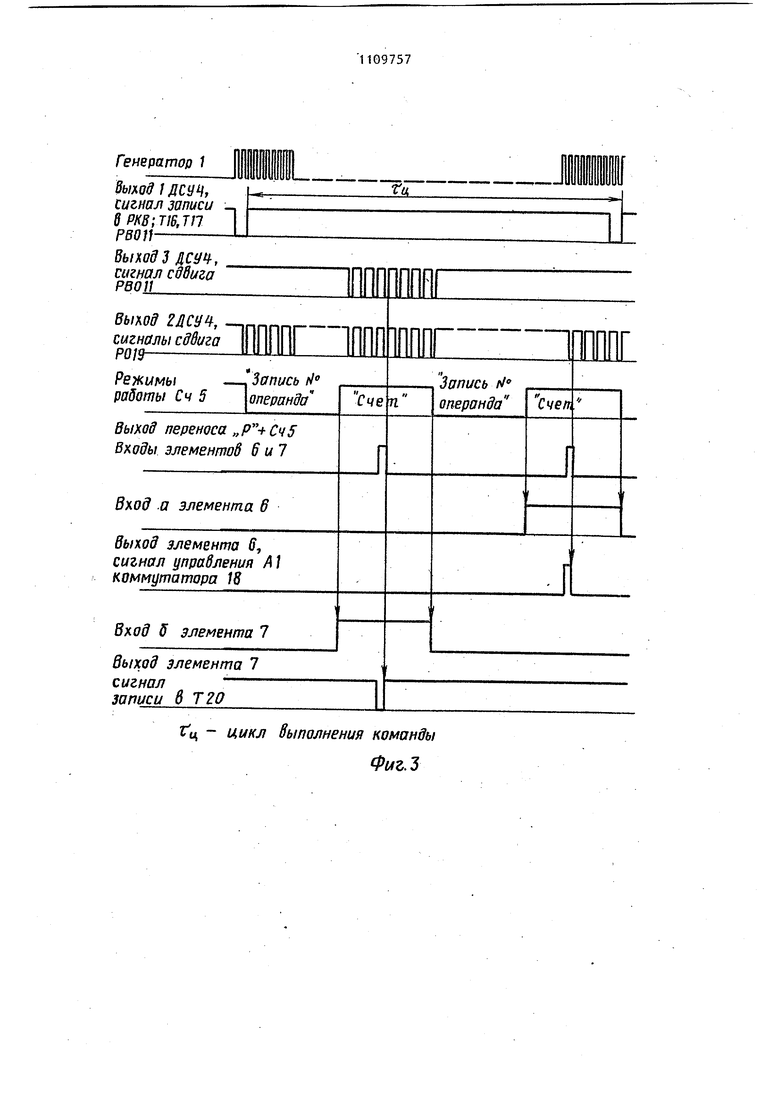

1. ПРОЦЕССОР, содержащий генератор тактовых импульсов, устройство управления, включающее два счетчика, дешифратор сигналов управления, элементы И, И-ИЕ, причем счетный вход первого счетчика соединен с выходом генератора тактовых импульсов, выход первого разряда первого счетчика соединен с йервым информационным входом дешифратора сигналов управления и счетным входом второго счетчика, выход второго разряда первого счетчика подключен к управляющему входу второго счетчика, выходы разрядов первого счетчика, начиная с третьего, соеди- нены соответственно с информационными входами дешифратора сигналов управления, начиная с второго, первый выход дешифратора сигналов управления подключен к управляющему входу регистра команд, второй выход - к управляющему входу регистра операндов, третий выход - к первому входу первого элемента И, чётвертьй выход соединен с первым входом элемента И-НЕ, вторые входы первого элемента И и элемента И-НЕ соединены с выходом переноса второго счетчика, информационные входы которого соединены соответственно с выходами первой группы регистра команд, выход элемента И-НЕ соединен с синхронизирующим входом триггера результата, вход данных регистра команд является входом кода команды процессора, выходы второй группы регистра команд соединены соответственно с входами дешифратора команд, группа выходов которого соединена .соответственно с управляющими входами устройства выполнения логи(П ческих операций, первый информационный вход которого является входом приема данных процессора, выход регистра операндов подключен к второму информационному входу устройства выполнения логических операций и к информационному входу триггера результата, выход которого является выходом процессора, отличающийся тем, что, с целью повышеел ния быстродействия при упрощении про граммирования, в него введены регистр выбора операндов, коммутатор, второй и третий элементы И, элемент НЕ и два триггера, причем первый управляющий вход регистра выбора операндов соединен с пятымвыходом дешифратора сигналов управления, первый выход которого соединен с вторым управляющим входом регистра выбора операндов, информационные входы которого являются входами кода маски процессора, выход первого элемента И подключен к первому адресному входу

I

Изобретение-относится к вычислительной технике и может быть использовано, в частности, в управляющих системах с программным управлением, в цифровых вычислительных машинах и в программируемых контроллерах.

Известны микропроцессоры, которые представляют собой программно-управляемые устройства, осуществляющие прием, обработку и вьщачу цифровой информации, построенные на одной или

.нескольких интегральных микросхемах Ci .

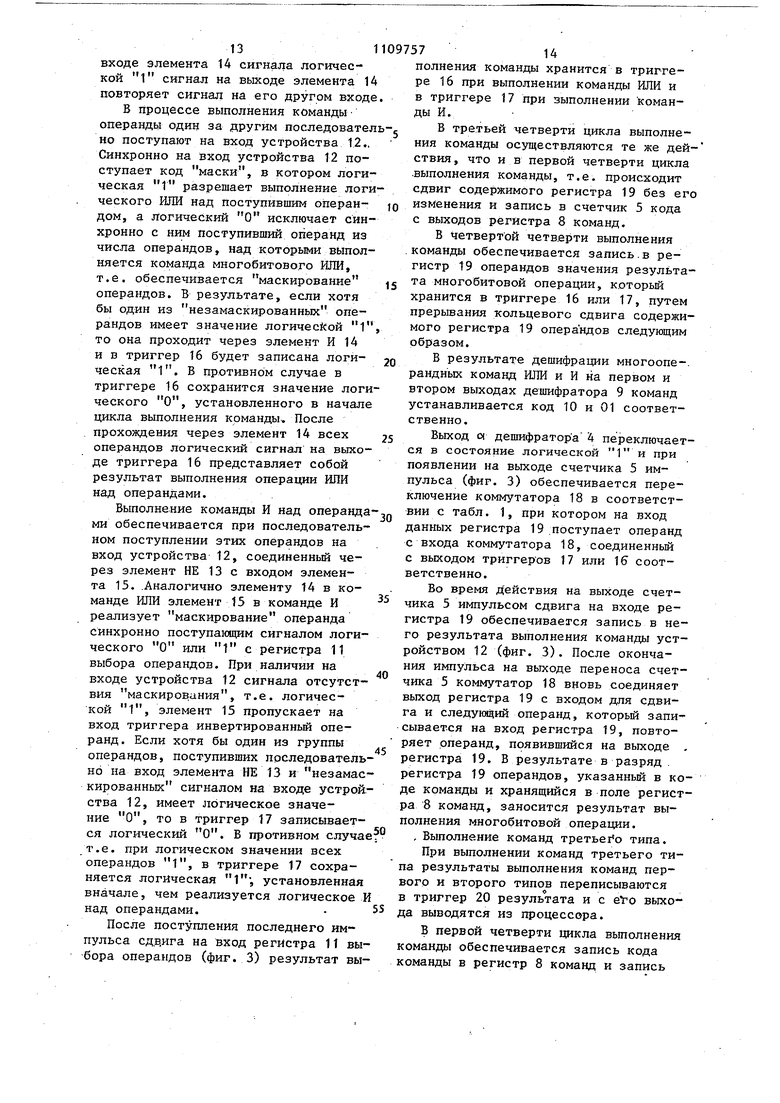

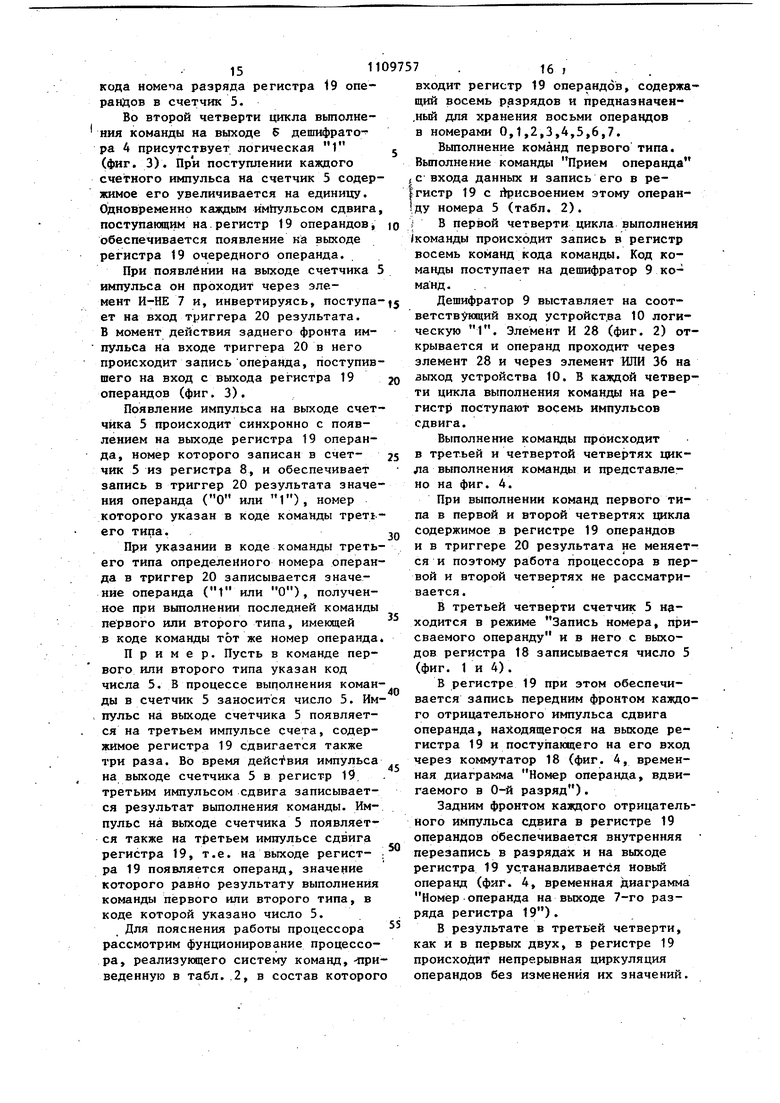

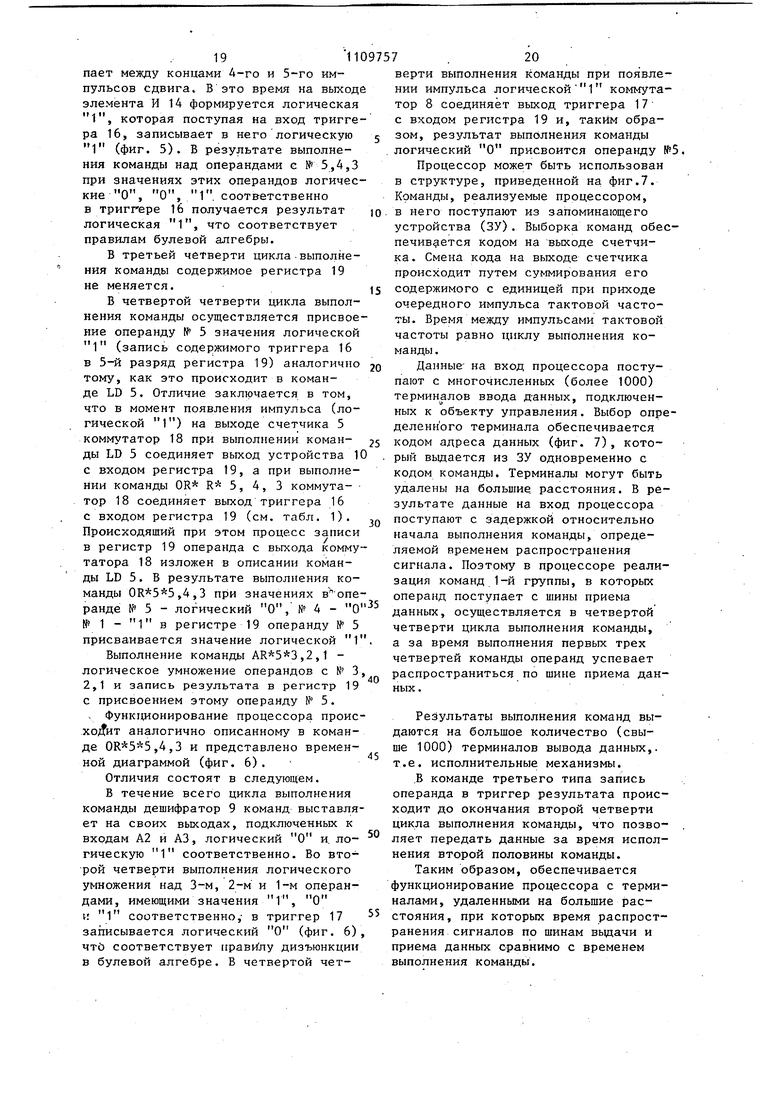

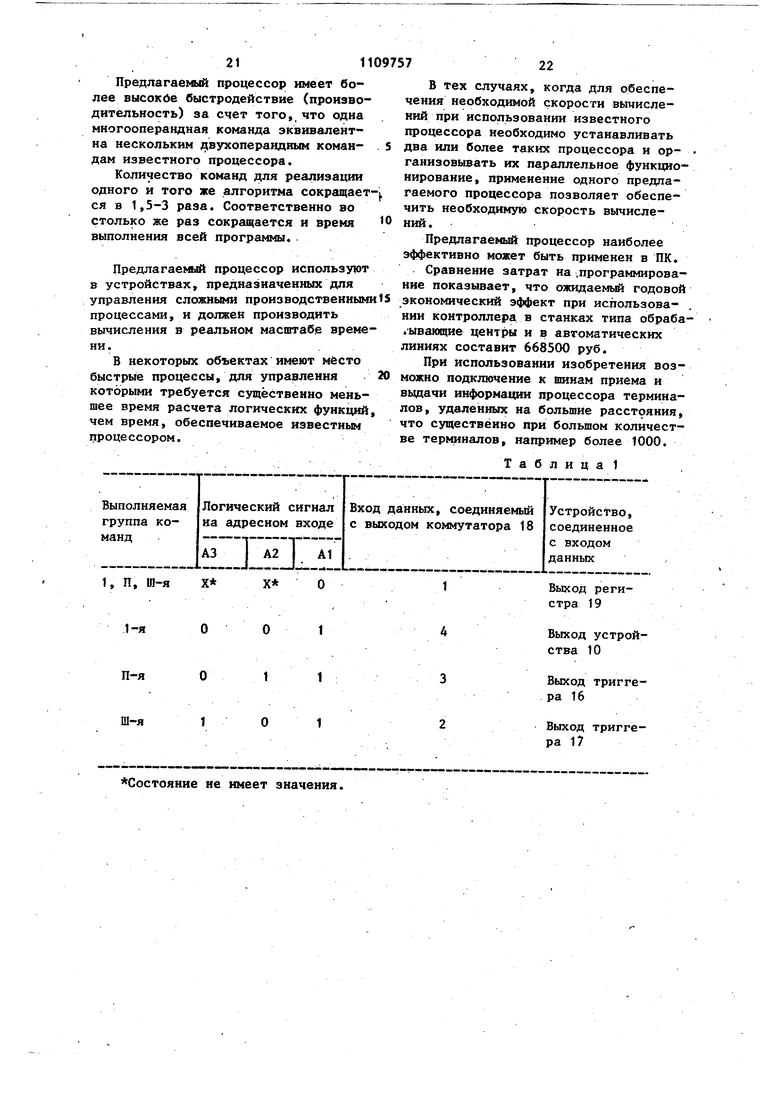

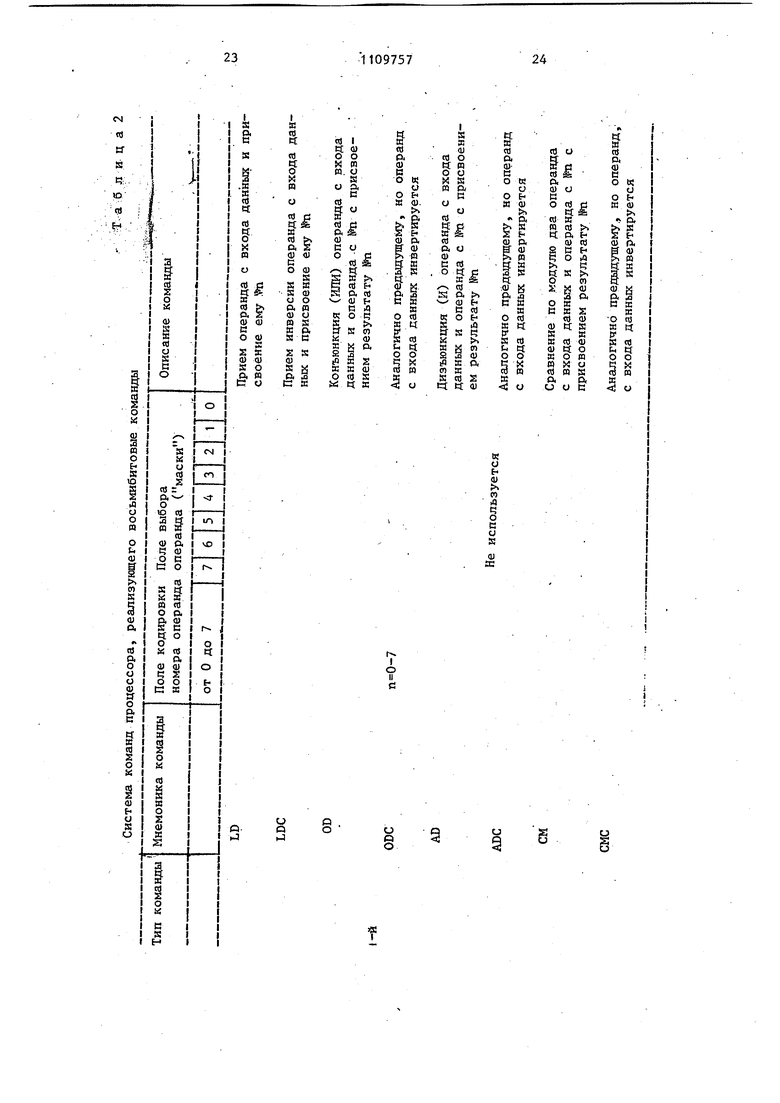

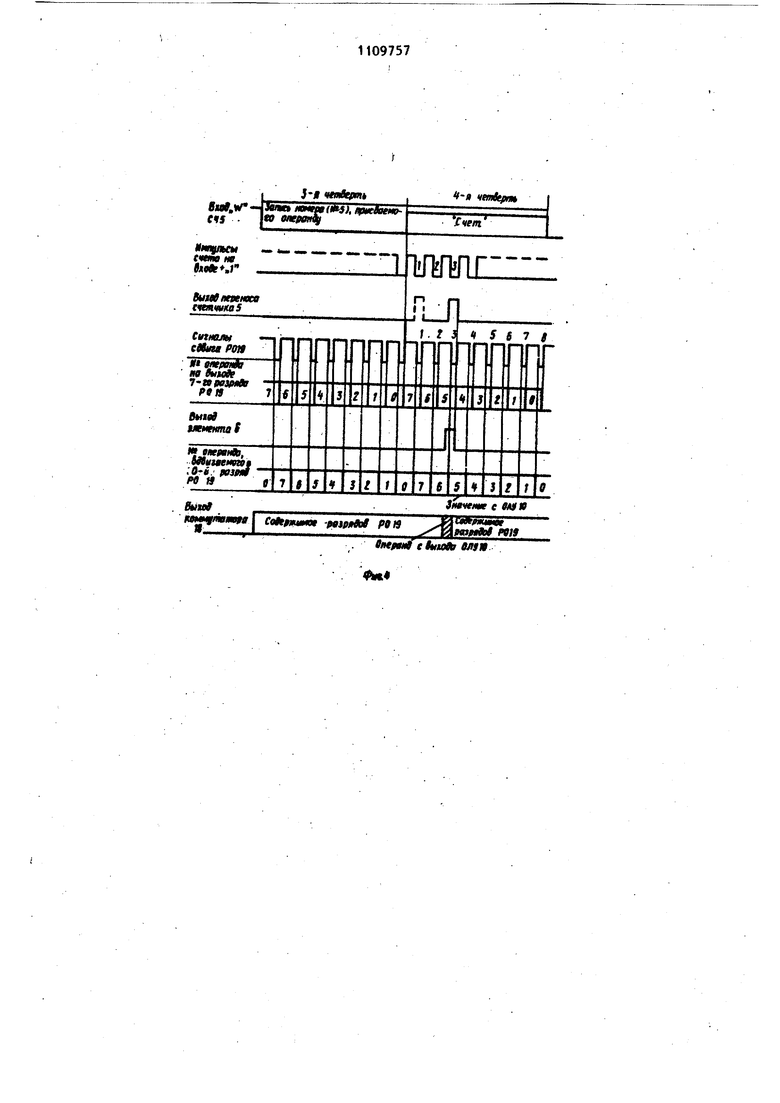

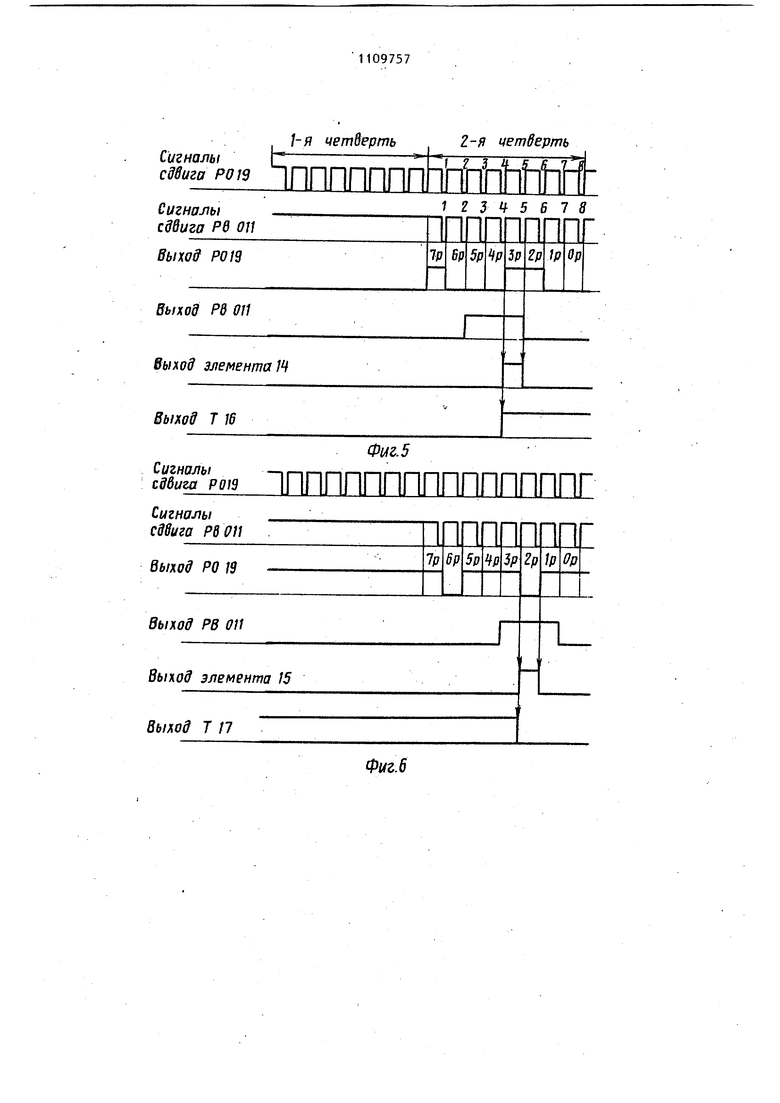

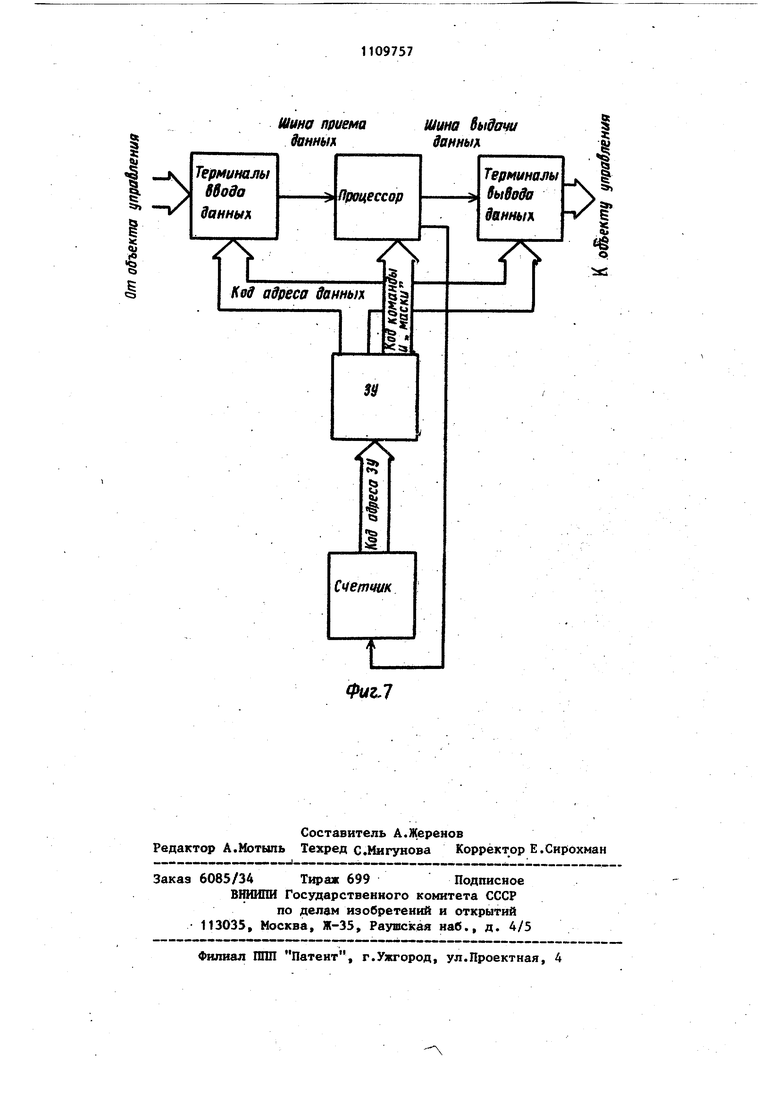

. Программирование микропроцессоров производится на так называемых машинных языках и доступно только специалистам по программированию. В условиях эксплуатации систем управления, использующих микропроцессоры, возникает необходимость изменять алгоритм работы объекта управления при отладке и модернизациях оборудования. a также осуществлять поиск неисправностей при отказах. Эта работа связа на с необходимостью изменять програм мы управления, что недоступно для специалистов, далеких от программирования, таких, как.электрики, технологи и т.п. Для того, чтобы дать возможность производственному персоналу осуществлять программирование, разрабатываются специальные проблемно-ориентированные языки. Они являются языками высокого уровня по отношению к.машинным языкам, ко торые используются непосредственно в микро-ЭВМ или микропроцессорах. Преобразование пр.ограмм на языках высокого уровня в программы на машинных языках осуществляется специальными программами-трансляторами. Применение трансляторов требует наличия дополнительных объемов памяти и дополнительного времени на выполнение совокупности машинных команд, эквивалентных одной команде проблемно-ориентированного языка. Поэтому недостатками систем управления, построенных на микропроцессорах и микро-ЭВМ, являются низкое быстродействие, а также увеличенные объемь электронного оборудования из-за увеличенной емкости запоминающих устройств. Сложность программирования на про лемно-ориентированных языках является также недостатком систем логического управления на микропроцессорах и микро-ЭВМ. Эти недостатки в значительной ст пени устранены в появившихся в после нее десятилетие электронных системах управления сложными производственными машинами, получивших название программируемые контролеры, использующих однобитовые логические процессоры. Наиболее близким по технической сущности к предлагаемому является процессор, содержащий генератор, уст ройство управления, регистр команд, логическое устройство, регистр результата. Генератор вьщает тактовые импульс в устройство управления, которое обеспечивает синхронизацию работы всего процессора. Код команды из регистра команд поступает в логическое утройство, которое обеспечивает непосредственное выполнение следующих инструкций (команд): прием данных. логическое И и логическое ИЛИ над двумя операндами, инверсию операндов в перечисленных действиях, запоминание операндов, выдачу операнда. По шине данных в логическое устройство поступает однобитовая входная информация. Результат вьтолнения каждой команды передается в регистр результата, из которого данные поступают в устройство вьздачи .. или в логическое устройство в качестве операнда. При решении логической задачи по управлению объектом часто необходимо выполнить логические операции над группой операндов, причем каждый из этих операндов сам является результатом выполнения другой логической операции. В известном процессоре в регистре результата возможно хранение только одного из этих операндов. При этом предполагается, что результаты вычислений помещаются в специальном внешнем запоминающем устройстве. При этом операнды вычисляются последовательно один за другим и пересылаются временно во внешнее запоминакндее устройство. В известном процессоре функции, например логическое И, выполняются только над двумя операндами. При необходимости вычислить эту функцию над несколькими, например восьмью операндами, они поочередно извлекаются из внешнего запоминающего устройства и умножаются в процессоре. Все умножение производится за семь команд с учетом того,что первый операнд находится в регистре результата С2 }. Недостатком известного процессора является невозможность выполнения логических операций над группой из операндов за один цикл выполнения ко|манды,. В результате время выполнения многооперандной логической операции над п операндами в (п-1) раз больше, чем двухоперандной. Кроме того, недостатком устройства является усложненное программирование из-за необходимости для реализации многооперандной функции использовать несколько команд. Цель изобретения - повьштение быстродействия при упрощении программиро-. вания. Поставленная цель достигается тем, что в процессор, содержащий генератор тактовых импульсов, устройстВО управления, включающее два счетчи ка, лешнфратор сигналов управления, элементы И, И-НЕ, причем счетньй вхо первого счетчика соединен с выходом генератора тактовых имйульсов, выход первого разряда первого счетчика сое динен с первым инф ормационным входом дешифратора сигналов управления и счетным входом второго, счетчика, выход второго разряда первого счетчика подключен к управляющему входу второго счетчика, выходы разрядов первого счетчика, начиная с третьег о соединены соответственно с информационными входами дешифратора сигналов управления, начиная с второго, первьй выход дешифратора сигналов управления подключен к управлякнцему входу регистра команд, второй выход - к управляющему входу регистра операндов, третий выход - к первому входу первого элемента И, четвертьй выход соединен с первым входом элемента И-НЕ, вторые входы первого элемента И и элемента И-НЕ соединены с выходом переноса второго счетчика, информационные входы которого соединены соответственно с выходами первой группы регистра команд, выход элемента И-НЕ соединен с синхронизирующим входом триггера результата, вход данных регистра команд является входом кода команды процессора, выходы второй группы регистра команд соединены соответственно с входами дешифратора команд, группа выходов которого соединена соответственно с управляющими входами устройства выполнения логических операций, первый информационный вход которого является входом приема данных процес сора, выход регистра операндов подключен к второму информационному вхо ду устройства выполнения логических операций и к информационному входу триггера результата,.выход которого является выходом процессора, введены регистр выбора операндов, коммутатор второй и третий элементы И,элемент Н и два Триггера,причем первый управляющий вход регистра выбора операндов соединен с пятым выходом дешифра тора сигналов управления, первьй выход которого соединен и вторым управ ляюп(им входом регистра выбора операн дов, информационные входы которого являются входами кода маски процессора, выход первого элемента И подключен к первому адресному входу ком мутатора, выход которого соединен с информационным входом регистра операндов, выход которого соединен с первБ1м .информационным входом коммутатора, с первым входом второго элемента И и с входом элемента НЕ, выход которого подключен к первому входу третьего элемента И, второй и третий информационные входы, коммутатора соединены соответственно с выходами первого и второго триггеров, четвертьй информационньй вход коммутатора подключен к выходу однобитового логического устройства, второй и третий . адресные входы коммутатора соединены соответственно с первым и вторым выходами дешифратора команд, третий выход которого подключен к третьему входу элемента И-НЕ, выход регистра выбора операндов соединен с его последним входом и с вторыми входами второго и третьего элементов И, выходы второго и третьего элементов И соединены соответственно с единичными и нулевыми входами второго и первого триггеров,-установочньй вход первого триггера является входом логической 1 процессора, установочньй вход второго триггера является входом логического О процессора, входы синхронизации первого и второго триггеров соединены с первым выходом дешифратора сигналов управления . Кроме того, устройство выполнения логических операций содержит элемент НЕ, десять элементов И, три элемента ИЛИ и два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, причем первьй информационньй вход устройства соединен с входом элемента НЕ, с первыми входами первых элементов ИЛИ, И, ИСКЛЮЧАЮЩЕЕ ИЛИ, с первым входом второго элемента И, второй информационньй вход устройства соединен с вторыми . входами перврго элемента ИЛИ, второго элемента И, первого элемента ИСЮБОЧАЮЩЕЕ ИЛИ и с первыми входами второго элемента ИЛИ, третьего элемента И, второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход элемента НЕ подключен к вторым входам второго элемента ИЛИ, третьего элемента И, второго 2(лемента ИСКПЮЧАЩЕЕ ИЛИ н к первому входу четвертого элемента И, выход первого элемента ЕПИ соединен с первь1м входом пятого элемента И, выход второго элемента Р1ПИ соединен с первым входом шестого элемента И, выход втоporo элемента И соединен с первым входом седьмого элемента И, выход tpeTberp элемента И соединен с первы входом восьмого элемента И, выход( первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ сое динен с первым входом девятого элемента }1, выход второго элемента ИСКЛЮЧАРЦЕЕ ИЛИ соединен с первым входом десятого элемента И, вторые входы первого, четвертого, пятого, шеетого, седьмого, восьмого, девятого и десятого элементов И подключены соответственно к управляющим входа:м устройства, выходы первого, четвертого, пятого, шестого, седьмого, восьмого, девятого и десятого элемен тов И подключены к соответствующим входам третьего элемента ИЛИ, выход которого является выходом устройства На фиг. 1 приведена схема процессора; на фиг. 2 - пример функциональ ной схема устройства выполнения логических операций; на фиг. 3 временная диаграмма сигналов управле ния; на фиг. 4 - временная диаграмма работы при записи результата выполнения команды в регистр операндов для процессора, именицего восьмиразрядньй регистр операндов; на фиг. 5 - временная диаграмма работы при выполнении команды логического сложения над операндами в 3,4 и 5-м разрядах регистра операндов для процессора, имекмцего восьмиразрядный регистр операндов; на фиг. 6 - временная диаграмма работы при выполнении команды логического умножения над операндами в 1, 2 и 3-м разрядах регистра операндов для процессора, имеющего восьмиразрядный регистр опе рандов; на фиг. 7 - пример структурной схемы программируемого контроллера (ПК) . Устройство содержит генератор 1 тактовых импульсов, устройство 2 управления, состоящее из счетчика 3 дешифратора 4 сигналов управления, счетчика 5, элемента И 6, элемента И-НЕ 7, регистр- 8 команд, дешифра тор 9 команд, устройство 10 выполнения логических операций, регистр 11 выбора операндов, однобитовое логиче кое устройство 12, содержащее элемент НЕ 13, элементы И 14 и 15, триг геры 16 и 17, коммутатор 18, регистр 19 операндов, триггер 20 результата, элемент НЕ 2 Г, элементы ИЛИ 22 и 23, элементы И 24 и 25, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 26. и 27, элементы И 28-35, элемент ИЛИ 36. Процессор реализует три типа команд. Первый тип. Прием операнда с входа данных в регистр операндов, логическое И, ИЛИ, неравнозначность между двумя операндами, один из которых хранится в регистре операндов, а второй поступает с входа приема данных. При этом Возможна инверсия операндов . Второй тип. Логическое И, ИЛИ над группой операндов, хранящихся в регистре операндов, причем группа операндов, над которой осуществляется логическая команда, может представлять собой как всю совокупность операндов, так и отдельные операнды по выбору. Третий тип. Запись любого операнда, хранящегося в регистре операндов, в триггер результата, с выхода которого результаты выполнения операций вьшодятся из логического процессора . Процессор работает следующим образом. Генератор 1 вьфабатывает импульсы, которые накапливаются счетчиком 3 Дешифратор 4 формирует сигналы, управляющие работой процессора. При включении в разрядах счетчиков 3 и 5 устанавл{юаются логические О сигналом Начальная установка. Выполнение любой команды начинается с записи в регистр 8 команд кода команды и в регистр 11 выбора операнда кода маски задним фронтом отрицательного импульса с первого выхода дешифратора 4 (фиг. 3). Одна часть разрядов кода, занесенного в регистр 8 команд, с выходов Хполе 1) поступает на входы дешифратора 9 команд. В зависимости от типа выполняемой команды дешифратор 9 формирует на выходах код, управляющий состоянием коммутатора 18 в соответствии с табл. 1. Коммутатор 18 постоянно находится в одном из четырех состояний, приведенных в табл. 1, и обеспечиваемом сигналами на его адресных входах. Вторая часть разрядов кода, занесенного в регистр 8 команд, с его выходов (поле 2) поступает на входы данных счетчика 5. В поле 2 регистра команд находится код, обозначающий номер разряда п-разрядного регистра 19 операндов, который в слу чае выполнения команды первого типа, обозначает.номер.разряда в регистре 19 операндов, над содержимым кото рого в качестве операнда осуществляется действие, предписанное командой и в которьй заносится результат выполнения команды; при выполнении команды второго типа обозначает номе разряда в регистре 19 операндов, в которьй заносится результат выполнения команды, и при выполнении кома ды третьего типа обозначает номер разряда в регистре 19 операндов, из которого значение операнда записывается в триггер 20 результата. Весь цикл вьшолнения любой, команды рассматривается по четвертям (фиг. 3). Счетчик 5 по время выполнения любой команды функционирует в двух режимах: Запись номера операнда и Счет. В первую и третью четверти команды в счетчике 5 осуществляется запись № операнда, установленного на входах данных; во вторую и четвертую четверти происходит счет импульса. Переключение режимов работы счетчика 5обеспечивается подачей на его вход сигнала с выхода счетчика 3, ло гическое значение которого сменяется четыре раза за время выполнения одной команды. При счете импульсов происходит суммирование кода, записа ного в счетчик 5, с единицей, в результате после каждого пришедшего им пульса код в счеТчике увеличивается на единицу до тех. пор, пока счетчик не заполнится единицами во всех разрядах. При этом на выходе переноса счетчика 5 появится импульс. Наприме если счетчик 5 трехразрядньй и в нег записан номер операнда пять (101), т после прохождения двух импульсов в нем будет код(111) и появится импульс на. выходе переноса. В течение каждой четверти выполнения команды на регистр 19 операндов с второго вы хода дешифратора 4 сигналов управления поступает п импульсов сдвига. Причем во второй и четвертой четвертях они синхронны с импульсами, поступающими на счетный вход счетчика 5. В результате в конце каждой, четверти в нулевом разряде находится 0-й операнд, в первом разряде - 1-й операнд и в (п-1)-м разряде - (п-1)операнд. Далее работа процессора рассматривается при выполнении им кажд.ого типа команд отдельно. Выполнение команд первого типа. Код на выходах дешифратора 9 обес-. печивает настройку устройства 10 на выполнение одной из команд первого типа в соответствии с кодом команды, находящимся в регистре 8 команд. Устройство 10 выполняет эту команду над двумя операндами, поступающими на его входы. Первый операнд поступает по входу приема данных, а вТорой - с выхода регистра 19 операндов. Устройство 10 представляет собой Совокупность, комбинационных схем и может иметь разную структуру в зависимости от конкретной системы команд и элементной базы, на которой реализовано устройство. Выбор второго операнда из регистра 19 операндов и запись в него результата выполнения команды происходит следующим образом. Поступающие на вход регистра 19 импульсы с выхода дешифратора 4 обес печивают непрерывньй сдвиг содержимого регистра 19. В первой, второй и третьей четвертях цикла выполнения команды с выхода а дешифратора 4 на вход элемента И 6 поступает сигнал логического О, которьй проходит на выход элемента 6 и далее на адресньй вход коммутатора 18. В результате обеспечивается соединение входа коммутатора 18 с его выходом. При этом происходит подключение выхода регистра 19 к его входу для сдвига, чем обеспечивается неизменность содержимого регистра 19 в процессе сдвига. В четвертой четверти цикла выполнения команды результат операции помещается в тот разряд регистра 19 операндов, из которого операнд берется на вход устройства 10 для выполнения команды. Это обеспечивается путем прерывания кольцевого сдвига содержимого регистра 19 операндов следукщим образом. Выход дешифратора 4, переключается в состояние логической 1 и при появлении на выходе счетчика 5 импульса (фиг. 3) обеспечивается переключение коммутатора Т8 в соответствии с табл. 1, при котором на вход устойства 10, соединенньй с выходом регистра 19 операндов, поступает опеанд, содержащийся в выбираемом разяде регистра 19, а на вход данных регистра 19 поступает операнд с выхо да устройства 10, который представляет собой результат выполнения команды. Во время действия импульса на выходе переноса счетчика 5 импуль сом сдвига на управляющем входе регистра 19 обеспечивается запись в не го результата вьшолнения команды в устройстве 10 (фиг. 2). После окончания импульса на выходе переноса счетчика 5 коммутатор 18 вновь соединяет через свой вход выход регистра 19 с входом для сдвига. И следующий операнд, который записывается на вход регистра 19, повторит операнд, появившийся на выходе ре.гистра 19. В результате в разряд регистра 19 операндов, указанный в коде команды и хранящийся в регистра 8 команд, заносится результат логической операции, код которой хранится в поле 1 регистра 8 команд. Остальные операнды переписываются в ходе выполнения команды с выхода регистра 19 на его вход и не меняют своих значений. Выполнение команд второго типа. В начале цикла вьтолнения команды (фиг. 3) обеспечивается запись кода команды в регистр 8 и кода мас ки в регистр 11 выбора операнда сиг налом с выхода дешифратора 4. Этим же сигналом в триггеры 16 и 17 заносятся логический О и логическая соответственно. Сигналом на входе счетчика 5 осуществляется запись номера регистра результата в счетчик 5 В первой четверти цикла выполнения команды с выхода дешифратора 4 на вход элемента 6 поступает логический , который передается на вход коммутатора 18. Коммутатор 18 обеспечивает соединение своего входа с выходом (см. табл. 1). На вход регистра 19 операндов с выхода дешифратора 4 поступает п импульсов сдви га (фиг. 3). В результате операнды в течение первой четверти выполнения команды в регистре 19 непрерывно сдвигаются, не изменяясь. Во второй ч етверти цикла выполнения команды с третьего выхода дешифратора 4 на регистр 11 выбора опера дов поступает п импульсов сдвига син хронно с импульсами сдвига на входе управления регистра 19 операндов, соединенном с выходом дешифратора 4. В процессе сдвига логические сигналы с выходов регистров 11 и 19 поступаю на входы устройства 12, где и осуществляется выполнение мнбгобитовых команд. Выполнение многобитовых команд логическое И и логическое ИЛИ может осуществляться как над всей группой операндов, так и над меньшим количеством операндов. Конкретные операнды, над которыми обеспечивается выполнение логической операции, находятся . в регистре 19 операндов и определяются кодом маски. Код, находящийся в регистре 11 выбора операндов, обеспечивает маскирование тех операндов, которые должны игнорироваться при выполнении многобитовых команд следующим образом. Логическая t в определенном разряде кода маски обозначает необходимость выполнения логической операции над операндом, хранящимся в соответствующем разряде регистра 19. Логический О в определенном разряде кода маски обозначает исключение операнда, хранящегося в соответствующем разряде регистра 19, из состава операндов, над которыми осуществляется логическая операция. Например, при восьми разрядах и коде 01101001 в регистре 11 логическая операция выполняется над операндами, хранящимися, в 0-м, 3-м, 5-м, 6-м разрядах регистра 19. Устройство 12 обеспечивает выполнение логического И и логического ИЛИ над группой операндов следующим образом. Выполнение команды ИЛИ над операндами обеспечивается при последовательном поступлении этих операндов на вход устройства 12, соединенный с входом элемента 14, и через элемент 14 на вход триггера 16. Триггер 16 устанавливается в состояние логической 1 при поступлении на его вход логической 1 с выхода элемента 14. На вход элемента 14 синхронно поступает сигнал из регистра 11, определяющий, должна выполниться или нет команда ИЛИ над операндом, поступившим на вход устройства 12, соединенный с входом элемента 14. В случае наличия .на входе элемента 14 сигнала логического О этот сигнал проходит через элемент 14 на вход триггера 16, при этом триггер 16 не меняет своего начального состояния при любом значении операнда на д{5угом входе элемента 14. При наличии на одном входе элемента 14 сигнала логической 1 сигнал на выходе элемента 14 повторяет сигнал на его другом входе В процессе выполнения командыоперанды один за другим последовател но поступают на вход устройства 12.. Синхронно на вход устройства 12 поступает код маски, в котором логическая 1 разрешает выполнение логи ческого ШШ над поступившим операндом, а Логический О исключает синхронно с ним поступивший операнд из числа операндов, над которыми выполняется команда многобитового ИЛИ, т.е. обеспечивается маскирование операндов. Б результате, если хотя бы один из незамаскированных операндов имеет значение логической 1 то она проходит через элемент И 14 и в триггер 16 будет записана логическая 1. В противном случае в триггере 16 сохранится значение логи ческого О, установленного в начале цикла выполнения команды. После прохождения через элемент 14 всех операндов логический сигнал на выходе триггера 16 представляет собой результат выполнения операции ИЛИ над операндами. Выполнение команды И над операнда ми обеспечивается при последовательном поступлении этих операндов на вход устройства 12, соединенньй через элемент НЕ 13 с входом элемента 15. .Аналогично элементу 14 в команде ИЛИ элемент 15 в команде И реализует маскирование операнда синхронно поступающим сигналом логического О или 1 с регистра 11 выбора операндов. При наличии на входе устройства 12 сигнала отсутствия маскирования, т.е. логической 1, элемент 15 пропускает на вход триггера инвертированный операнд. Если хотя бы один из группы операндов, поступивших последователь но на вход элемента НЕ 13 и незамас кированных сигналом на входе устрой ства 12, имеет логическое значение О, то в триггер 17 записывается логический О. В противном случа т.е. при логическом значении всех операндов 1, в триггере 17 сохраняется логическая установленная вначале, чем реализуется логическое над операндами. После поступления последнего импульса сддига на вход регистра 11 вы бора операндов (фиг. 3) результат вы полнения команды хранится в триггере 16 при выполнении команды ИЛИ и в триггере 17 при выполнении команды И. Б третьей четверти цикла выполнения команды осуществляются те же действия, что ив первой четверти цикла .выполнения команды, т.е. происходит сдвиг содержимого регистра 19 без его изменения и запись в счетчик 5 кода с выходов регистра 8 команд. В четвертой четверти выполнения команды обеспечивается запись.в регистр 19 операндов значения результата многобитовой операции, к.оторьй хранится в триггере 16 или 17, путем прерывания кольцевого сдвига содержимого регистра 19 операндов следующим образом. В результате дешифрации многоопе-. рандных команд ИЛИ и И на первом и втором выходах дешифратора 9 команд устанавливается код 10 и 01 соответственно. Выход 01 дешифратора 4 переключается в состояние логической 1 и при появлении на выходе счетчика 5 импульса (фиг. 3) обеспечивается переключение коммутатора 18 в соответствии с табл. 1, при котором на вход данных регистра 19.поступает операнд с входа коммутатора 18, соединенньй с выходом триггеров 17 или 16 соответственно. Во время Действия на выходе счетчика 5 импульсом сдвига на входе регистра 19 обеспечивается запись в него результата выполнения команды устройством 12 (фиг. 3). После окончания импульса на выходе переноса счетчика 5 коммутатор 18 вновь соединяет выход регистра 19 с входом для сдвига и следунядий операнд, которьй записывается на вход регистра 19, повторяет операнд, появившийся на выходе , регистра 19. В результате в разряд . регистра 19 операндов, указанньй в коде команды и хранящийся в поле регистра 8 команд, заносится результат выполнения многобитовой операции. , Выполнение команд третьех о типа. При выполнении команд третьего типа результаты выполнения команд первого и второго типов переписываются в триггер 20 результата и с его выхоа выводятся из процессора. В первой четверти цикла вьтолнения команды обеспечивается запись кода оманды в регистр 8 команд и запись кода номепа разряда регистра 19 операндов в счетчик 5. Во второй четверти цикла вьтолнения команды на выходе 5 дешифратора А присутствует логическая 1 (фиг. 3). При поступлении каждого счетного импульса на счетчик 5 содер жимое его увеличивается на единицу. Одновременно каждым имйульсом сдвига поступакяцим на.регистр 19 операндовj обеспечивается появление на выходе регистра 19 очередного операнда. При появлении на выходе счетчика импульса он проходит через элемент И-НЕ 7 и, инвертируясь, поступа ет на вход триггера 20 результата. В момент действия заднего фронта импульса на входе триггера 20 в него происходит запись операнда, поступив шего на вход с выхода регистра 19 операндов (фиг. 3). Появление импульса на выходе счет чика 5 происходит синхронно с появлением на выходе регистра 19 операнда, номер которого записан в счетчик 5 из регистра 8, и обеспечивает запись в триггер 20 результата значе ния операнда (О или 1), номер которого указан в коде команды треть его типа. При указании в коде команды треть его типа определенного номера операн да в триггер 20 записывается значение операнда (1 или О), полученное при выполнении последней команды первого или второго типа, имеющей в коде команды тот же номер операнда Пример. Пусть в команде первого или второго типа указан код числа 5. В процессе выполнения коман ды в счетчик 5 заносится число 5. Им пульс на выходе счетчика 5 появляется на третьем импульсе счета, содержимое регистра 19 сдвигается также три раза. Во время дейст вия импульса на выходе счетчика 5 в регистр 19 третьим импульсом сдвига записывается результат выполнения команды. Импульс на выходе счетчика 5 появляется также на третьем импульсе сдвига регистра 19, т.е. на выходе регистра 19 появляется операнд, значение которого равно результату выполнения команды первого или второго типа, в коде которой указано число 5. Для пояснения работы процессора рассмотрим фунционирование процессора, реализующего систему команд, -при веденную в табл. .2, в состав которог входит регистр 19 операндов, содержащий восемь разрядов и предназначен,ньй для хранения восьми операндов в номерами 0,1,2,3,4,5,6,7. Выполнение команд первого типа. Вьтолнекие команды Прием операнда с входа данных и запись его в регистр 19 с присвоением этому операнду номера 5 (табл. 2). ; В первой четверти цикла выполнения команды происходит запись в регистр восемь команд кода команды. Код команды поступает на дешифратор 9 команд. . , Дешифратор 9 выставляет на соответствующий вход устройст.ва 10 логическую 1. Элемент И 28 (фиг. 2) открывается и операнд проходит через злемент 28 и через элемент ИЛИ 36 на выход устройства 10. В каждой четверти цикла выполнения команды на регистр поступают восемь импульсов сдвига. Выполнение команды происходит в третьей и четвертой четвертях цикла выполнения команды и представлено на фиг. 4. При выполнении команд первого типа в первой и второй четвертях цикла содержимое в регистре 19 операндов и в триггере 20 результата не меняется и поэтому работа процессора в первой и второй четвертях не рассматривается. В третьей четверти счетчик 5 находится в режиме Запись номера, присваемого операнду и в него с выходов регистра 18 записывается число 5 (фиг. 1 и 4). В регистре 19 при этом обеспечивается запись передним фронтом каждого отрицательного импульса сдвига операнда, находящегося на выходе регистра 19 и поступающего на его вход через коммутатор 18 (фиг. 4, временная диаграмма Номер операнда, вдвигаемого в 0-й разряд). Задним фронтом каждого отрицательного импульса сдвига в регистре 19 операндов обеспечивается внутренняя перезапись в разрядах и на выходе регистра 19 устанавливается новый операнд (фиг. 4, временная диаграмма Номер операнда на выходе 7-го разряда регистра 19). В результате в третьей четверти, как и в первых двух, в регистре 19 происходит непрерывная циркуляция операндов без изменения их значений. Четвертая четверь цикла выполнения команды начинается по фронту импульса на выходе счетчика, 5. Поступающие на вход счетчика 5 импульсы начинают им пересчитываться в момент прохождения третьего импуль са на выходе переноса счетчика 5, на время действия импульса появляется логическая 1 (фиг. 4), когда во всех его трех разрядах устанавливают ся 1. Коммутатор 18 переключается положительным импульсом на выходе элемента 6 в соответствии с табл, 1, и на вход регистра 19, соединенный с выходом коммутатора 18, поступает операнд с входа приема данных через элементы 28 и 36 (фиг. 2) и коммутатор 18 (фиг. 4 временная диаграмма Выход коммутатора 18). Передним фронтом третьего отри цательного импульса в регистр 19 про исходит запись операнда с входа приема данных (фиг. 4). По окончании положительного импульса на выходе элемента 6 коммутатор 18 снова переключается и коммутирует между собой выход и вход регистра 19 операндов. Процесс сдвига в регистре 19 продолжается так же, как он осуществлялся до появления логической 1 на выходе элемента 6, Выполнение остальных команд перво го типа отличается от описанного выполнения команды лишь тем, что дешифратор 9 устанавливает логическую 1 на входе, соответствуклцем выполняемо команде. При этом эти команды реализуются в устройстве 10 и операндырезультаты проходят не через элемент И 28, а через тот элемент И, на вход которого поступает логическая При выполнении команд, в которых указан другой номер операнда-результата, импульс на выходе элемента 6 появляется в момент прохождения друг го по счету,импульса сдвига. Например, при выполнений команды OD 7 импульс на выходе элемента 6 появляется при прохождении импульса, обозначенного единицей, и в регистр 19 заносится операнд-результат с номером 7 (фиг, 4, временные диаграммы Выход переноса счетчика 5 и Номер операнда, вдвигаемого в 0-й разряд регистра 19). В момен-т действия импульса на выходе элемента 6 на второй вход устройства 10 поступает операнд с номером 7 (фиг. 4, временная диаграмма Номер операнда на выходе 7-го разряда регистра 19), а на первый вход устройства 10 - опе ранд с входа приема данных. Поэтому операнд, записываемый в регистр 19, является результатом логического ело-. жения операнда с входа приема данных и операнда с № 7, находящегося на выходе регистра 19. Выполнение команд второго типа. Выполнение команды Логическое сложение операндов с номерами 5,4,3 и запись результата в регистр 19 с присвоением этому операнду номера 5. В начале цикла выполнения команды в регистры 19 операндов и 11 выбора, операндов записывается код команды и восьмиразрядньй код маски 5,4,3 (00111000) соответственно, в счетчик 5 обеспечивается запись числа 5 и триггер 16 устанавливается в О. Дешифратор 9 команд в течение всего цикла выполнения команды выставляет на своих выходах, подключённых к входам коммутатора, логическую.l и логический О соответственно. Во второй четверти цикла выполнения коман-, ды в триггере 16 формируется результат логической операции ИЛИ над операндами № 5,4,3,,при этом содержимое регистра 19 не меняется. Рассмотрим это на примере, представленном на временной диаграмме Выход Р019 (фиг. 5), когда в регистре 19 операнды имеют следующие значения: операнд № 7 - логическую операнд № 6 - операнд № 5 - операнд № 4 - операнд № 3 - операнд № 2 - операнд № 1 - операнд № О - О. С начала второй четверти цикла выполнения команды и до окончания импульса сдвига на выхоце регистра 19 присутствует сигнал логического О (фиг. 5, временная диаграмма Выход Р019.). В это время на выходе регистра 11 выбора операндов присутствует сигнал логического О (фиг. 5, временная диаграмма Выход РВ 011). В результате на обоих входах элемента И 14 присутствует сигнал логического О, которьй с его выхода передается на вход триггера 16, которьй не меняет своего состояния. Между концами второго и пятого импульсов сдвига на выходе регистра 11 присутствует логическая 1, которая открывает элемент И 14 по одному входу. На второй вход элемента И 14 с выхода регистра 19 логическая 1 постулает между концами А-го и 5-го импульсов сдвига. В это время на выход элемента И 14 формируется логическая 1, которая поступая на вход тригге ра 16, записывает в него логическую 1 (фиг. 5). В результате выполнения команды над операндами с № 5,4,3 при значениях этих операндов логичес кие О, О, 1. соответственно в триггере 16 получается результат логическая 1, что соответствует правилам булевой алгебры. В третьей четверти цикла-выполнения команды содержимое регистра 19 не меняется. В четвертой четверти цикла выполнения команды осуществляется присвое ние операнду № 5 значения логической 1 (запись содержимого триггера 16 в 5-й разряд регистра 19) аналогично тому, как это происходит в команде LD 5. Отличие заключается в том, что в момент появления импульса (логической 1) на выходе счетчика 5 коммутатор 18 при выполнении команды LD 5 соединяет выход устройства 1 с входом регистра 19, а при выполнении команды OR R 5, 4, 3 коммутатор 18 соединяет выход триггера 16 с входом регистра 19 (см. табл. 1). Происходящий при этом процесс записи в регистр 19 операнда с выхода комму татора 18 изложен в описании команды LD 5. В результате выполнения команды ,4,3 при значениях ранде № 5 - логический О, № 4 - 0 № 1 - 1 в регистре 19 операнду № 5 присваивается значение логической 1 Выполнение команды ,2,1 логическое умножение операндов с № 3 2,1 и запись результата в регистр 19 с присвоением этому операнду № 5. Функционирование процессора проис аналогично описанному в команде ,4,3 и представлено временной диаграммой (фиг. 6). Отличия состоят в следующем. В течение всего цикла выполнения команды дешифратор 9 команд выставля ет на своих выходах, подключенных к входам А2 и A3, логический О и. логическую 1 соответственно. Во второй четверти выполнения логического умножения над 3-м, 2-м и 1-м операндами, имеющими значения 1, О и 1 соответствен ю,- в триггер 17 записывается логический О (фиг. 6) что соответствует иравилу дизъюнкции в булевой алгебре. В четвертой четверти выполнения команды при появлении импульса логической 1 коммутатор В соединяет выход триггера 17 с входом регистра 19 и, таким образом, результат выполнения команды логический О присвоится операнду №5. Процессор может быть использован в структуре, приведенной на фиг.7. Команды, реализуемые процессором, в него поступают из запоминающего устройства (ЗУ). Выборка команд обеспечивается кодом на выходе счетчика. Смена кода на выходе счетчика происходит путем суммирования его содержимого с единицей при приходе очередного импульса тактовой частоты. Время между импульсами тактовой частоты равно циклу выполнения команды . Данные на вход процессора поступают с многочисленных (более 1000) терминалов ввода д-анных, подключенных к объекту управления. Выбор определенного терминала обеспечивается кодом адреса данных (фиг. 7), который выдается из ЗУ одновременно с кодом команды. Терминалы могут быть удалены на большие расстояния. В результате данные на вход процессора поступают с задержкой относительно начала выполнения команды, определяемой временем распространения сигнала. Поэтому в процессоре реализация команд 1-й группы, в которых операнд поступает с шины приема данных, осуществляется в четвертой четверти цикла выполнения команды, а за время выполнения первых; трех четвертей команды операнд успевает распространиться по шине приема данных. Результаты выполнения команд выдаются на большое количество (свыше 1000) терминалов вывода данных,, т.е. исполнительные механизмы. ,В команде третьего типа запись операнда в триггер результата происходит до окончания второй четверти цикла выполнения команды, что позволяет передать данные за время исполнения второй половины команды. Таким образом, обеспечивается функционирование процессора с терминалами, удаленными на большие расстояния, при которых время распространения сигналов по шинам вьщачи и приема данных сравнимо с временем выполнения команды. Предлагаемый процессор имеет более высокие быстродействие (производительность) за счет того,, что одиа многооперандная команда эквивалентна нескольким ;(вухоперандным командам известного процессора. Количество команд для реализации одного и того же алгоритма сокращает ся в 1,5-3 раза. Соответственно во столько же раз сокращается и время выполнения всей программы. Предлагаемый процессор используют в устройствах, предназначенных для управления сложными производственным процессами, и должен производить вычисления в реальном масштабе време ни. В некоторых объектах имеют место быстрые процессы, для управления которыми требуется существенно меньшее время расчета логических функций чем время, обеспечиваемое известным процессором.

Состояние не имеет значения.

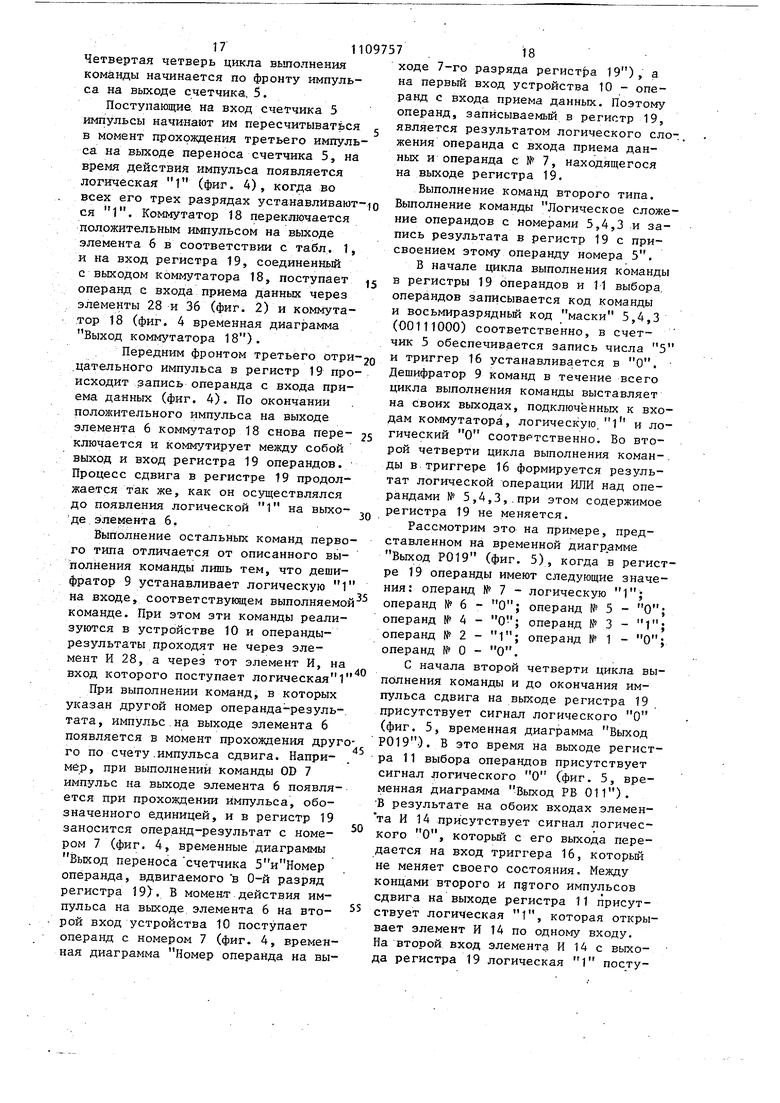

Таблица 1 В тех случаях, когда для обеспечения необходимой скорости вычислений при использовании известного процессора необходимо устанавливать два или более таких процессора и организовывать их параллельное функционирование, применение одного предлагаемого процессора позволяет обеспечить необходимую скорость вычислений. Предлагаемый процессор наиболее эффективно может быть применен в ПК. Сравнение затрат на .программирование показывает, что ожидаемый годовой экономический эффект при использовании контроллера в станках типа обраба .ывакяцие центры и в автоматических линиях составит 668500 руб. При Использовании изобретения возможно подключение к шинам приема и выдачи информации процессора терминалов, удаленных на большие расстояния, что существенно при большом количестве терьшналов, например более 1000.

CN

n)

a s,

Ч:. Ш

«B

.:

iJ

§

о

Фиг.1

29

гг

У1

31

гц

35

п

п

35

Фиг.г

Вы}10д1МУЧ, сигнал записи ,

ВРК8;Т1В,ТП РВОПL

Jk

Гц - UUKJ7 Выполнения команды

Фиг. 3

f,tp,M род хЙЙ5йаГ%/у

Знвченж e Мв

OMfgHt е ЛааЛг MtH W4

1-я четверть

4nnnnnnnHi1ihlili1iH|c sS ms Т ТПГ1ПГ1ПГ1Г1ПЛГ1ПППГ

2-я цетверть

Ф1лг.5

Фиг.6

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Микропроцессорные комплекты интегральных схем | |||

| Состав и структура | |||

| Справочник | |||

| М., Радио и связь, 1982 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Патент CUIA № 4153942, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Дверной замок, автоматически запирающийся на ригель, удерживаемый в крайних своих положениях помощью серии парных, симметрично расположенных цугальт | 1914 |

|

SU1979A1 |

Авторы

Даты

1984-08-23—Публикация

1983-04-08—Подача