11

Изобретение отиоситчл к вычис:лигелъной технике н может использовано для контроля достижения реверсивным счетчиком заданного кодового состояния в цифровых измерительных и вычислительных системах, в частности при построении

реверсивных счетчиков с управляемым коэффициентом пересчета.

Известно устройство контроля, содержащее счетчик, мультиплексор, триггер, инвертор и элемент совпадения 1 1.

Недостатком устройства является относительно низкая точность контроля ,

Известно также устройство контроля, содержащее входную шину, счетчик, мультиплексор, элемент задержки, элемент НЕ, триггер и элемент И первый и второй входы которого соединены соответственно с выходом элемента НЕ и с выходом элемента задержки, входы которых соединены с выходом мультиплексора, управляющие и информационные входы которого соединены соответственно с шинами управления и с выходами счетчика, вход сложения которого соединен с входной шиной и с входом установки в 1, триггера, вход установки в О которого соединен с выходом элемента И 2}

Недостатком известного устройств является ограниченность его функциональных возможностей.

Цель изобретения - расширение функциональных возможностей устройства контроля за счет возможности точного определения моментов равенства нулю или единице выходных сигналов заданного количества разрядов реверсивного счетчика в режимах прямого и обратного счета соответственно .

Для достижения поставленной цели в устройство контроля, содержащее первую входную шину, счетчик, мультиплексор, элемент задержки, первый элемент НЕ, первый триггер и первый элемент И, первый и второй входы которого соединены соответственно с выходом первого элемента НЕ и с выходом элемента задержки, входы которых соединены с выходом мультиплексора, управляющие и информационные входы которого соединены соответственно с шинами управления и с выходами счетчика, вход сложения

чдп91

KOToiHirc) соединен с iiepFioii нходпой iijHiioii, ппс/Ниы гггорая входная шина, второй и TpcTini элементы И, элемент RlH, злгмонт И,1И-НК, второй и тре, Tiifi -чломонты III- и второй трипер, рход установки в О которого соединен с входом установки в О первого триггСрл и с выходом з;гемента ИЛИ, псрЕзый и второй входы которого со)Q единены соответстве 1но. с первыми входами второго и третьего элементов И и соединены соответственно с ;-ходами второго и третьего элементов HR, входы которых соединены со ответственно с первой и второй входными шинами, последняя из которых соединена с входом вычитания счетчика, входы элемента ИЛИ-НЕ соединены соответственно с выходом первого элемента НЕ и с выходом элемента задержки, выходы первого элемента И и элемента ИЛИ-НЕ соединены соответственно с вторыми входами второго и третьего элементов И, выходы ко2. торых Соединены соответственно с входами установки в 1 первого и второго триггеров.

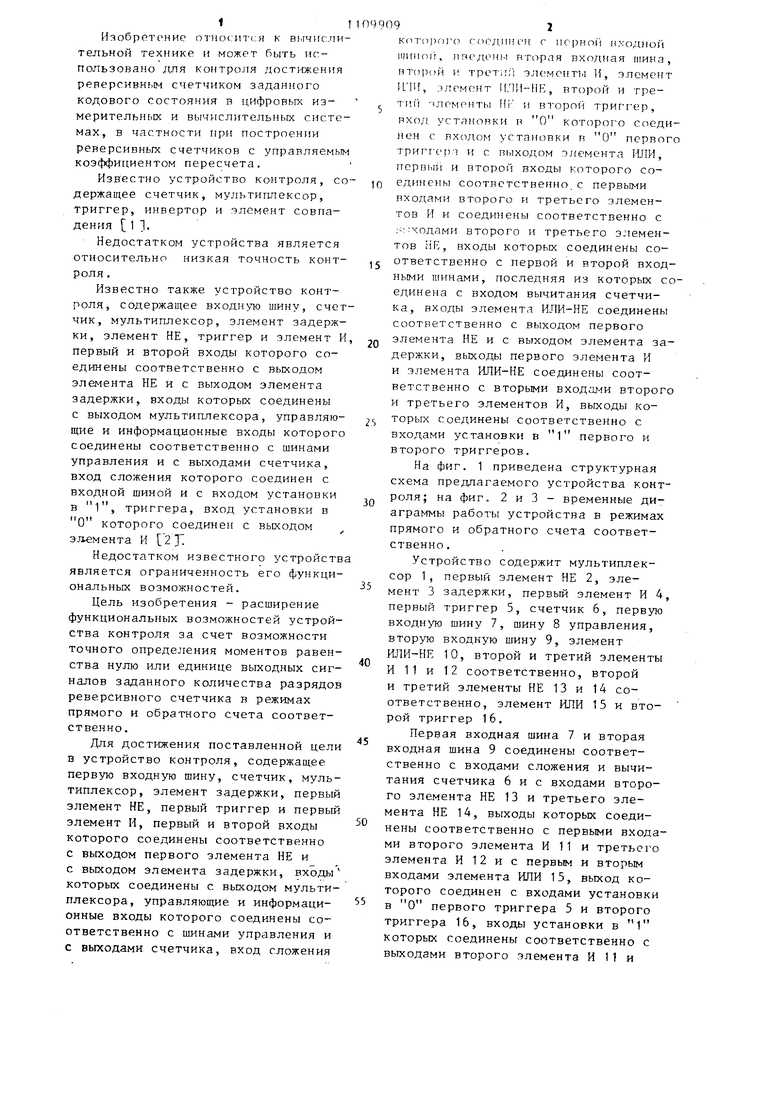

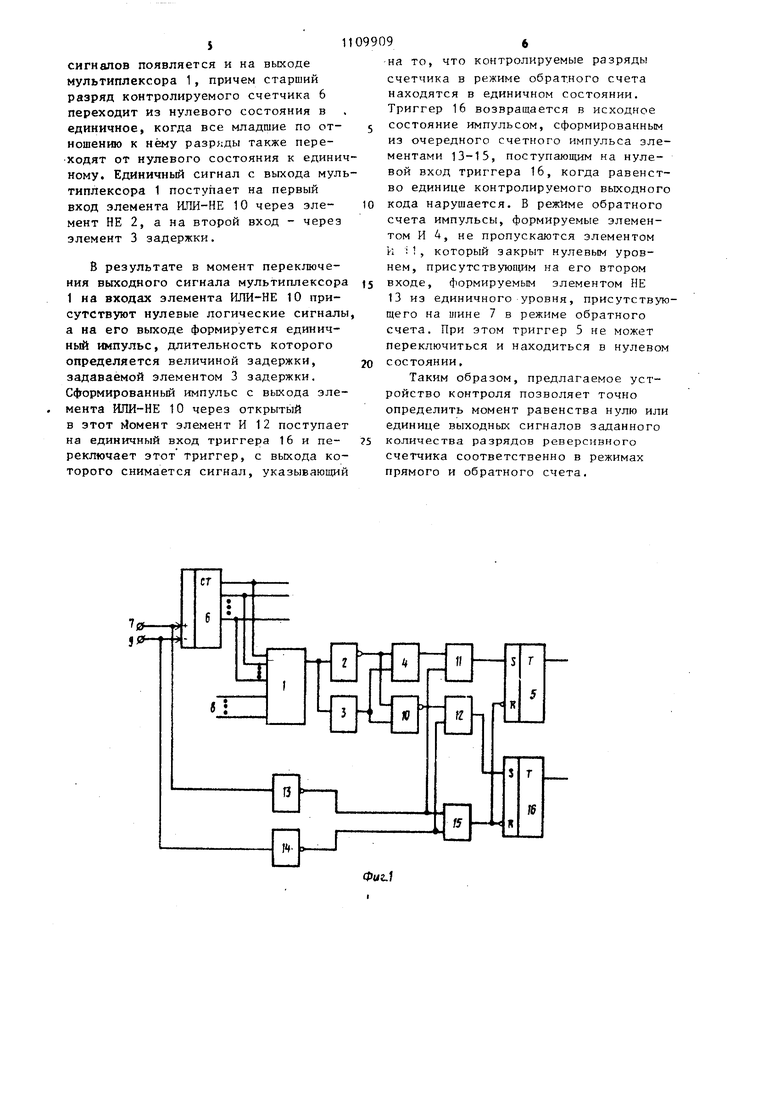

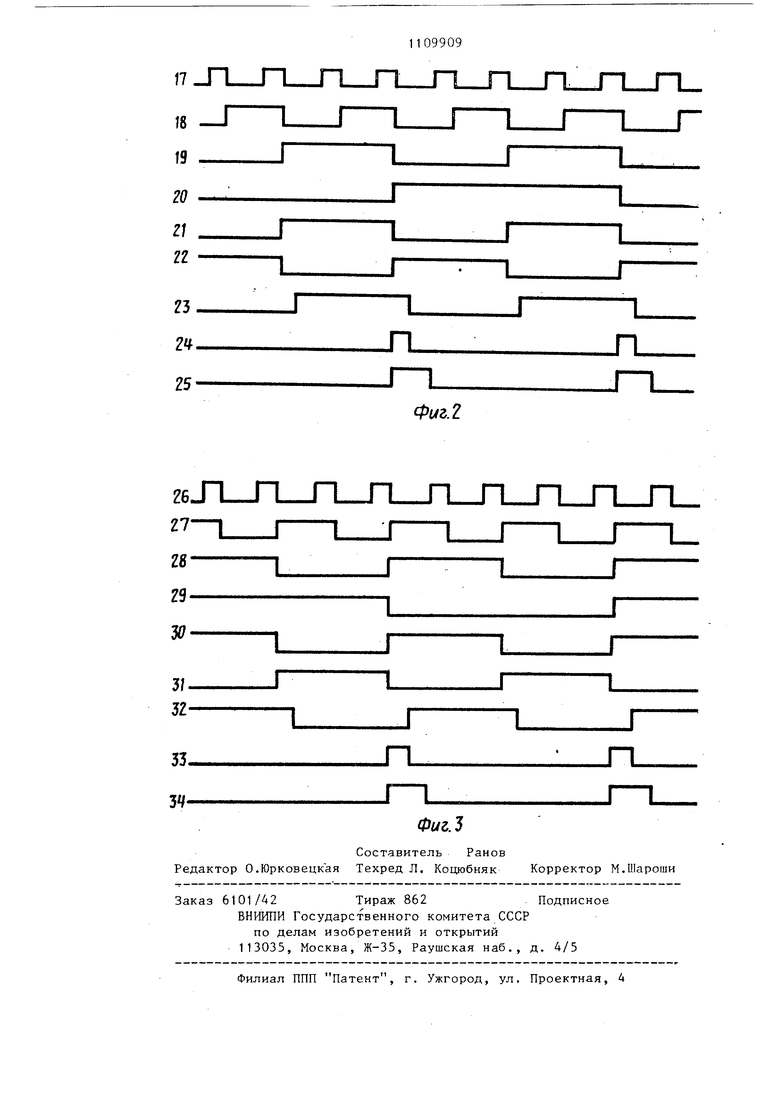

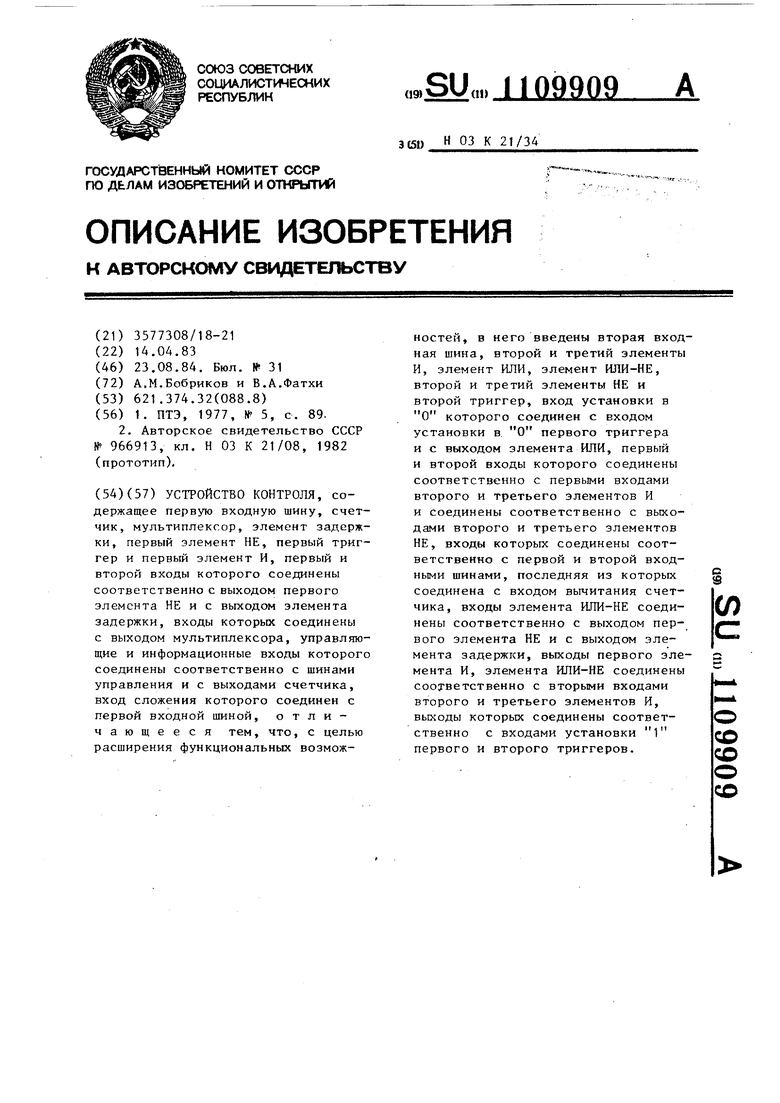

На фиг. 1 приведена структурная схема предлагаемого устройства к.онт, РОЛЯ; на фиг. 2 и 3 - временные диаграммы работы устройства в режимах прямого и обратного счета соответственно.

Устройство содержит мультиплексор 1, первый элемент НЕ 2, элемент 3 задержки, первый элемент И 4, первый триггер 5, счетчик 6, первую входную шину 7, шину 8 управления, вторую входную шину 9, элемент ИЛИ-НЕ 10, второй и третий элементы И 11 и 12 соответственно, второй и третий элементы НЕ 13 и 14 соответственно, элемент ИЛИ 15 и второй триггер 16.

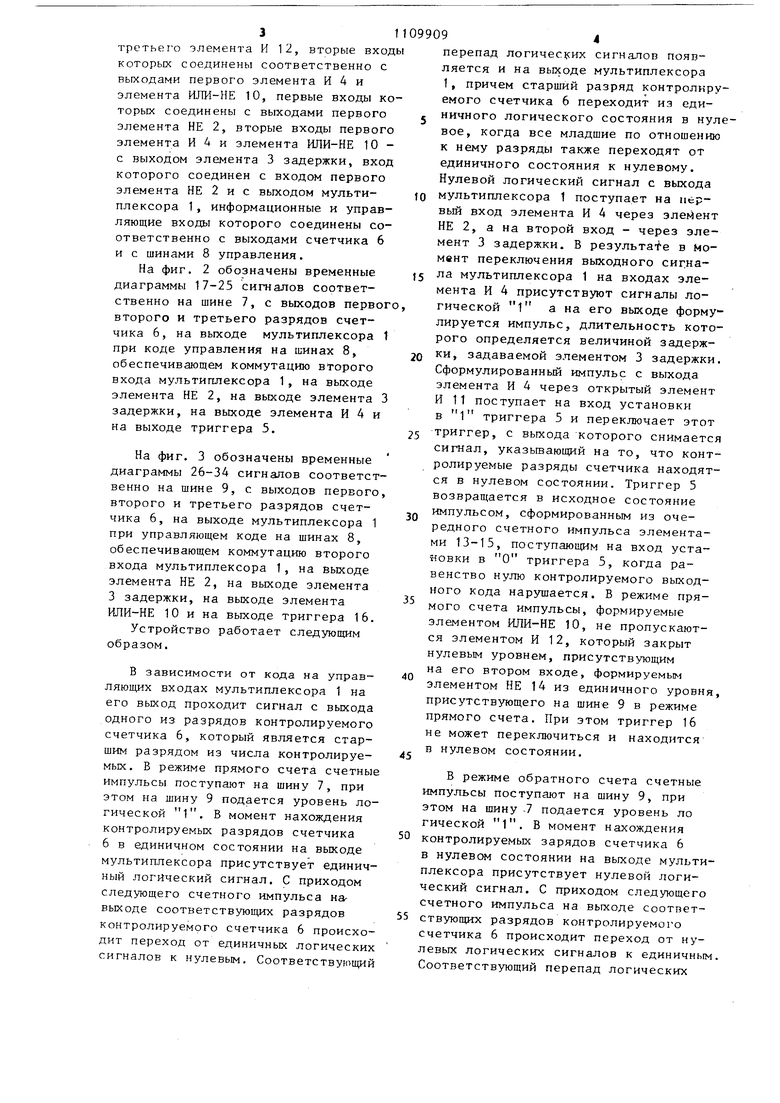

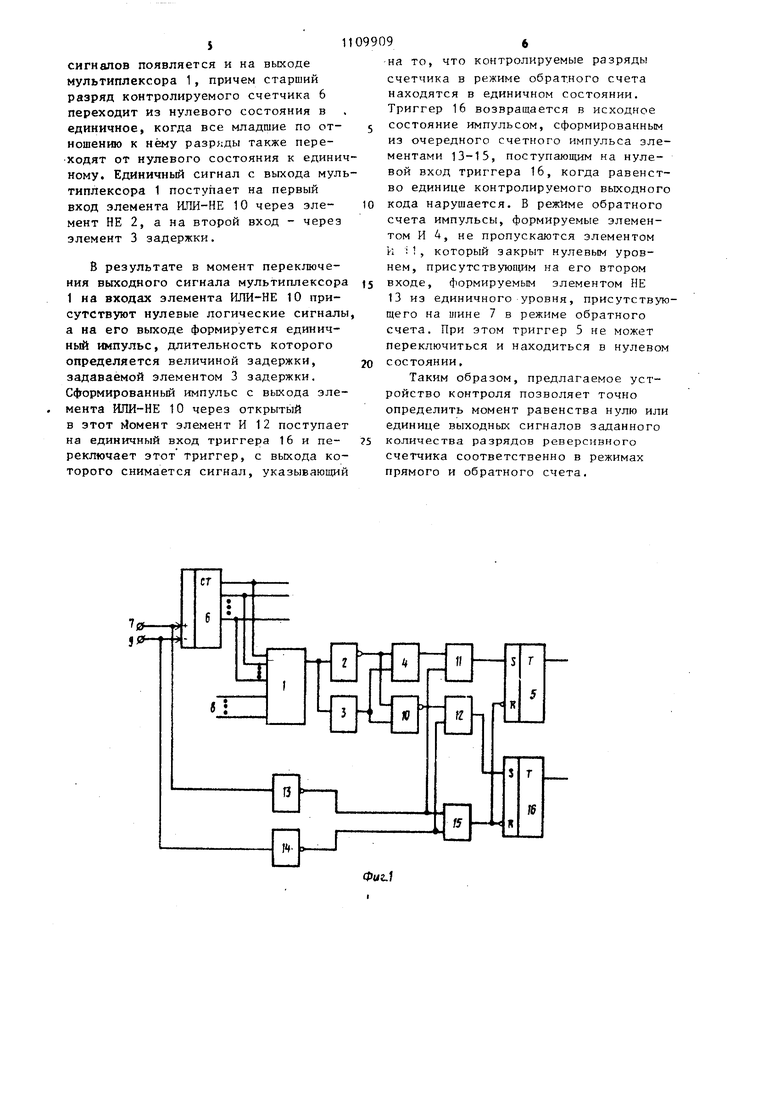

Первая входная шина 7 и вторая входная шина 9 соединены соответственно с входами сложения и вычитания счетчика бис входами второго элемента НЕ 13 и третьего элемента НЕ 14, выходы которых соединены соответственно с первыми входами второго элемента И 11 и третьего элемента И 12 и с первым и вторым входами элемента ИЛИ 15, выход которого соединен с входами установки в О первого триггера 5 и второго триггера 16, входы установки в 1 которых соединены соответственно с выходами второго элемента И 11 и третьего элемента И 12, вторые вхо которых соединены соответственно с выходами первого элемента И 4 и элемента ИЛИ-НЕ 10, первые входы к торых соединены с выходами первого элемента НЕ 2, вторые входы первог элемента И и элемента ИЛИ-НЕ 10 с выходом элемента 3 задержки, вхо которого соединен с входом первого элемента НЕ 2 и с выходом мультиплексора 1, информационные и управ ляющие входы которого соединены со ответственно с выходами счетчика 6 и с шинами 8 управления. На фиг. 2 обозначены временные диаграммы 17-25 сигналов соответственно на шине 7, с выходов перво второго и третьего разрядов счетчика 6, на выходе мультиплексора при коде управления на шинах 8, обеспечивающем коммутацию второго входа мультиплексора 1, на выходе элемента НЕ 2, на выходе элемента задержки, на выходе элемента И 4 и на выходе триггера 5. На фиг. 3 обозначены временные диаграммы 26-34 сигналов соответст венно на щине 9, с выходов первого второго и третьего разрядов счетчика 6, на выходе мультиплексора 1 при управляющем коде на шинах 8, обеспечивающем коммутацию второго входа мультиплексора 1, на выходе элемента НЕ 2, на выходе элемента 3 задержки, на выходе элемента ИЛИ-НЕ 10 и на выходе триггера 16. Устройство работает следующим образом. В зависимости от кода на управляющих входах мультиплексора 1 на его выход проходит сигнал с выхода одного из разрядов контролируемого счетчика 6, который является старшим разрядом из числа контролируемых. В режиме прямого счета счетны импульсы поступают на шину 7, при этом на шину 9 подается уровень логической 1. В момент нахождения контролируемых разрядов счетчика 6 в единичном состоянии на выходе мультиплексора присутствует единичный логический сигнал. С приходом следующего счетного импульса невыходе соответствующих разрядов контролируемого счетчика 6 происходит переход от единичных логических сигналов к нулевым. Соответствующий перепад логических сигна,пов появляется и на выходе мультиплексора 1, причем старший разряд контролируемого счетчика 6 переходит из единичного логического состояния в нулевое, когда все младшие по отношению к нему разряды также переходят от единичного состояния к нулевому. Нулевой логический сигнал с выхода мультиплексора 1 поступает на первый вход элемента И 4 через элемент НЕ 2, а на второй вход - через элемент 3 задержки. В результа е в Момент переключения выходного сигнала мультиплексора 1 на входах элемента И 4 присутствуют сигналы логической 1 а на его выходе формулируется импульс, длительность которого определяется величиной задержки, задаваемой элементом 3 задержки. Сформулированный импульс с выхода элемента И 4 через открытый элемент И 11 поступает на вход установки в 1 триггера 5 и переключает этот триггер, с выхода которого снимается сигнал, указьшающий на то, что контролируемые разряды счетчика находятся в нулевом состоянии. Триггер 5 возвращается в исходное состояние импульсом, сформированным из очередного счетного импульса элементами 13-15, поступающим на вход установки в О триггера 5, когда равенство нулю контролируемого выходного кода нарушается. В режиме прямого счета импульсы, формируемые элементом ИЛИ-НЕ 10, не пропускаются элементом И 12, который закрыт нулевым уровнем, присутствующим на его втором входе, формируемым элементом НЕ 14 из единичного уровня, присутствующего на шине 9 в режиме прямого счета. При этом триггер 16 не может переключиться и находится в нулевом состоянии. В режиме обратного счета счетные импульсы поступают на шину 9, при этом на шину -7 подается уровень ло гической 1. В момент нахождения контролируемых зарядов счетчика 6 в нулевом состоянии на выходе мультиплексора присутствует нулевой логиеский сигнал. С приходом следующего счетного импульса на выходе соответствующих разрядов контролируемого четчика 6 происходит переход от нуевых логических сигналов к единичным. оответствующий перепад логических сигналов появляется и на выходе мультиплексора 1, причем старший разряд контролируемого счетчика 6 переходит из нулевого состояния в единичное, когда все младшие по отношению к нему разряды также переходят от нулевого состояния к едини ному. Единичный сигнал с выхода мул типлексора 1 поступает на первый вход элемента ИЛИ-НЕ 10 через элемент НЕ 2, а на второй вход - через элемент 3 задержки. В результате в момент переключения в(гходного сигнала мультиплексор 1 на входах элемента ИЛИ-НЕ 10 присутствуют нулевые логические сигнал а на его выходе формируется единичный импульс, длительность которого определяется величиной задержки, задаваемой элементом 3 задержки, Сформированный импульс с выхода эле мента ШТИ-НЕ 10 через открытый в этот 1 омент элемент И 12 поступае на единичный вход триггера 16 и переключает этот триггер, с выхода ко торого снимается сигнал, указывающи 96 на то, что контролируемые разряды счетчика в режиме обратного счета находятся в единичном состоянии. Триггер 16 возвращается в исходное состояние импульсом, сформированным из очередного счетного импульса элементами 13-15, поступающим на нулевой вход триггера 16, когда равенство единице контролируемого выходного кода нарушается. В режиме обратного счета импульсы, формируемые элементом И 4, не пропускаются элементом к ; 1 , который закрыт нулевьЕм уровнем, присутствую цим на его втором входе, формируемым элементом НЕ 13 из единичного уровня, присутствующего на шине 7 в режиме обратного счета. При этом триггер 5 не может переключиться и находиться в нулевом состоянии. Таким образом, предлагаемое устройство контроля позволяет точно определить момент равенства нулю или единице выходных сигналов заданного количества разрядов реверсивного счетчика соответственно в режимах прямого и обратного счета.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство контроля электропитания процессора | 1984 |

|

SU1188741A1 |

| МОДУЛЬ МУЛЬТИМИКРОПРОГРАММНОЙ СИСТЕМЫ | 1997 |

|

RU2116665C1 |

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

| Настраиваемое логическое устройство | 1990 |

|

SU1784964A1 |

| Устройство для контроля функционирования логических блоков | 1986 |

|

SU1327107A1 |

| Устройство для контроля работоспособности счетчика | 1986 |

|

SU1378052A1 |

| Устройство для контроля счетчиков импульсов | 1985 |

|

SU1248061A1 |

| Устройство для контроля логических блоков | 1986 |

|

SU1401462A1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

УСТРОЙСТВО КОНТРОЛЯ, содержащее первую входную шину, счетчик, мультиплексор, элемент задержки, первый элемент НЕ, первый триггер и первый элемент И, первый и второй входы которого соединены соответственно с выходом первого элемента НЕ и с выходом элемента задержки, входы которых соединены с выходом мультиплексора, управляющие и информационные входы которого соединены соответственно с шинами управления и с выходами счетчика, вход сложения которого соединен с первой входной шиной, отличающееся тем, что, с целью расширения функциональных возможностей, в него введены вторая входная шина, второй и третий элементы И, элемент ИЛИ, элемент ИЛИ-НЕ, второй и третий элементы НЕ и второй триггер, вход установки в О которого соединен с входом установки в. О первого триггера и с выходом элемента ИЛИ, первый и второй входы которого соединены соответственно с первыми входами второго и третьего элементов И и соединены соответственно с выходами второго и третьего элементов НЕ, входы которых соединены соответственно с первой и второй входi ными шинами, последняя из которых соединена с входом вычитания счет(Л чика, входы элемента ИЛИ-НЕ соединены соответственно с выходом первого элемента НЕ и с выходом элемента задержки, выходы первого элемента И, элемента ИЛИ-НЕ соединены соответственно с вторыми входами второго и третьего элементов И, вькоды которых соединены соответ1Г 4 It ственно с входами установки со ;о первого и второго триггеров. о со

СГ

13

1

№

ff

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| ПТЭ, 1977, № 5, с | |||

| Способ размножения копий рисунков, текста и т.п. | 1921 |

|

SU89A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство контроля | 1981 |

|

SU966913A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1984-08-23—Публикация

1983-04-14—Подача