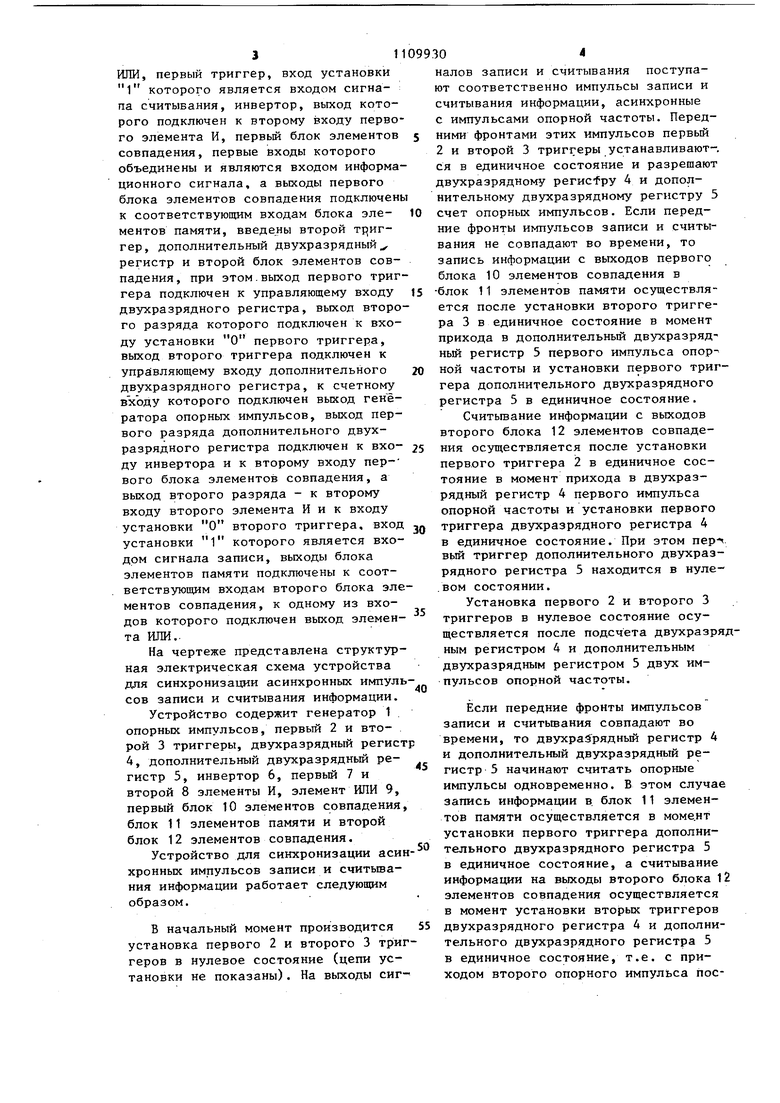

Изобретение относится к радиотех нике и вычислительной технике и может быть использовано в система х об мена данными для обеспечения синхронизации асинхронных импульсов записи и считьгоания информации. Известно устройство для синхронизации асинхронных импульсов записи и считывания информации, содержащее последовательно соединенные генератор сигналов считывания и триггер, прямой и инверсный выходы которого через первый и второй элементы совпадения подклкЛены соответственно к другим входам элемента ИЛИ и инвертора, последовательно соединенные блок выделения тактовых импульсов, распределитель сигналов записи, блок элементов совпадения и блок элементов памяти, другие входы которого подключены к выходам распределителя сигналов считывания, первый и второй элементы И, первые объединенные входы которых подключены к выходу перво го разряда распределителя сигналов считывания, вторые входы первого и второго элементов И - соответственно к прямому и инверсному входам триггера, а третьи входы первого и второго элементов И - соответственно к .прямому и инверсному выходам счетчика импульсов, первый и второй управляющие входы которого подключены к выходам первого и второго элементов а счетный вход счетчика импульсов к выходу генератора сигналов считывания, выходы первого, второго и последнего разрядов распределителя сигналов записи подсоединены соответственно к вторым входам второго и первого элементов совпадения и входу установки О триггера, а объединенные вторые входы блока элементов сов падения и блока вьзделения тактовых и fflyльcoв являются входом устройства 1. Недостатком данного устройства является низкая точность синхронизации. Наиболее близким техническим реше нием к изобретению является устройст во для синхронизации асинхронных импульсов записи и считьюания лнформации, содержащее генератор опорных импульсов, выход которого подключен к счетному входу двухразрядного регистра, выходы разрядов которого подключены соответственно к первым входам первого и второго элементов И выходы которых подключены к входам .элемента ИЛИ, первый триггер, вход установки 1 которого является входом сигнала считывания, инвертор, выход которого подключен к второму входу первого элемента И, первьй блок элементов совпадения, первые входы которого объединены и являются входом информационного сигнала, а выходы первого блока элементов совпадения подключены к соответствующим входам блока элементов памяти, выход гене.ратора одиночных импульсов подсоединен к управляющему входу двухразрядного регистра и входу установки О первого триггера, вход инвертора и опорный вход генератора одиночньгх импульсов подключены к выходу генератора опорных импульсов, выход инвертора подсоединен к второму входу второго элемента И, третьи входы первого и второго элементов И подключены соответственно к инверсному и прямому выходам первого триггера, выход элемента ИЛИ подсоединен к счетному входу распределителя сигналов записи, выходы которого подсоединены к соответствующим вторым входам первого блока элементов совпадения, а выходы распределителя сигналов считывания к соответствующим вторым входам блока элементов памяти, счетный вход распределителя сигналов считьтания подключен к входу установки 1 первого триггера, причем сигнальный вход генератора одиночных импульсов является входом сигнала записи, а выходы блока элементов памяти - выходами устройства 2. Недостатком известного устройства является низкая точность синхронизации из-за возможности совпадения во времени процессов записи и считывания информации. Цель изобретения - повьппение точности синхронизации путем исключения возможности совпадения во времени процессов записи и считывания информации . Для достижения цели в устройство для синхронизации асинхронных импульсов записи и считьгоания информации, содержащее генератор опорных импульсов, выход которого подключен к счетному входу двухразрядного регистра, выходы разрядов которого подключены соответственно к первым входам первого и второго элементов И, выходы которых подключены к входам элемента ИЛИ, первый триггер, вход установки 1 которого является входом сигнапа считывания, инвертор, выход которого подключен к второму входу перво го элемента И, первьм блок элементов совпадения, первые входы которого объединены и являются входом информа ционного сигнала, а выходы первого блока элементов совпадения подключен к соответствующим входам блока элементов памяти, введены второй тциггер, дополнительный двухразрядный регистр и второй блок элементов совпадения, при этом.выход первого триг гера подключен к управляющему входу двухразрядного регистра, выход второ го разряда которого подключен к входу установки О первого триггера, выход второго триггера подключен к управляющему входу дополнительного двухразрядного регистра, к счетному входу которого подключен выход генератора опорных импульсов, выход первого разряда дополнительного двухразрядного регистра подключен к входу инвертора и к второму входу первого блока элементов совпадения, а выход второго разряда - к второму входу второго элемента Ник входу установки О второго триггера, вход установки 1 которого является входом сигнала записи, выходы блока элементов памяти подключены к соответствующим входам второго блока эл ментов совпадения, к одному из входов которого подключен выход элемен та ИЛИ.. На чертеже представлена структур ная электрическая схема устройства для синхронизации асинхронных импул сов записи и считывания информации. Устройство содержит генератор 1 опорных импульсов, первый 2 и второй 3 триггеры, двухразрядный регис 4, дополнительный двухразрядный регистр 5, инвертор 6, первый 7 и второй 8 элементы И, элемент ИЛИ 9, первый блок 10 элементов совпадения блок 11 элементов памяти и второй блок 12 элементов совпадения. Устройство для синхронизации аси хронных импульсов записи и считьгоания информации работает следующим образом. В начальный момент производится установка первого 2 и второго 3 три геров в нулевое состояние (цепи установки не показаны). На выходы сиг налов записи и считывания поступают соответственно импупьсы записи и считывания информации, асинхронные с импульсами опорной частоты. Передними фронтами этих импульсов первый 2 и второй 3 триггеры устанавливают-, ся в единичное состояние и разрешают двухразрядному peгиcfpy 4 и дополнительному двухразрядному регистру 5 счет опорных импульсов. Если передние фронты импульсов записи и считывания не совпадают во времени, то запись информации с выходов первого блока 10 элементов совпадения в блок 11 элементов памяти осуществляется после установки второго триггера 3 в единичное состояние в момент прихода в дополнительный двухразрядный регистр 5 первого импульса опор ной частоты и установки первого триггера дополнительного двухразрядного регистра 5 в единичное состояние. Считьтание информации с выходов второго блока 12 элементов совпадения осуществляется после установки перв.ого триггера 2 в единичное состояние в момент прихода в двухразрядный регистр 4 первого импульса опорной частоты и установки первого триггера двухразрядного регистра 4 в единичное состояние. При этом первый триггер дополнительного двухразрядного регистра 5 находится в нулевом состоянии. Установка первого 2 и второго 3 триггеров в нулевое состояние осуществляется после подсчета двухразрядным регистром 4 и дополнительным двухразрядным регистром 5 двух импульсов опорной частоты. Если передние фронты импульсов записи и считьтания совпадают во времени, то двухраЗ рядный регистр 4 и дополнительный двухразрядный регистр 5 начинают считать опорные импульсы одновременно. В этом случае запись информации в блок 11 элементов памяти осуществляется в моме.нт установки первого триггера дополнительного двухразрядного регистра 5 в единичное состояние, а считывание информации на выходы второго блока 12 элементов совпадения осуществляется в момент установки вторых триггеров двухразрядного регистра 4 и дополнительного двухразрядного регистра 5 в единичное состояние, т.е. с приходом второго опорного импульса поспе установки 2 и второго 3 триггеров в единичное состояние.

Следовательно, во всех случаях импульсы записи информации в блок 11 элементов памяти и импульсы считьгоания из него информации, асинхронные с импульсами опорной частоты, сдвинуты друг относительно друга на один

и более периодов следования опорных импульсов.

Таким образом, в предложенном устройстве исключается возможность совпадения во времени процессов записи и считьгеания информации и тем самым повышается надежность его функционирования.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синхронизации асинхронных импульсов записи и считывания информации | 1975 |

|

SU603136A1 |

| УСТРОЙСТВО ДЛЯ ЗАДЕРЖКИ СИГНАЛОВ | 1992 |

|

RU2024186C1 |

| Устройство для отображения информации на экране телевизионного приемника | 1987 |

|

SU1522271A1 |

| Буферное запоминающее устройство | 1984 |

|

SU1242968A1 |

| Селектор импульсов по длительности | 1988 |

|

SU1529437A1 |

| Устройство для сопряжения вычислительной машины с магистралью обмена | 1986 |

|

SU1381519A1 |

| Цифровой измеритель частоты заполнения радиоимпульсов | 1982 |

|

SU1161892A1 |

| НАКОПИТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2089043C1 |

| Приемное устройство дополнительной цифровой информации, передаваемой в составе кадрового гасящего импульса полного телевизионного сигнала | 1988 |

|

SU1653179A1 |

| Буферное запоминающее устройство | 1978 |

|

SU942132A1 |

УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ АСИНХРОННЫХ ИМПУЛЬСОВ ЗАПИСИ И СЧИТЬВАНИЯ ИНФОРМАЦИИ, содержащее генератор опорных импульсов, выход которого подключен к счетному входу двухразрядного регистра, выходы разрядов которого подключены соответственно к первым входам первого и второго элементов И, выходы которых подключены к входам элемента ИЛИ, первый триггер, вход установки 1 которого является входом сигнала считывания, инвертор, выход которого подключён к второму входу первого элемента И, первый блок элементов совпадения, первые входы которого объединены и являются входом информационного сигнала, а выходы первого блока элементов совпадения подключены к соответствующим входам блока элементов памяти, отличающееся тем, что, с целью повышения точности синхронизации путем исключения возможности совпадения во времени процессов записи и считывания информации, введены второй триггер, дополнительньш двухразрядных регистр и второй блок элементов совпадения, при этом выход первого триггера подключен к управляющему входу двухразрядного регистра, выход второго разряда которого подключен к входу установки О первого триггера, выход второго триггера подключен к управляющему входу дополнительного двухразрядного регистра, к счетному входу которого подключен выход генератора опорных (О импульсов, выход первого разряда дополнительного двухразрядного регистра подключен к входу инвертора и к второму входу первого блока элементов совпадения, а выход второго разряда - к второму входу второго элемента И и к входу установки О второго триггера, выход установки 1 со со которого является входом сигнала эаписи, выходы блока элементов памяти 00 подключены к соответствующим входам второго блока элементов совпадения, к одному из входов которого подключен выход элемента ИЛИ.

1

Г

0-

г

Т

ю

12

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Сихронизатор независимых импульсных последовательностей | 1974 |

|

SU537452A2 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для стягивания ленты | 1977 |

|

SU630136A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1984-08-23—Публикация

1981-06-17—Подача