Изобретение относится к вычислительной технике и может использовать ся в устройствах передачи данньк.

Целью изобретения является расширение области применения за счет адаптации устройства к виду и скороети принимаемой и выдаваемой информации.

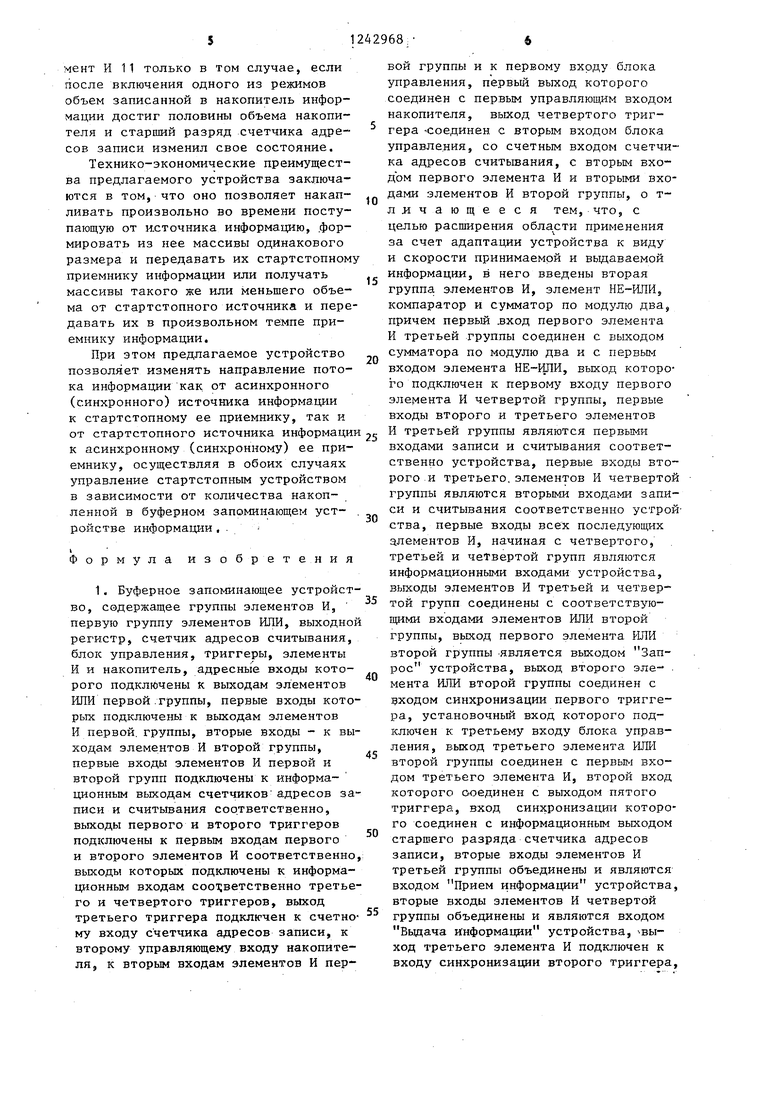

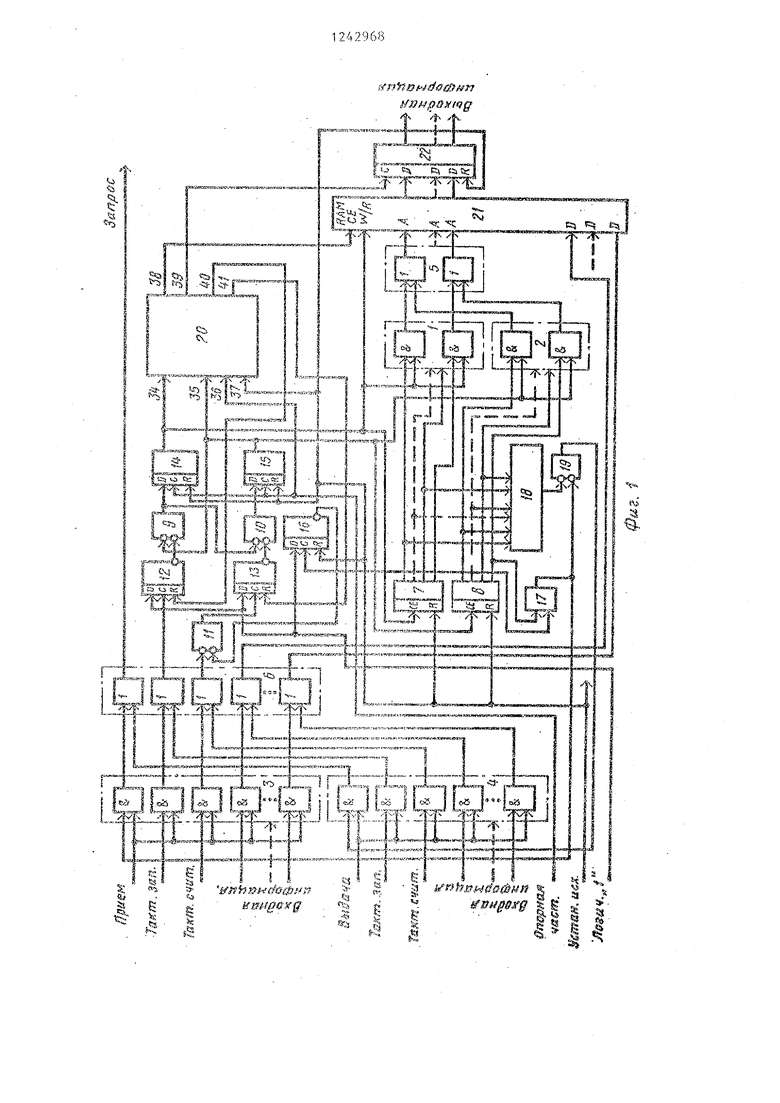

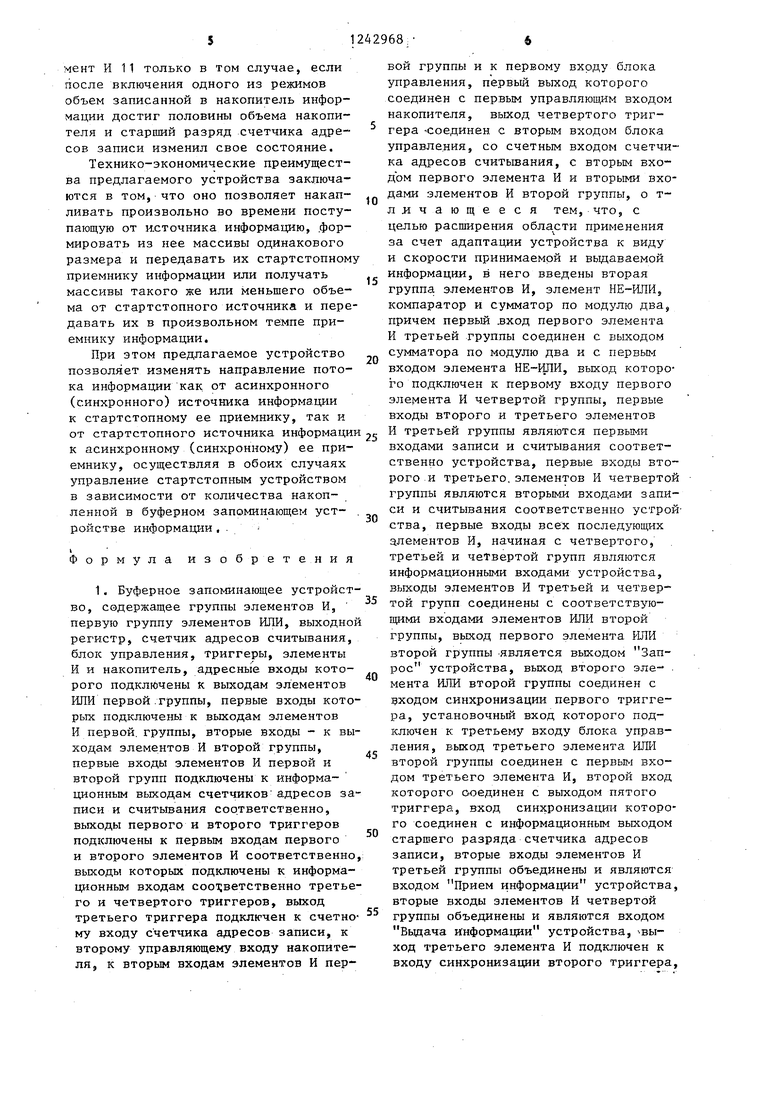

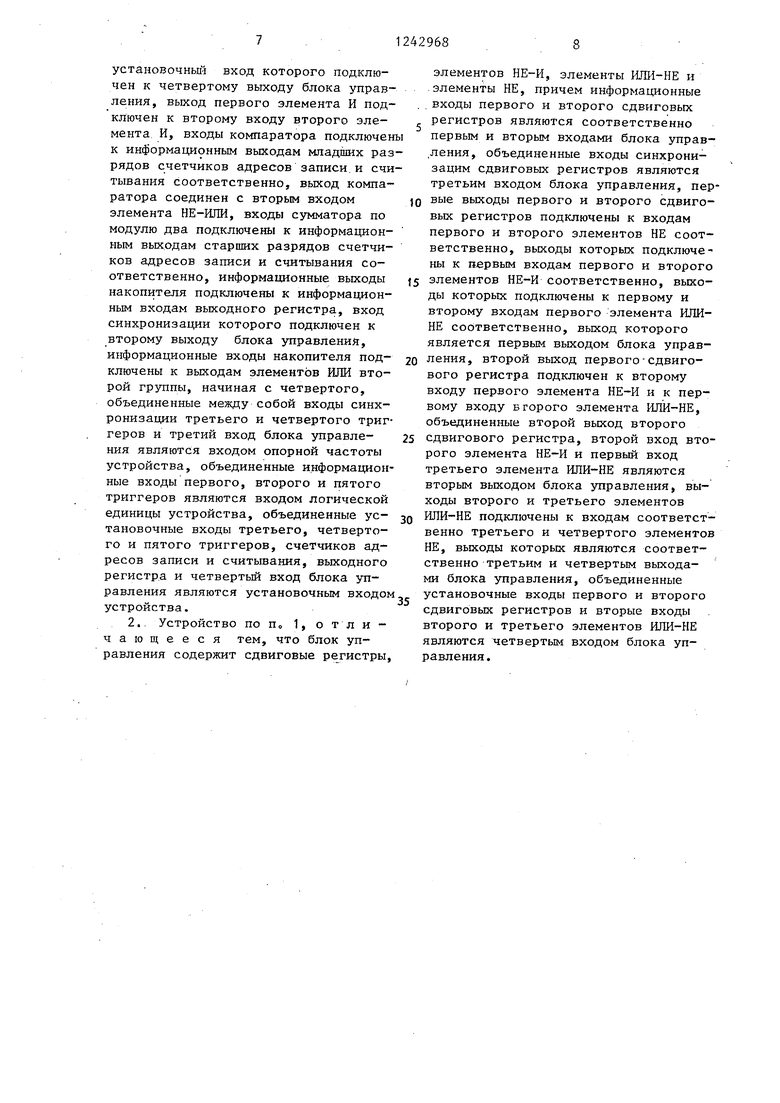

На фиг, 1 представлена схема уст-, ройства) на фиг. 2 - функциональная схема блока управления.

Устройство содержит (фиг. 1) первую 1, вторую 2, третью 3 и четвертую 4 группы элементов И, первую 5 и вторую 6 группы элементов ИЛИ, счетчик 7 адресов записи, счетчик 8 адресов считывания, первый 9, второй 10 и третий 11 элементы И, первый 12, второй 13, третий 14, четвертый 15 и пятый 16 триггеры, сумматор 17 по модулю два, компаратор 18, элемент НЕ-ИЛИ 19, блок 20 управления, накопитель 21, выходной регистр 22.

Блок 20 управления (фиг. 2) содержит первьш 23 и второй 24 сдвиго ные регистры, первый 25, второй -26, третий 27 и четвертый 28 элементы НЕ первый 29 и второй 30 элементы НЕ-И, первый 31, второй 32 и третий 33 элементы .

- Кроме того, устройство имеет входы с первого по четвертый 34-37 и выходы с первого по четвертый 38-41. Группы 1 и 2 элементов И совместно с группой 5 элементов ИЛИ могут быть вьтолнены на микросхемах 564ЛС2 так же, как и группы 3 и 4 элементов И совместно с группой 6 элементов ИЛИ. Счетчики 7 и 8 могут быть выполнены на ми кросхемах 564ИЕ10, элементы И 9-11, НЕ-И 29 и 30 и элементы ИЛИ-НЕ 31-33 на микросхемах 564ЛЕ5 триггеры 12-16 - на микросхемах .564ТМ25 сумматор 17 по модулю два - на микросхемах 564ЛП2, компара-тор 18 - на микросхемах 564ИП25 элемент НЕ-ИЛИ 19 - на микросхемах 564ЛА7, накопитель 21 - на микросхемах 564РЗ выходной регистр 22 - на микросхемах 564ТМ2 с объединенными R- и С-входа- ivffi триггеров, сдвиговые регистры 23 и 24 - на микросхемах 564ИР25 элемен ты НЕ 25-28 - на микросхеме 564ЛН2. Устройство рабод ает следующим образом.

Перед началом любого пз режимов Прием информации или Выдача информации на устойчивый вход устройства аоступает импульс установки, сбрасы

5

0

вающии все триггеры, счетчики и регистры в исходное (нулевое).состояние,

В режиме Прием информации сигнал прием на втор)ых входах элементов И третьей группы 3 и второй элемент ИЛИ второй группы 6 импульсов тактовой частоты записи, сопровождающей входную информацию на вход синхронизации первого триггера 12, который переходит в состояние 1, и при нахождении триггера 15 в состоянии О (нет считывания информации в данный момент) элемент И 9 разрешает включение триггера 14 по первому импульсу опорной частоты, постоянно присутствующей на входе устройства и на входе 36 блока управления.

Сигнал с выхода триггера 14 (сигнал разрешения записи) поступит на второй управляющий вход накопителя 21 (вход Запись-чтение), разрешит прохождение кода адреса с выхода счетчика 7 адресов записи через группу 1 элементов И и группу 5 элементов 5 ИЛИ на адресные входы накопителя 21. Также этот сигнал поступает на счетный вход счетчика 7, который по его заднему фронту изменит свое состояние (содефжимое счетчика увеличится на единицу) и на первый вход 34 блока 20 управления, в котором при этом записываются в сдвиговый регистр 23 и сдвигаются в нем символы 1 по каждому такту опорной частоты.

В течение временного интервала, когда на выходе сдвигового регистра 23, подключенному к входу элемента НЕ 25, логическ:ая 1, з- на выходе, подключенном к .второму дзходу элемента 29, логический О, элемент НЕ-И 29 сформирует импульс, который начнется позже, а окончится раньше сигнала разрешения записи на время, кратное периоду опорной частоты, этому периоду будет кратна и длительность упомянутого импульса, который через элемент ШИ-НЕ 31 поступит на выход 38 блока 20 управления и на первый управляющий вход накопителя 21 (вход выбора кристалла).

Считывание информации из накопителя 21 не прок сходит до тех пор, пока старший разряд счетчика 7 адресов записи не изменит свое состояние на 1 (т.е. пока не будет заполнено 5 не менее половины накопителя 21), при этом включится триггер 16 и разрешит прохождение импульсов тактовой частоты считывания через третий эле0

5

0

5

0

3

мент И группы 3, третий элемент ИЛИ группы 6 и элемент И 11 на вход синхронизации триггера 13.

.Одновременно, в результате сравнения состояний старших разрядов счетчика 7 адресов записи и счетчика 8 адресов считывания на выходе сумматора 17 по модулю два появится сигнал Запрос, который через первый элемент И группы 3 и первый элемент ИЛИ группы 6 выдает приемнику информацию для запроса на считывание им из устройства информации,

Импульсы тактовой частоты считывания переводят в состояние 1 триггер 13 и, если в этот момент нет сигнала, разрешающего запись на выходе элемента И 9, элемент И 10 разреишт включение триггера 15 по первому импульсу опорной частоты.

Сигнал с выхода триггера 15 (сигнал разрешения считывания) разрешит прохождение кода адреса с выходов счетчика 8 адресов считывания через группу 2 элементов И и группу 5 элементов ИЛИ на адресные входы накопителя 21. Также этот сигнал поступит на счетный вход счетчика 8, который по его заднему фронту изменит свое состояние (содержимое счетчика увеличится на единицу), и на второй вхо 35 блока 20 управления, в который при этом записываются в сдвиговый регистр 24 и сдвигаются в нем символ 1 по каждому такту опорной частоты

В течение временного интервала, когда на выходе сдвигового регистра 24, подключенном к входу элемента НЕ 26, логическая 1, а на выходе, подключенном к второму входу элемента НЕ-И 30, логический О, элемент НЕ-И 30 аналогично элементу НЕ-И 29 при записи сформирует импульс, который через элемент -ИЛИ-НЕ 31 и выход 38 блока 20 управления поступит на первьй управляющий вход накопителя 21 (вход выбора кристалла).

При записи символа 1 в разряд сдвигового регистра 24, выход которого подключен к вькоду 39 блока управления, сигнал с этого выхода поступит на вход синхронизации выходного регистра 22, в который при этом перепишется информация с выходов накопителя 21.

При записи символов. 1 в разряд сдвиговых регистров 23 при записи и 24 при считьшании, выходы которых подключены к первым входам элементов

f5

20

2429684

ИЛИ-НЕ 32 и 33 соответственно, через элементы ИЛИ-НЕ 32 и 33, элементы НЕ 27 и 28 и выходы 40 и 41 блока 20 . управления на установочные входы , триггеров 12 и 13 соответственно поступят сигналы сброса так же, как и при поступлении на установочньй вход устройства импульса установки устройства в исходное состояние, которьш Q поступит на вход 37 блока 20 управления, на вторые входы элементов И-НЕ 32 и 33 и через инверторы 27 и 28 - на установочные входы триггеров 12 и 1-3 соответственно.

Сброс триггеров 12 и 13 приведет к записи символов О в триггеры 14 и 15 и в сдвиговые регистры 23 и 24 соответственно.

Входная информация поступает на информационные входы накопителя через четвертый и последующие элементы И групп 3 и четвертый и последующие элементы ИЛИ группы 6.

В режиме Прием информации информация стартстопному управляемому приемнику информации вьщается массивами, равнйгми по величине половине объема накопителя 21, независимо от скорости и неравномерности поступления информации от источника информации.

В режиме Вьщлча информации устройство работает аналогично режиму Прием со следуюнщми отличиями.

Вместо группы 3 элементов И сигналы проходят через группу 4 элемен- 35 тов И. . .

Сигнал Запрос сформируется при условии совпадения старших разрядов счетчика 7 адресов записи и счетчика 8 адресов считывания, при этом сиг- нал Запрос формируется на выходе сумматора 17 по модулю два или при условии, если содержимое п - 1 млад ших разрядов счетчика 7 адресов записи не больше содержимого п - 1 младших разрядов счетчика 8 адресов

25

30

40

5

считывания, при этом сигнал Запрос формируется на выходе компаратора 18. На выход Запрос устройства любой

J13 упомянутых сигналов поступает через элемент НЕ-ИЛИ 19 и первые элементы И группы 4 и ИЛИ группы 6.

Таким образом, запрос на начало вьщачи очередного массива выдается стартстолному источнику информации при условии, если свободного - не менее половины объема накопителя 21.

.Триггер 16 ра1зрешает прохождение тактовой частоты считывания через элемент И 11 только в том случае, если после включения одного из режимов объем записанной в накопитель информации достиг половины объема накопителя и старший разряд счетчика адресов записи изменил свое состояние.

Технико-экономические преимущества предлагаемого устройства заключаются в том, что оно позволяет накап- ливать произвольно во времени поступающую от источника информацию, .формировать из нее массивы одинакового размера и передавать их стартстопном приемнику информации или получать массивы такого же или меньшего объема от стартстопного источника и передавать их в произвольном темпе приемнику информации.

При этом предлагаемое устройство позволяет изменять направление потока информации как; от асинхронного (синхронного) источника информации к стартстопному ее приемнику, так и от стартстопного источника информаци к асинхронному (синхронному) ее приемнику, осуществляя в обоих случаях управление стартстопным устройством в зависимости от количества накопленной в буферном запоминающем устройстве информации. .

Формула изобретения

1, Буферное запоминающее устройство, содержащее группы элементов И, первую группу элементов ИЛИ, выходной регистр, счетчик адресов считывания, блок управления, триггеры, элементы И и накопитель, адресные входы которого подключены к выходам элементов ИЛИ первой .труппы, первые входы которых подключены к выходам элементов И первой, группы, вторые входы - к выходам элементов И второй группы, первые входы элементов И первой и второй групп подключены к информационным выходам счетчиков адресов записи и считьгоания соответственно, выходы первого и второго триггеров подключены к первым входам первого и второго элементов И соответственно, выходы которых подключены к информационным входам cooTjBeTCTBBHHO третьего и четвертого триггеров, выход третьего триггера подключен к счетно му входу счетчика адресов записи, к второму управляющему входу накопителя,, к вторым входам элементов И пер.

.« .,., ji;

30

35

40

45

50

55

вой группы и к первому входу блока управления, первый выход которого соединен с первым управляющим входом накопителя, выход четвертого триггера Соединен с вторым входом блока управле.ния, со счетным входом счетчика адресов считывания, с вторым входом первого элемента И и вторыми входами элементов И второй группы, о т- л .и ч а ю щ е е с я тем, что, с целью расширения применения за счет адапта:ции устройства к виду и скорости принимаемой и вьщаваемой информации, в него введены вторая группа элементов И, элемент НЕ-ИЛИ, компаратор и сумматор по модулю два, причем первый .вход первого элемента И третьей труппы соединен с выходом сумматора по модулю два и с первым входом элемента НЕ-Ш1И, выход которого подключен к первому входу первого элемента И четвертой группы, первые входы второго и третьего элементов И третьей группы являются первыми входами записи и считывания соответственно устройства, первые входы второго и третьего, элементов И четвертой группы являются вторыми входами записи и считывания соответственно устройства, первые входы всех последующих элементов И, начиная с четвертого, третьей и четвертой групп являются информационными входами устройства, выходы элементов И третьей и четвертой групп соединены с соответствующими входами элементов ИЛИ второй группы, выход первого элемента ШШ второй группы -является выходом Запрос устройства, выход второго эле- - мента ИЛИ второй группы соединен с уходом синхронизации первого триггера, уста.новочный вход которого подключен к третьему входу блока управления, выход третьего элемента ИЛИ второй группы соединен с первым входом третьего элемента И, второй вход которого ооединен с выходом пятого триггера, вход синхронизации которого соединен с информационным выходом старшего разряда счетчика адресов записи, вторые входы элементов И третьей группы объединены и являются входом Прием информации устройства, вторые входы элементов И четвертой группы объединены и являются входом Вьщача информации устройства, вы- ход третьего элемента И подключен к входу синхронизации второго триггера.

установочньш вход которого подключен к четвертому выходу блока управления, выход первого элемента И подключен к второму входу второго элемента И, входы компаратора подключен к информационным выходам младших разрядов счетчиков адресов записи.и считывания соответственно, вькод компаратора соединен с вторым входом элемента НЕ-ИЛИ, входы сумматора по модулю два подключены к информационным выходам старших разрядов счетчиков адресов записи и считывания соответственно, информационные выходы накопителя подключены к информационным входам выходного регистра, вход синхронизации которого подключен к второму выходу блока управления, информационные входы накопителя под- ключены к выходам элементов ИЛИ второй группы, начиная с четвертого, объединенные между собой входы синхронизации третьего и четвертого триггеров и третий вход блока управле- ния являются входом опорной частоты устройства, объединенные информационные входы первого, второго и пятого триггеров являются входом логической единицы устройства, объединенные ус- тановочные входы третьего, четвертого и пятого триггеров, счетчиков адресов записи и считывания, выходного регистра и четвертый вход блока управления являются установочным входом устройства.

2.. Устройство по По 1, отличающееся тем, что блок управления содержит сдвиговые регистры.

JQ J5 20 25 зо

5

элементов НЕ-И, элементы ШШ-НЕ и элементы НЕ, причем информационные . входы первого и второго сдвиговых регистров являются соответственно первым и вторым входами блока управ- ,ления, объединенные входы синхрони- зацим сдвиговых регистров являются третьим входом блока управления, первые выходы первого и второго сдвиговых регистров подключены к входам первого и второго элементов НЕ соответственно, выходы которых подключены к первым входам первого и второго элементов НЕ-И соответственно, выходы которых подключены к первому и второму входам первого элемента ИЛИ- НЕ соответственно, выход которого является первым выходом блока управления, второй выход первого-сдвигового регистра подключен к второму входу первого элемента НЕ-И и к первому входу второго элемента ШШ-НЕ, объединенные второй выход второго сдвигового регистра, второй вход второго элемента НЕ-И и первый вход третьего элемента ИЛИ-НЕ являются вторым выходом блока управления, выходы второго и третьего элементов ИЛИ-НЕ подключены к входам соответственно третьего и четвертого элементов НЕ, выходы которых являются соответственно третьим и четвертым выходами блока управления, объединенные установочные входы первого и второго сдвиговых регистров и вторые входы второго и третьего элементов ИЛИ-НЕ являются четвертым входом блока управления.

n }fjdarj fifj

if//7A ,

|ч/ф ж.

-M« J : &«OEiaH I :«ltl

«г

.s

i.iS

(1бф; f

w KnujM g , g. - -

fc

El и ynbandocoi n

S

a

л

p

«II

3

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1983 |

|

SU1116458A1 |

| Устройство для регистрации цифровой информации | 1986 |

|

SU1386915A2 |

| Система для обмена информацией | 1990 |

|

SU1815646A1 |

| Устройство для коррекции ошибок в блоках памяти | 1985 |

|

SU1257708A1 |

| Буферное запоминающее устройство с самоконтролем | 1982 |

|

SU1084890A1 |

| Буферное запоминающее устройство | 1982 |

|

SU1048516A1 |

| Устройство для считывания графической информации | 1986 |

|

SU1354225A1 |

| Ассоциативный параллельный процессор | 1981 |

|

SU1166128A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С РЕЗЕРВИРОВАНИЕМ | 1990 |

|

RU2024969C1 |

| Устройство для формирования видеосигнала | 1990 |

|

SU1741124A1 |

Изобретение относится к вычисли- тельной технике, а именно к устрой-. .ствам для обработки и хранения цифровой информации, и может быть использовано при необходимости согласования устройств, работающих с различными темпами обработки информации. Цель .изобретения - расширение области применения устройства за счет адаптации устройства к виду и скорости принимаемой и выдаваемой информации. Устройство содержит группы элементов И и ИЛИ, элементы И, НЕ, ИЛИ-НЕ, НЕ- ИЛИ, НЕ-И, триггеры, счетчики адресов записи и считьшания, выходной регистр, сдвиговые регистры, компаратор, сумматор по модулю два и накопитель, соединенные между собой- в соответствии с выполняемыми функциями. Изобретение позволяет накапливать произвольно во времени поступающую от источника информацию, формировать из нее массивы одинакового размера и передавать их стартстопно- му приемнику информации, а получать массивы такого же или меньшего объема от стартстопного источника и пер е- давать их в произвольном темпе прием-, кику информации. При этом устройство позволяет изменять направление потока информации как асинхронного (синхронного) источника информации к старт- стопному ее приемнику, так и от стартстопного источника информации к асинхронному (синхронному) ее приемнику, осуществляя в обоих случаях управление стартстопным устройством в зависимости от количества накопленной в устройстве информации., 1 з.п. ф-лы, 2 ил. с Ф Ю 4 IS9 ;о О5

Редактор Н.Гунько

Составитель В.Фокина

Техред М.Ходанич Корректор А.Обручар

Заказ 3707/49Тираж 671 . Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Стартстопно-синхронный передатчик | 1979 |

|

SU832762A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Буферное запоминающее устройство | 1980 |

|

SU932566A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-07-07—Публикация

1984-11-23—Подача