Изобретение относится к вычислительной технике и может быть использовано в качестве процессора вычислительной машины,, предназначенной для параллельной обработки массивов информации.

Известна ассоциативная запоминающая матрица, содержащая ассоциативные запоминающие элементы, состоящие из триггера и логической схемы, причем в каждой строке матрицы первый и второй выходы каждого элемента, кроме последнего, соединены соответственно с первым и вторым входами левого, соседнего элемента, д третий выход каждого элемента, кроме первого, - с третьим входом правого соседнего элемента, четвертый вход всех элементов каждого столбца матрицы - с соответствующим номеру столбца разрядом внещнего регистра компаранда, управляющие входы элементов подключены к соответствующим управляющим шинам матрицы fl.

Матрица обладает ограниченными функциональными возможностями и низким быстродействием при выполнении операций над элементами двух массивов информации или операций, в которых участвуют элементы одного и того же массива, так как в ней т)тсутствуют информационные связи между строками. Эти операции можно производить построчно, но это приводит к значительным затратам времени.

Наиболее близким техническим рещением к изобретению является ассоциативная матрица памяти, содержащая ассоциативные запоминающие элементы, причем в каждой строке матрицы выходы сравнения и переноса- сравнения каждого ассоциативного запоминающего элемента, кроме последнего, соединены с соответствующими входами, последующего ассоциативного запоминающего элемента, а выход переноса сложения каждого ассоциативного запоминающего элемента, кроме первого - с соответствующим входом предыдущего ассоциативного запоминающего элемента, управляющие входы ассоциативных запоминающих элементов подключены к соответствующим управляющим щинам, а также адресные накопители и коммутаторы по числу ассоциативных запоминающих элементов, причем выход каждого коммутатора подключен к информационному входу соответствующего ассоциативного запоминающего элемента, первый вход - к информационному вь1ходу соответствующего адресного накопителя, Btoрой вход - к общей для каждого столбца матрицы информационной щине, третий вход - к первому управляющему входу матрицы, информационный вход каждого адресного накопителя - к информационному выходу соответствующего ассоциативного заломинающего элемента, управляющий вход - второму управляющему входу

матрицы, а адресный вход - к адресному входу матрицы.

Такая структура матрицы позволяет выполнять операции сравнения и сложения 5 информации, находящейся в матрице, с информацией внешнего регистра компаранда, а также сравнение и сложение в каждой стро ке матрицы информации, находящейся в адресных накопителях, с информацией, нахо0 дящейся в ассоциативных запоминающих элементах (2).

Недостатком известной матрицы является то, что в ией сложно организовать выполнение операций между информацией, хранящейся в ассоциативных запоминающих

элементах двух строк. В матрице отсутствует возможность выполнения операций сдвига, а также операции умножения кодов, хранящихся в двух соседних строках. Выполнение же операции умножения массивов, храня0 щихся в строках матрицы с использованием дополнительных устройств, значительно увеличивает время выполнения данной операции, что снижает быстродействие устройства Целью изобретения является повышение быстродействия матрицы при выполнении арифметических операций и расширение функциональных возможностей ее за счет выполнения операций сдвига и выполнения операции умножения кодов, хранящихся в двух смежных строках матрицы.

д Поставленная цель достигается тем, что в ассоциативную запоминающую матрицу, содержащую ассоциативные запоминающие элементы, состоящие из триггеров, основных коммутаторов и логических блоков, причем в каждой строке матрицы первый

5 выход каждого логического блока, кроме первого, соединен с первым входом предыдущего логического блока, управляющие входы основных коммутаторов, вторые вхоаы логических блоков и первый вход первого логического блока являются одними из входов матрицы, выходами которой являются первые выходы логических блоков первого столбца и вторые -входы логических блоков первой строки матрицы, введены дополнительные коммутаторы, причем в каждой стро5 ке матрицы первый вход каждого дополнительного коммутатора, кроме последнего, подключен к второму выходу последующего логического блока, второй вход каждого дополнительного коммутатора, кроме первого, соединен с вторым выходом предыдуще го логического блока, в каждом столбце матрицы третий вход каждого дополнительного коммутатора, кроме последнего, подключен к второму выходу последующего логического блока, выход каждого дополнительного ком5 мутатора соединен с третьим входом одноименного логического блока и первым входом одноименного основного коммутатора, второй вход которого подключен к второму выходу одноименного логического блока, выход каждого осиопного коммутатора соединен с входом одноименного триггера, прямой и инверсный выходы которого подключены соответственно к четвертому и пятому входам одноименного логического блока, первые входы последних и вторые входы первых в строках матрицы дополнительных коммутаторов, третьи входы последних в столбцах матрицы дополнительных коммутаторов, управляющие входы триггеров, дополнительных коммутаторов и логических блоков являются другими входами матрицы. Кроме того, каждый логический блок содержит первый и второй полусумматоры, первый и второй элементы 2-ЗИ-2ИЛИ, элементы ИЛИ, элементы И, элемент НЕ, вход которого и первый вход первого элемента И являются одним из входов блока, выход элемента НЕ соединен с первыми входами первого и второго элементов ИЛИ, выходы которых соединены соответственно с первым и вторым входами первого элемента 2-ЗИ- 2ИЛИ, выход первого элемента 2-ЗИ- 2ИЛИ соединен с первым входом первого полусумматора, выход первого элемента И подключен к первому входу третьего элемента ИЛИ, выход которого соединен с вторым входом первого полусумматора, выход которого соединен с первым входом второго элемента 2-ЗИ-2ИЛИ н с первым входом второго полусумматора, выход второго элемента И подключен к вторым входам второго элемента 2-ЗИ-2ИЛИ и полусумматора, вторые входы элементов ИЛИ, третьи, четвертые и пятые входы элементов 2-ЗМ- 2ИЛИ, второй и третий входы первого элемента И и входы второго элемента И являются другими входами блока, выходами которого являются выходы вторых элемента 2-ЗИ--2ИЛИ и полусумматора.

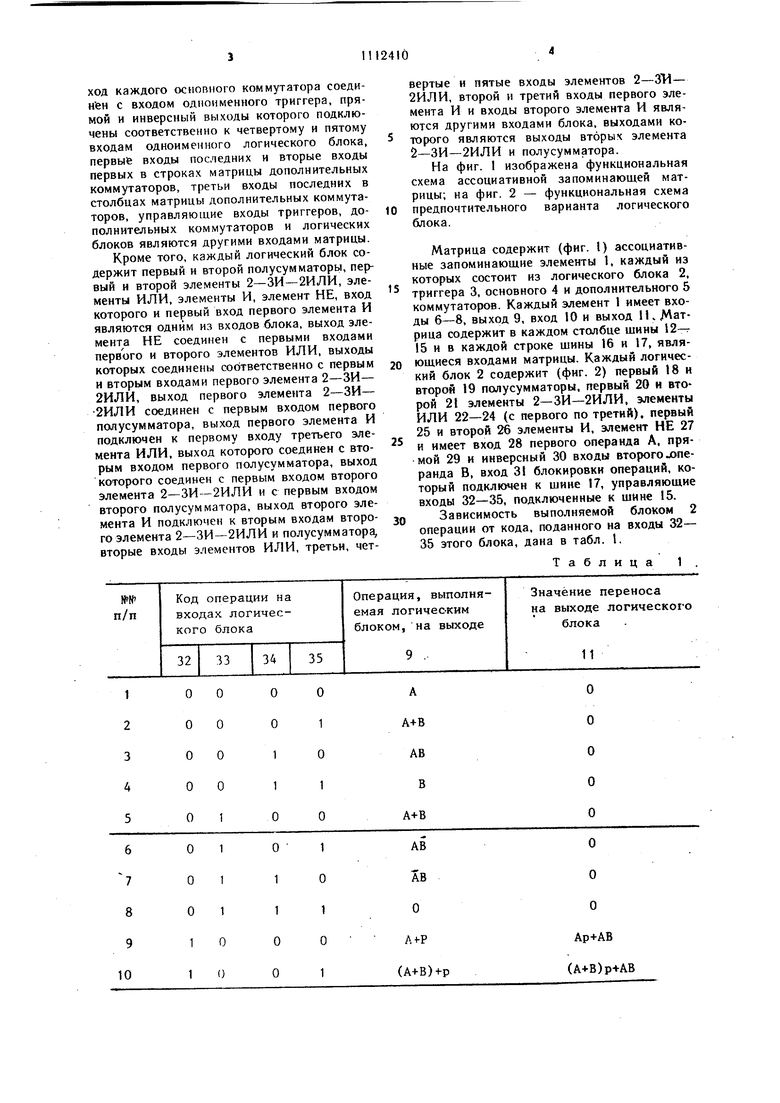

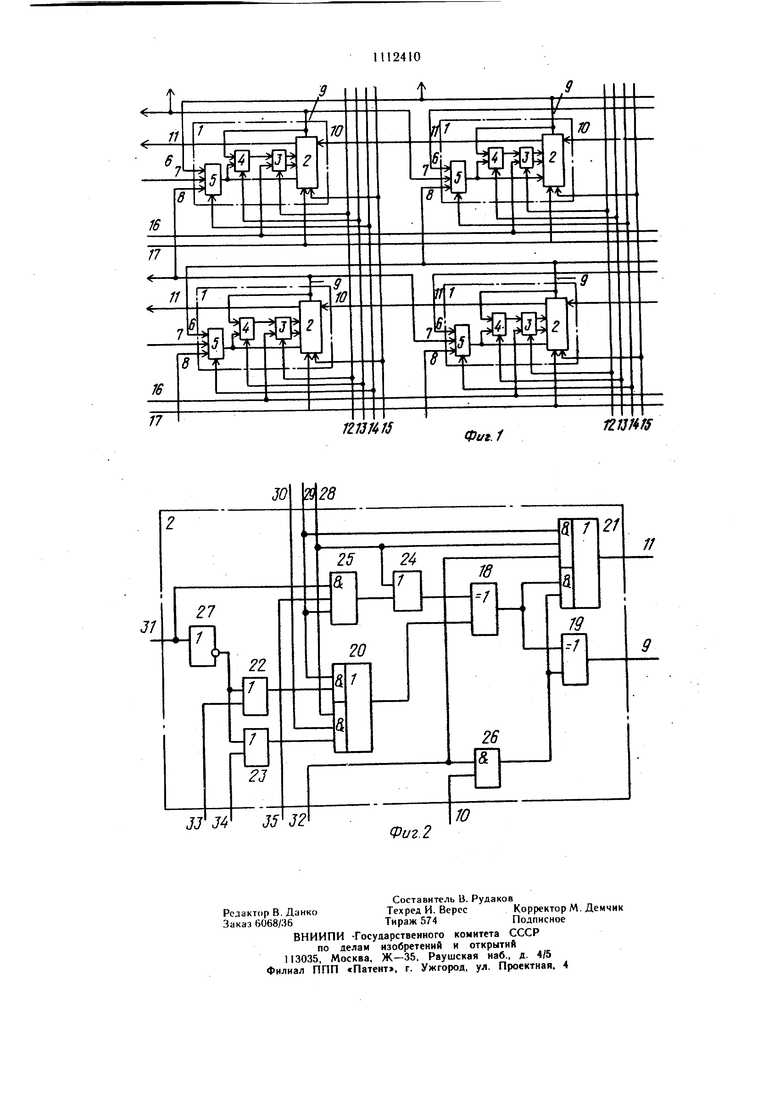

На фиг. 1 изображена функциональная схема ассоциативной запоминающей матрицы; на фиг. 2 - функциональная схема предпочтительного варианта логического блока.

Матрица содержит (фиг. I) ассоциативные запоминающие элементы 1, каждый из которых состоит из логического блока 2, триггера 3, основного 4 и дополнительного 5 коммутаторов. Каждый элемент 1 имеет входы 6-8, выход 9, вход 10 и выход iL Матрица содержит в каждом столбце шины н в каждой строке шины 16 и 17, являющиеся входами матрицы. Каждый логический блок 2 содержит (фиг. 2) первый 18 и второй 19 полусумматоры, первый 20 и второй 21 элементы 2-ЗИ-2ИЛИ, элементы ИЛИ 22-24 (с первого по третий), первый 25 и второй элементы И, элемент НЕ 27 и имеет вход 28 первого операнда А. прямой 29 и инверсный 30 входы второго операнда В, вход 3 блокировки операций, который подключен к шине 17, управляющие входы 32-35, подключенные к шине 15.

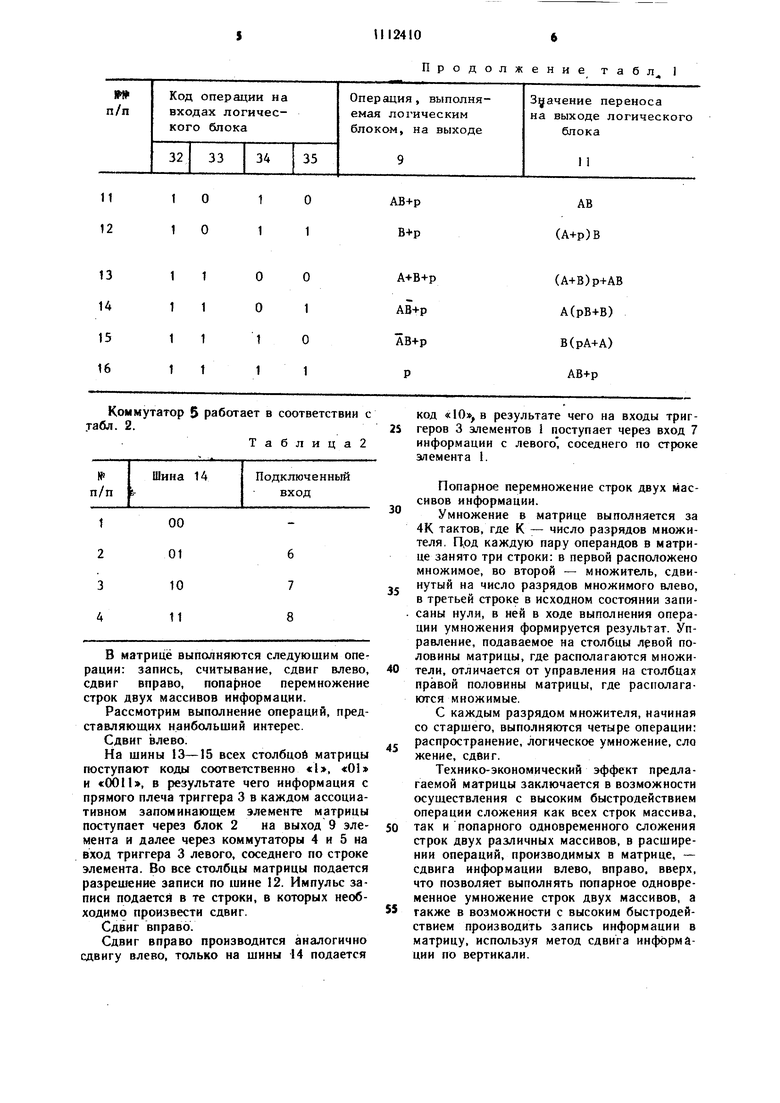

Зависимость выполняемой блоком 2 операции от кода, поданного на входы 32- 35 этого блока, дана в табл. 1.

Таблица

11 124106

Продолжение табл 1 nim mmis Фиг.1 rs

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофункциональный запоминающий элемент для логической матрицы | 1983 |

|

SU1104584A1 |

| Многофункциональный запоминающий модуль для логической матрицы | 1989 |

|

SU1642525A1 |

| Ассоциативный параллельный процессор | 1980 |

|

SU955078A1 |

| Многофункциональный элемент для логической матрицы | 1982 |

|

SU1037344A1 |

| Ассоциативная запоминающая матрица | 1980 |

|

SU920841A1 |

| Ассоциативное запоминающее устройство | 1983 |

|

SU1095237A1 |

| Ассоциативный матричный процессор | 1982 |

|

SU1164720A1 |

| Скалярный умножитель векторов | 1988 |

|

SU1619254A1 |

| Цифровой преобразователь координат | 1981 |

|

SU960834A1 |

| АССОЦИАТИВНАЯ ЗАПОМИНАЮЩАЯ МАТРИЦА | 1996 |

|

RU2107955C1 |

1. АССОЦИАТИВНАЯ ЗАПОМИНАЮЩАЯ МАТРИЦА, содержащая ассоциативные запоминающие элементы, состоящие из триггеров, основных коммутаторов и логических блоков, причем в каждой строке матрицы первый выход каждого логического блока, кроме первого, соединен с первым входом предыдущего логического блока, управляющие входы основных коммутаторов, вторые входы логических блоков и первый вход первого логического блока являются одними из входов матрицы, выходами которой являются первые выходы логических блоков первого столбца и вторые входы логических блоков первой строки матрицы, отличающаяся тем, что, с целью повыщения быстродействия матрицы при выполнении арифметических операций и расширения функциональных возможностей ее за счет выполнения операций сдвига и выполнения операции умножения кодов, хранящихся в двух смежных строках матрицы, в нее введены дополнительные коммутаторы, при чем в каждой строке матрицы первый вход каждого дополнительного коммутатора, кроме последнего, подключен к второму выходу последующего логического блока, второй вход каждого дополнительного коммутатора, кроме первого, соединен с вторым выходом предыдущего логического блока, в столбце матрицы третий вход каждого дополнительного коммутатора, ,крол1е послед не го, под ключей к второму выходу последующего логического блока, выход каждого дополнительного коммутатора соединен с третьим входом одноименного логического блока и первым входом одноименного основного коммутатора, второй вход которого подключен к второму выходу одноименного логического блока, выход каждого основного коммутатора соединен с входом одноименного триггера, прямой н инверсный выходы которого подключены соответственно к четвертому и пятому входам одноименного логического блока, первые входы последних и вторые входы первых в строках матрицы дополнительных коммутаторов, третьи входы последних в столбцах матрицы дополнительных коммутаторов, управляющие входы триггеров, дополнительных коммутаторов и логических блоков являются другими входами матрицы. 2. Матрица по п. I, отличающаяся тем, что каждый логический блок содержит первый и второй полусумматоры, первый и второй элементы 2-ЗИ-2ИЛИ, элементы ИЛИ, элементы И, элемент НЕ, вход которого и первый вход первого элемента И являются одним из входов блока, выход элемента НЕ соединен с первыми входами первого и второго элементов ИЛИ, выходы которых соединены соответственно с первым и вторым входами первого элемента 2-ЗИ- SD 2ИЛИ, выход первого элемента 2-ЗИ- nU 2ИЛИ соединен с первым входом первого полусумматора, выход первого элемента И подключен к первому входу третьего элемента ИЛИ, выход которого соединен с вторым входом первого полусумматора, выход которого соединен с первым входом второго элемента 2-ЗИ-2ИЛИ и с первым входом второго полусумматора, выход второго эле мента И подключен к вторым входам второго элемента 2-ЗИ-2ИЛИ и полусумматора, вторые входы элементов ИЛИ, третьи, четвер гые и пятые входы элементов 2-ЗИ- 2ИЛИ, второй и третий входы первого элемента И и входы второго элемента И являются другими входами блока, выходами которого являются выходы вторых элемента 2-ЗИ-2ИЛИ и полусумматора.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США № 3735312, кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| опублнк | |||

| Приспособление для склейки фанер в стыках | 1924 |

|

SU1973A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР № 760188, кл | |||

| Прибор для нагревания перетягиваемых бандажей подвижного состава | 1917 |

|

SU15A1 |

Авторы

Даты

1984-09-07—Публикация

1982-10-14—Подача