Изобретение относится к вычислитель ной технике и может быть использовано в матричных ассоциативно-логических устройствах.

Известен элемент для логических

и ассоциативных матриц, содержащий триггер, схему сравнения, элементы И, ИЛИ и НЕ tip .

В матрицах, построенных из таких элементов, ряд операций поиска выпол- няется за одну микрокоманду, однако арифметические операции осуществляются затруднительно с помощью микропрограмм, требующих значительных затрат 1времени.,

Наиболее близким техническим реще- нием к изобретению является элемент для ассоциативно-логической матрицы, , содержащий элемент ИЛИ,триггер синхровкод которого соединен с выходом первого элемента И, а первый вход элемента И подключен к шине записи, второй эле- , мент И, первый вход которого соединен с единичным выходом триггера, а второй - к шине опроса, элемент 2-2И-ИЛИ первый и третий входы которого соединены с инверсным и прямым выходами триггера, а второй и четвертый входы подключены к второму и первому разрядам кода шины операции, мультиплексор, управляющие входы которого подключены к первому и второму разрядам кода шины настройки, а первый и второй входы мултиплексора соединены с соответствующим шинами входного числа .

Недостатком этого элемента является ограниченное быстродействие, так как арифметические операции (сложение, вычитание, умножение) в матрице, пост роенной из этих элементов, вьшолняются за несколько микрокоманд программы. .

Целью изобретения является поЁьш1ени быстродействия (многофункционального) .элемента для логической матрицы при выполненнии арифметических операций.

Поставленная цель достигается тем, что в многоф пнкциональный элемент для логической матрицы, содержащий первые элементы И, ИЛИ и 2И-ИЛИ, второй элемент И, первый мультиплексор и тригг«р, первый вход которого подключен к выходу первого элемента И, выходы сое; динены с одним из входом первохч элемента , причем один из выходов триггера подключен к первому входу вто рого элемента И, второй вход которого, входы первого элемента И и первого мул типдексора и другие входы первого элемента 2И-ИЛИ являются одними из входов многофункционального элемента, введены второй и третий мультиплексоры, второй элемент 2И-ИЛИ, второй и третий элементы ИЛИ, элемент .НЕРАВНОЗНАЧНОСТЬ, третий, четвертый и пятый элементы И, причем один из входов зторого элемента 2И-ИЛИ подключены соответственно к выходам триггера и выходу первого мультиплексора, первый вход первого элемента ИЛИ соединен с выходом второго элемента И, вторые входы первого элемента ИЛИ и триггера подключены к выходу, первого мультиплексора, выходы второго элемента 2И-ИЛИ соединены с первыми вхо -дами. третьего- элемента И и второго элемента ИЛИ, второй вход которого подключен к выходу четвертого элемента И, выход второго мультиплексора соединен -с первыми входами четвертого и пятого элементов И и третьего муль- типлексора, второй вход которого подключен к выходу второго элемента ИЛИ, входы третьего элемента ИЛИ соединены с выходами первого мул1зттплексора и первого элемента 2И-ИЛИ, а выход под- .ключен к вторым входам. третьего и че вертого элементов И, выход пятого элемента И подключен к одному из входов элемента НЕРАВНОЗНАЧНОСТЬ, другой вход которого соединен с .выходом третьего элемента И, входы второго мультиплексора, другие входы второго элемента 2И-ИЛИ, объединенные второй вход пятого элемента И и третий вход третьего мультиплексора являются другими входами многофункционального элемента, выходами которого являются выходы первого элемента ИЛИ, элемента НЕРАВНОЗНАЧНОСТЬ и третьего

мультиплексора.

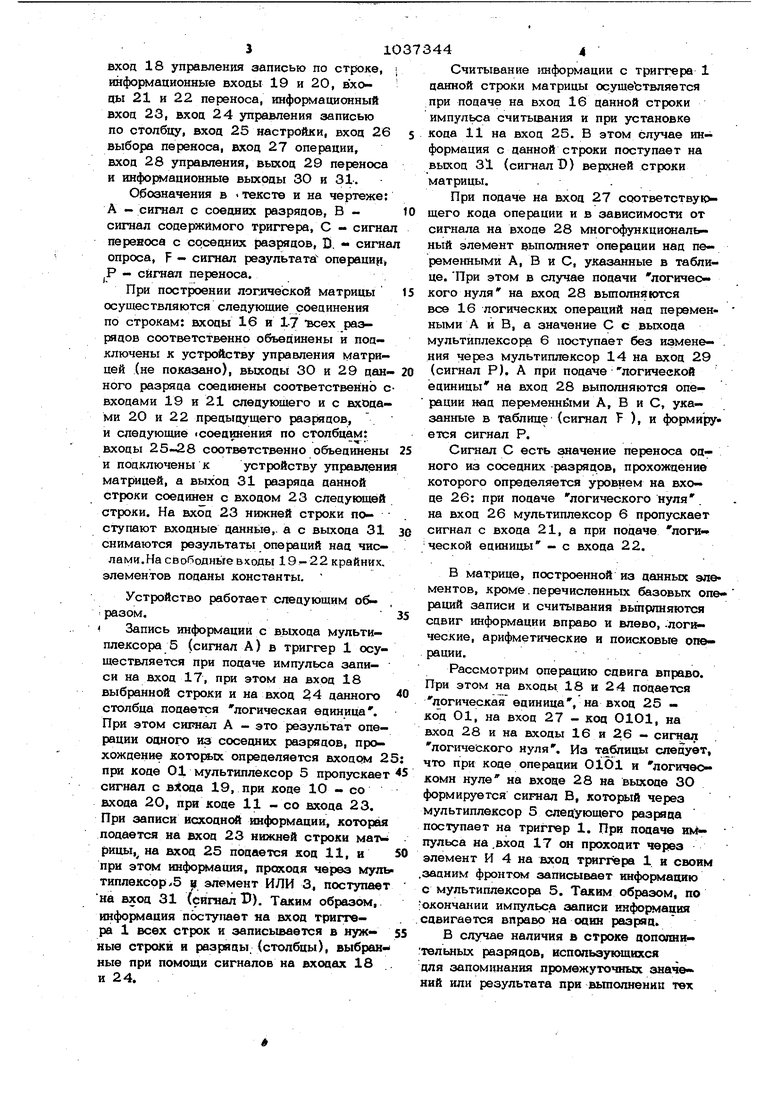

На чертеже показана структурная -CXQма многофункционального элемента для логической матрицы.

Многофункциональный элемент для логической матрицы содержит триггер 1, , первый элемент И 2, первый элемент ИЛИ 3, второй элемент И 4, пёрнБЫй 5 и второй 6 мультиплексоры, перм вый 7 и второй 8 элементы 2И-ИЛИ, второй элемент ИЛИ 9, третий 10 и четвертый 11 элементы И, третий элемент ИЛИ 12, пятый элемент И 13, третий мультиплексор 14 и элемент НЕ- РАВНОЗНАЧНОСТЬ 15. МногофункциональньШ элемент для логической матрищй имеет вход 16 опроса, вхоа 17 записи.

вход 18 управления записью по строке, информационные входы 19 и 20, вхопы 21 и 22 переноса, информационный вхоц 23, вход 24 управления записью по столбцу, вход 25 настройки, вхоц 26 выбора переноса, вход 27 операции, вход 28 управления, выход 29 переноса и информационные выходы ЗО и 31.

Обозначения в тексте и на чертеже: А - сигнал с соедних разрядов, В сигнал содержимого триггера, С - сигнал переноса с соседних разрядов, D. - сигна опроса, F - сигнал результата опараци, Р - сигнал переноса.

При построении логлческой матрицы осуществляются следующие соединения по строкам: входы 16 и 1-7 всех разрядов соответственно объединены и подключены к устройству управления матрицей (не показано), выходы 30 и 29 данного разряда соединены соответственно свходами 19 и 21 следующего и с входами 20 н 22 предыду щего разрядов, и следующие «соединения по столбцам; входы соответственно объединены и подключены к устройству управлени матрицей, а выход 31 разряда данной строки соединен с входом 23 следующей строки. На вход 23 нижней строки поступают входные данные,, а с въкода 31 снимаются результаты операций над числами.На свободные в ходы 19 - 22 крайних, элементов поданы константы.

Устройство работает следующим об разом.

Запись информации с вьисода мультиплексора 5 (сигнал А) в триггер 1 осуществляется при подаче импульса записи на вход 17, при этом на вход 18 выбранной строки и на вход 24 данного столбца подается логическая единица . При этом сигнал А - это результат операции одного из соседних разрядов, прохождение которых определяется входсчи 2 при коде 01 мультиплексор 5 пропускает сигнал с входа 19, при коде 10 - со входа 2О, при коде 11 - со входа 23. При записи исходной информации, которая подается на вход 23 нижней строки мат рицы, на вход 25 подается код 11, и при этом информация, проходя через мультиплексор/5 IJ элемент ИЛИ 3, поступает на вход 31 (сигнал Т). Таким образом, инфо1Ж1ация поступает яа вход триггера 1 всех строк и записьюается в нуж- ныв строки и разряды, (столбцы), выбранные при помощи сигналов на входах 18 и 24.

Считывание 1шформации с триггера 1 данной строки матрицы осушеЬтвляется при подаче на вход 16 данной строки импульса считьшания и при установке кода 11 на вход 25. В этом случае информация с данной строки поступает на выход 31 (сигнал D) верхней строки матрицы..

При подаче на вход 27 соответствующего кода операции и в зависимости от сигнала на входе 28 многофункционален ный элемент выполняет операции над переменными А, В и С, указанные в таблице. При этом в случае подачи логического нуля на вход 28 вьшолняются все 16 логических операций над переменными А и В, а значение С с въгхода мультиплексора 6 поступает без измене- ния через мультиплексор 14 на вход 29 (сигнал Р). А при подаче логической единицы на вход 28 выполняются one- рации над переменными А, В и С, ука- заннъге в таблице (сигнал F ), и формируется сигнал Р.

Сигнал С есть значение переноса одного из соседних разрядов, прохождение которого определяется уровнем на входе 26: при подаче логического нуля . на вход 26 мультиплексор 6 пропускает сигнал с входа 21, а при подаче логической единицы - с входа 22.

В матрице, построенной из данных элментов, кроме.перечисленнъсс базовъпс on раций записи и считывания выпрлняются сдвиг информации вправо и влево, -логические, арифметические и поисковые one- рации.

Рассмотрим операцию сдвига вправо. При этом на входы 18 и 24 подается логическая единица, на вход 25 - кбд 01, на вход 27 - код О1О1, на вход 28 и на входы 16 и 26 - сигнал логического нуля. Из таблицъ следует, что при коде операции 0101 и логическомн нуле на входе 28 на выходе ЗО формируется сигнал В, который через мультиплексор 5 следующего разряда поступает на триггер 1. При подаче m/t пульса на .вход 17 он проходит через элемент И 4 на вход триггера 1 и своим .задним фронтом записывает информацию с мультиплексора 5. Таким образом, по окончании импульса записи информация сдвигается вправо на один разряд.

В случае наличия в строке допопнительных разрядов, использующихся для запоминания промежуточных значе- НИИ или результата при вьшолнении тех или иных операций, при вьтолиении операции сдвига на эти разряды - столбцы подается код операции 0000 и на вход 24 - уровень логического нуля . Поисковую операцию paccMOTpiiVi на примере сравнения на равенство двух чисел. При этом пары разрядов этих чисел располагают в одной строке, допустим старшими разрядами слева. При этом необходимо иметь дополнительный многофункциональный элемент матрицы на каждую пару разрядов чисел для фиксации промежуточного результата. Оаера ция сравнения осуществляется за две микрокоманды. В первой микрокоманде находим пары разрядов с кодами ОО и 11. При этом столбец, содержащий одно число, имеет следующие управляющие сигналы: вход 2 код 0101 (число с триггера), вход 28 и входы 16-18, 24-26 - логический нуль. Второй столбец, содержащий разряд второго числа, имеет следующие управляющие сигналы: вход 25 - код 01 вход 27 - код ОНО (свертка по моду- лю два), вход и входы 16-18, 24, 26 - логический ноль. Третий столбец содержащий дополнительный разряд, имеет следующие управляющие сигналы: вхо ды 18 и 24 - логическая единица, вход 25 - код 01, входы 16, 26 и 28 логический ноль, вход 27 - код ОООО При подаче по входу 17 импульса происходит фиксация в дополнительный разряд результата поразрядкой свертки по модулю два двух чисел. Вторая микрокоманда заключается в распространении, начиная от крайнего слева, сигнала поразрядного совпадения по всей строке. Крайний слева дополнительный разряд имеет следующие управляющие сигналы: вход 27 - код О1О1, вход 28 и входы , 24-26 -/логический ноль Столбцы, содержащие разряды сравнивае мых чисел, имеют следующие управлякяц сигналы: вход 25 - код О1, вход 27 код ОООО, вход 28 и входы 16-18, 24 26 - логический ноль. А столбцы, содержащие результат псфазряаного сравнения (дополнительные разряды, кроме крайнего слева) имеют следующие управляющие сигналы: вход 25 - код О1 вход 27 - код 0100, вход 28 и входы 16-18, 24 и 26 - логический ноль При этом сравниваемые числа равны в случае наличия логической единицы на выходе 30 (сигнал ) крайнего cnpaiui элемента строки. Аналогично происходит операция сравнения массива чисел с константой, подаваемой на вход 23 нижней строки матрицы, операция также занимает две микрокоманды: сравнение по модулю два одноименных разрядов с фиксацией результата в дополнительный разряд и распространение сигнала совпадения по строке. Из арифметических операций рассмотрим операцию сложения двух чисел. При этом пары одноименных разрядов этих чисел располагаются в одной строке, допустим старшим разрядом слева. При сложении чисел необходимо иметь дополнительный многофункциональный элемент матрицы на каждый разряд чисел цля фиксации результата. Операция арифметического сложения осуществляется за одну микрокоманду. При этом столбец, соде{ жащий разряд одного числа, имеет следующие управляющие сигналы; вход 26 логический ноль, вход 27 -код О1О1, вход 28 и входы 16-18, 24 к 25 логический ноль. Столбец, содержащий разряд второго числа имеет .следующие управляющие сигналы: вход 25 - код О1, вход 26 - логический ноль, вход 27 код 1001, вход 28 - логическая единица, входы 16-18 и 24 - логический ноль. На выходе 30 данного столбца формируется результат суммы данных разрядов двух чисел, а на вьгходе 29 перенос на следующий разряд. Столбец, предназначенный для фиксации; результата арифметического сложения, имеет следующие управляющие сигналы: входы 18 и 24 - логическая единица, вход 25 - код 01, вход 26 - логический ноль, вход 27 - код 110О, вход 28 логический ноль. При подаче на вход 17 импульса записи результат арифметического сложения фиксируется в дополни тельных разрядах данной строки. Технико-экономический эффект предложенного многофункционального элемента заключается в повьпиении быстродействия арифметических, а также логических и некоторых поисковых операций в матрице, построенной из таккх. элементов. Как было показано ранее для операции арифметического сложения двух чисел в известном устройстве необходимо семь микрокоманд, а в предложенном объекте эта операция осуществляется за одну микрокоманду.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофункциональный запоминающий элемент для логической матрицы | 1983 |

|

SU1104584A1 |

| Многофункциональный запоминающий модуль для логической матрицы | 1989 |

|

SU1642525A1 |

| Элемент ассоциативной памяти | 1980 |

|

SU875460A1 |

| АССОЦИАТИВНЫЙ ПРОЦЕССОР | 1988 |

|

SU1521118A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| ЯЧЕЙКА ОДНОРОДНОЙ СТРУКТУРЫ | 2005 |

|

RU2300800C1 |

| Вероятностная вычислительная машина | 1986 |

|

SU1455344A1 |

| Устройство для определения координат объекта | 1990 |

|

SU1814196A1 |

| Устройство для формирования тестов | 1987 |

|

SU1429121A1 |

| Микропрограммное вычислительное устройство | 1984 |

|

SU1229761A1 |

МНОГОФУНКЦИОНАЛЬНЫЙ ЭЛЕМЕНТ ДЛЯ ЛОГИЧЕСКОЙ МАТРИЦЫ, содер1жаший первые элементы И, ИЛИ, и 2И-ИЛИ, в торойэлемент И, первый мультиплексор и триггер, первый вход которого подключен к выходу первого элемента И, выходы соединены с одними из входов первого элемента 2И-ИЛИ, причем один из выходов триггера подключен к первому входу второго элемента И, второй вход которого, входы первого элемента И и первого мультиплексора и другие первого элемента являются одними из входов многофункционального элемента, отличающийся тем, что, с целью повышения быстродействия многофункционального элемента при выполнении ари етических операций, в него введены второй и третий мультиплексоры, второй элемент 2И-ИЛИ, второй и третий элементы ИЛИ, элемент НЕРАВНСХ. ЗНАЧНОСТЬ, третий, четвертый и пятый элементы И, причем одни из входов второго элемента 2И-ИЛИ подключены соответственно к выходам триггера и выходу первого мультиплексора, первый вход первого элемента ИЛИ соединен с выходом второго элемента И, вторые входы первого элемента ИЛИ и триггера подключены к выходу первого мультиплексора, выходы второго элемента 2И- ИЛИ соединены с первыми входами третьего элемента И и второго элемента ИЛИ, второй вход которого подключен к выходу четвертого элемента И, выход второго мультиплексора соединен с первыми входами четвертого и пятого элементов И и третьего мультиплексора, СП второй вход которого подключен к выходу второго элемента ИЛИ, входы третьего элемента ИЛИ соединены с выходами первого мультиплексора и первого элемента 2И., а выхоп подключен к .вторым входам третьего и четвертого элементов И, выход пятого элемента И подключен к. одному из входов элемента НЕРАВНОЗНАЧНОСТЬ, другой вход со которого соединен с выходом третьего . sj элемента И, входы второго мультиплекDO 4; ik сора, другие входы второго элемента 2ИИЛИ, объединенные второй вход пятого элемента И и третий вход третьего мультиплексора являются другими входами многофункционального элемента, выходами которого .являются выходы первого элемента ИЛИ, элемента НЕРАВНОЗНАЧНОСТЬ и третьего мультиплексора.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Запоминающий модуль для матричных блоков памяти | 1978 |

|

SU746728A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Под ред | |||

| И | |||

| В | |||

| Прангишвили | |||

| М., Советское радио, 1973, с | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1983-08-23—Публикация

1982-04-09—Подача