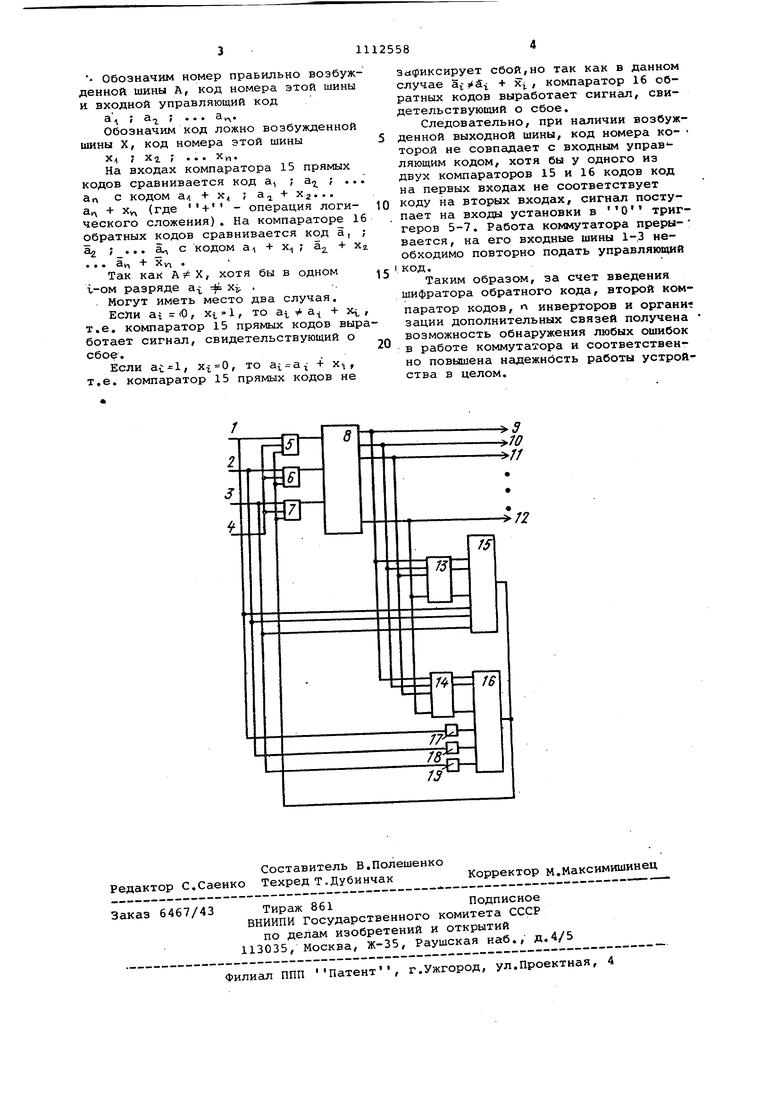

Изобретение относится к импульс,ной технике и может быть использова но в различных устройствах автомати ки и вычислительной техники. Известен коммутатор, содержащий счетчик тактовых импульсов и блок антисовпадений С1, Недостатком этого устройства является низкая надежность. Наиболее близким к изобретению по технической сущности является коммутатор, содержащий дешифратор, компаратор кодов, шифратор прямого кода, п триггеров, входы которых соединены соответственно с входными и тактовыми шинами коммутатора, а в ходы - с соответствующими входами д шифратора, выходы которого подключе ны к соответствующим выходным шинам коммутатора и входам шифратора прям го кода, выходы которого соединены первыми входами компаратора кодов, вторые входы которого соединены с соответствующими входными шинами ко мутатора, а выход - с входами установки в О триггеров С23. Недостатком известного устройств является невысокая надежность работ обусловленная невозможностью обнару жения ложных коммутирующих потенциа лов, возбужденных на выходных шинах код номера которых частично повторя ет код номера правильно возбужденно выходной шины. Цель изобретения - повышение надежности коммутатора. Поставленная цель достигается тем, что в коммутатор с обнаружением ошибок, содержащий дешифратор, первый компаратор кодов, шифратор прямого кода и л триггеров, входы которых соединены соответственно с входными и тактовой шинами компаратора, а выходы - с соответствующими входами дешифратора, выходы которого подключены к соответствующим выходным шинам коммутатора и входам шифратора прямого кода, выходы кото рого соединены с первыми входами компаратора кодов, вторые входы которого соединены с соответствующими входными шинами коммутатора, а выход - с входами установки в О триггеров, введены шифратор обратно го кода , л инверторов и второй компаратор кодов, первые входы которого соединены с соответствующими выходами шифратора обратного кода, а вторые входы - с выходами соответст вующих инверторов, входы которых по ключены к соответствующим входным шинам коммутатора, причем выход вто рого компаратора кодов подключен к входам установки в О триггеров, а входы шифратора обратного кода соединены с соответствующими выхода ми дешифратора. На чертеже представлена функциональная схема коммутатора с обнаружением ошибок для трехразрядного входного кода С 3) . Устройство содержит входные шины 1-3, тактовую шину 4, триггеры 5-7, дешифратор 8, выходные шины 9-12, шифраторы 13 и 14 соответственно прямого и обратного кодов, компараторы 15 и 16 кодов, инверторы 17-19. Входные шины 1-3 компаратора соединены с соответствующими входами триггеров 5-7, вторыми входами первого компаратора 15 кодов и через инверторы 17т 19 - с вторЕлми входами второго компаратора 16 кодов. Выходы компараторов 15 и 16 кодов подключены к входам установки в триггеров 5-7, тактовые входы которых соедине-, ны с тактовой шиной 4, а выходы - с соответствующими входами дешифратора 8, выходы которого подключены к соответствующим выходным шинам 9-12 компаратора и входам шифраторов 13 и 14 прямого и обратного кодов, выходы которых подключены к первым входам соответствующих компараторов 15 и 16 кодов. Коммутатор работает следующим образом. В случае правильного функционирования коммутатора при поступлении управляющего а разрядного двоичного кода на входные шины 1-3 и тактового сигнала на шину 4 управляющий сигнал с выходов триггеров 5-7 проходит на входы дешифратора 8, при этом на одной из выходных шин 9-12. появляется коммутирующий потенциал. Он поступает на один из входов шифратора 13 прямого кода и шифратора 14 обратного кода. На выходе шифратора 13 прямого кода появляется код, соответстветствующий управляющему коду на входных шинах 1-3, поэтому на первых и вторых входах первого компаратора 15 кодов присутствуют одинаковые коды. На выходе шифратора 14 обратного кода появляется код, обратный относительно присутствующего на входных шинах 1-3 компаратора. Этот код поступает на первые входы компаратора 16 кодов, на вторые входы которого поступает код с входных шин 1-3, прошедший через инверторы 17-19. Таким образом, на первых и вторых входах второго компаратора 16 кодов присутствуют одинаковые коды. На выходе компараторов 15 и 16 сигнал установки в О триггеров 5-7 не появляется и работа коммутатора не прерывается. В случае появления коммутирующего отенциала, кроме шины, код номера оторой совпадает с входным управлящим кодом еще на одной шине, устройтво работает следующим образом. Обозначим номер правильно возбуж денной шины А, код номера этой шины и входной управляющий код а 7. а. Обозначим код ложно возбужденной шины X, код номера этой шины -1 t 7. I Хц« На входах компаратора 15 прямых кодов сравнивается код а, ; а ; . arv с кодом а;( + X. ; а,, + х,... + х« (где - операция логического сложения). На компараторе 1 обратных кодов сравнивается код а, Ig ; ... а, с кодом а + х ; а. + х . . avi х . Так как А 5 X, хотя бы в одном i-OM разряде а- х- , . Могут иметь место два случая. Если ai 0, xt - 1, то а Ф а-1 + т.е. компаратор 15 прямых кодов выр ботает сигнал, свидетельствующий о сбое. Если ас 1, , то ai, a + х, т.е. компаратор 15 прямых кодов не Зафиксирует сбой,но так как в данном случае + Xj , компаратор 16 обратных кодов выработает сигнал, свидетельствующий о сбое. Следовательно, при наличии возбужденной выходной шины, код номера которой не совпадает с входным управ ляющим кодом, хотя бы у одного из двух компараторов 15 и 16 кодов код на первых входах не соответствует коду на вторых входах, сигнал поступает на входы установки в О триггеров 5-7. Работа коммутатора преры- вается, на его входные шины 1-3 необходимо повторно подать управляющий код. Таким образом, за счет введения шифратора обратного кода, второй компаратор кодов, « инверторов и органн зации дополнительных связей получена возможность обнаружения любых ошибок в работе коммутатора и соответственно повышена надежнбсть работы устройства в целом.

| название | год | авторы | номер документа |

|---|---|---|---|

| Шифратор | 1980 |

|

SU920835A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1990 |

|

SU1702380A1 |

| Преобразователь угла поворота вала в код | 1991 |

|

SU1833966A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1478330A1 |

| Устройство для приема команд телеуправления | 1987 |

|

SU1441436A1 |

| Шифратор | 1980 |

|

SU886048A2 |

| Способ цикловой синхронизации с динамической адресацией получателя | 2016 |

|

RU2621181C1 |

| Устройство для формирования последовательностей импульсов | 1989 |

|

SU1653140A1 |

| Аналого-цифровой преобразователь напряжения в код системы остаточных классов | 1990 |

|

SU1732470A1 |

| Устройство для кодирования и декодирования дискретной информации | 1983 |

|

SU1159166A1 |

КОММУТАТОР С ОБНАРУЖЕНИЕМ ОШИБОК, содержащий дешифратор, первый компаратор кодов, шифратор прямого кода и п триггеров, входа которых соединены соответственно с входными и тактовой шинами коммутатора, а выходы - с соответствующими входами дешифратора, выходы которого подключены к соответствующим выходным шинам коммутатора и входс м шифратора прямого кода, выходы которого соединены с первыми входами компаратора кодов, вторые входыкоторого соединены с соответствующими входными шинами коммутатора, а выход - с входами установки в О триггеров, отличающийся- тем, что, с целью повьлления надежности в работе, в него введены шифратор обратного кода, г инверторов и второй компаратор кодов, первые входы которого соединены с соответствующими выходами шифратора обратного кода, а вторые входы - с выходами соответствующих инверторов, входы которых подключены к соответствующим входным шинам коммутатора, причем выход второго компа-. ратора кодов подключен к входг1М уста- g новки в О триггеров, а входы шиф-; ратора обратного кода соединены с соответствующими выходами дешифратора.

//

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1984-09-07—Публикация

1983-01-06—Подача